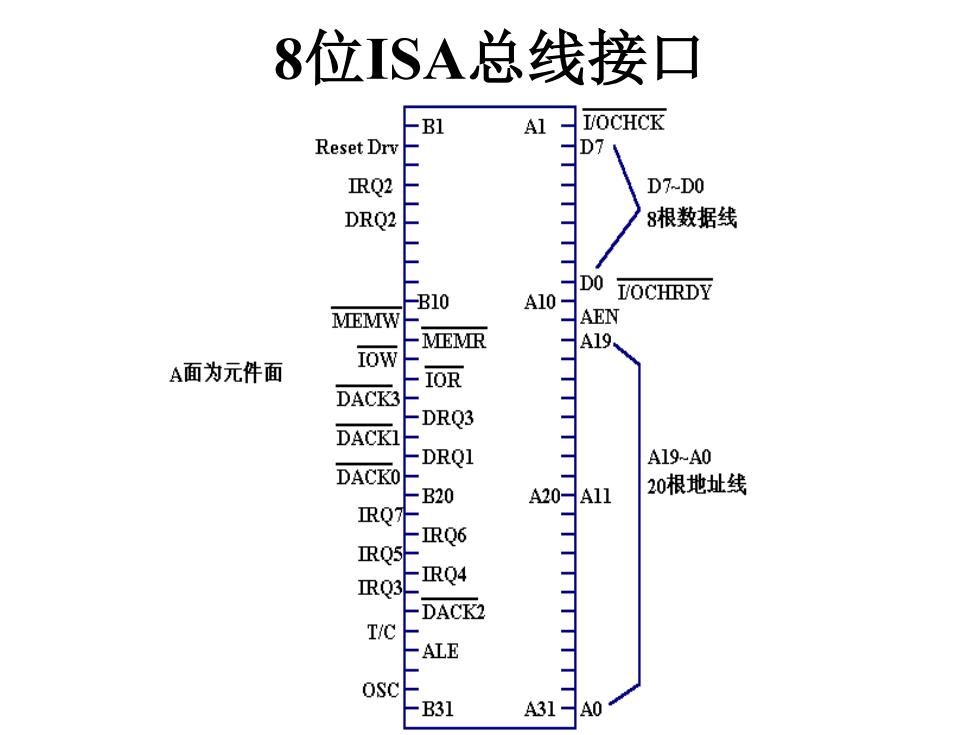

8位ISA总线接口 -B1 Al IOCHCK Reset Drv D7 IRQ2 D7-DO DRQ2 8根数据线 YOCHRD -B10 A10- MEMW AEN -MEMR A19, A面为元件面 IoW IOR DACK3 -DRQ3 DACKI -DRQ1 A19-A0 DACKO -B20 A20A11 20根地址线 IRQT -IRQ6 IRQ5 IRQ3 -IRQ4 -DACK2 T/C -ALE osc B31 A31A0

8位ISA总线接口

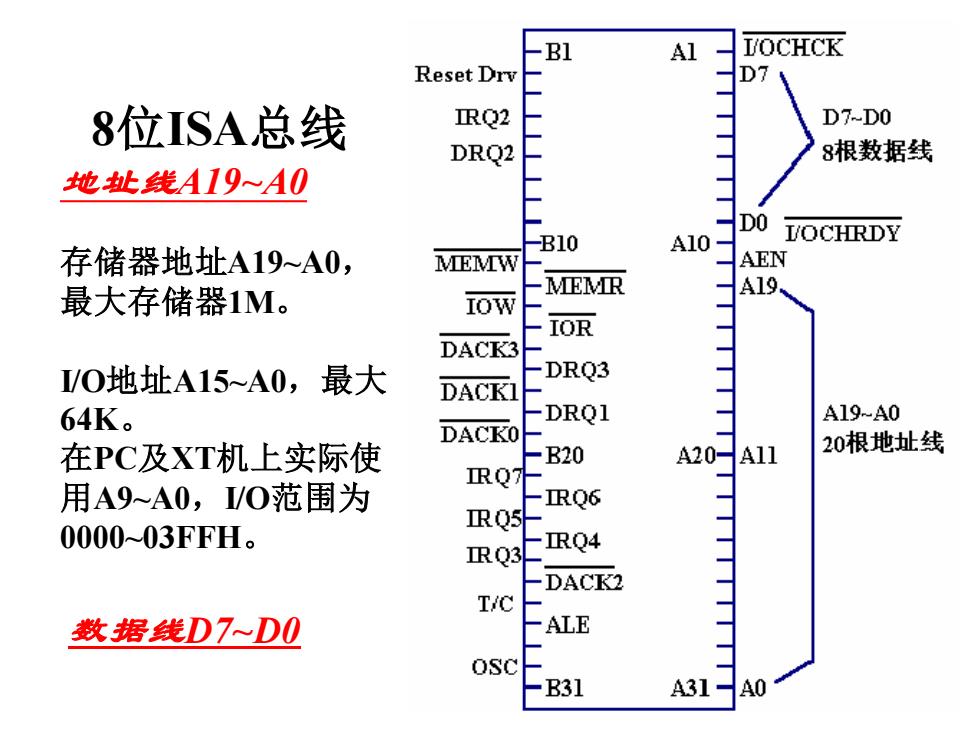

-B1 Al IOCHCK Reset Drv D7 8位ISA总线 IRQ2 D7-D0 DRQ2 8根数据线 地址线A19~A0 D0 -B10 A10- IOCHRDY 存储器地址A19~A0, MEMW AEN 最大存储器1M。 MEMR A19 IoW IOR DACK3 I/O地址A15~A0,最大 -DRQ3 DACKI 64K. -DRQ1 A19-A0 DACKO 在PC及XT机上实际使 -B20 A20A11 20根地址线 IRQ7 用A9~A0,/O范围为 -IRQ6 0000~03FFH。 RQ5 IRQ3 IRQ4 -DACK2 T/C 数据线D7~D0 -ALE -B31 A31- A0

地址线A19~A0 存储器地址A19~A0, 最大存储器1M。 I/O地址A15~A0,最大 64K。 在PC及XT机上实际使 用A9~A0,I/O范围为 0000~03FFH。 8位ISA总线 数据线D7~D0

8位ISA总线 IOCHCK Reset Drv D7 IRQ2 D7-D0 控制线21杂 DRQ2 8根数据线 AEN:Address Enable, -B10 A10 IOCHRDY 地址允许信号 MEMW AEN MEMR IoW PC总线可由CPU或DMA IOR DACK3 控制器控制,当DMAC控 -DRQ3 DACKI 制总线时,8237产生AEN -DRQ1 A19-A0 DACKO 信号,用于禁止CPU控制 -B20 A20A11 20根地址线 IRQ7 总线。即: -IRQ6 IRQ5 AEN=O,表示CPU控制总线 IRQ3 -IRQ4 -DACK2 AEN=1,表示DMA控制器控制,总线 T/C -ALE -B31 A31 A0

8位ISA总线 控制线 21条 AEN:Address Enable, 地址允许信号 PC总线可由CPU或DMA 控制器控制,当DMAC控 制总线时,8237产生AEN 信号,用于禁止CPU控制 总线。即:

-B1 Al IOCHCK Reset Drv D7 8位ISA总线 IRQ2 D7-D0 DRQ2 8根数据线 ALE:Address Latch D03 -B10 A10- OCHRDY AEN Enable,地址锁存允许 IEMW MEMR 入 A19 IOW IOR 在ALE的下降沿锁存来 DACK3 DRQ3 自CPU的地址信号 DACKI -DRQ1 A19-A0 DACKO -B20 A20A11 20根地址线 读/写信号 IRQ7 -IRQ6 IOR IOW IRQ5 IRQ3 IRQ4 MEMW -DACK2 MEMR T/C ∈ALE -B31 A31- A0

8位ISA总线 ALE:Address Latch Enable,地址锁存允许 在ALE的下降沿锁存来 自CPU的地址信号 读/写信号

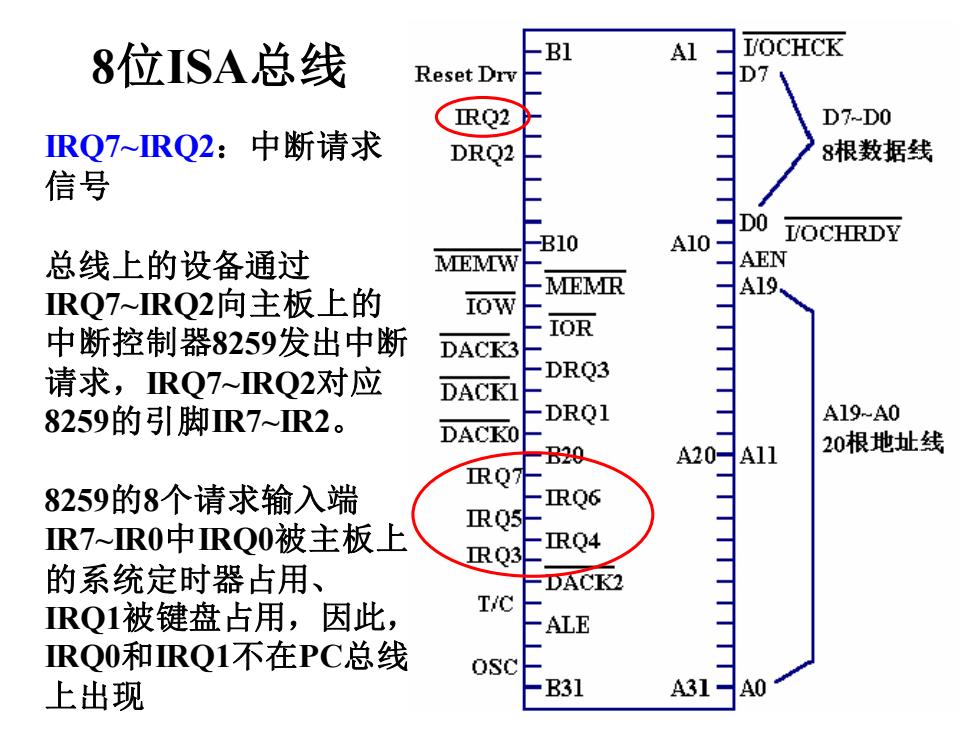

8位ISA总线 IOCHCK Reset Drv D7 IRQ2 D7-D0 RQ7~RQ2:中断请求 DRQ2 8根数据线 信号 -B10 A10- DO IOCHRDY 总线上的设备通过 MEMW AEN MEMR RQ7~RQ2向主板上的 A19 IoW 中断控制器8259发出中断 IOR DACK3 请求,RQ7~RQ2对应 -DRQ3 DACKI 8259的引脚R7~R2。 DRQ1 A19-A0 DACKO B20 A20A11 20根地址线 IRQ7 8259的8个请求输入端 -IRQ6 IRQ5 R7~R0中RQ0被主板上 -IRQ4 IRQ3 的系统定时器占用、 -DACK2 RQ1被键盘占用,因此, T/C -ALE RQ0和RQ1不在PC总线 上出现 -B31 A31A0

8位ISA总线 IRQ7~IRQ2:中断请求 信号 总线上的设备通过 IRQ7~IRQ2向主板上的 中断控制器8259发出中断 请求,IRQ7~IRQ2对应 8259的引脚IR7~IR2。 8259的8个请求输入端 IR7~IR0中IRQ0被主板上 的系统定时器占用、 IRQ1被键盘占用,因此, IRQ0和IRQ1不在PC总线 上出现