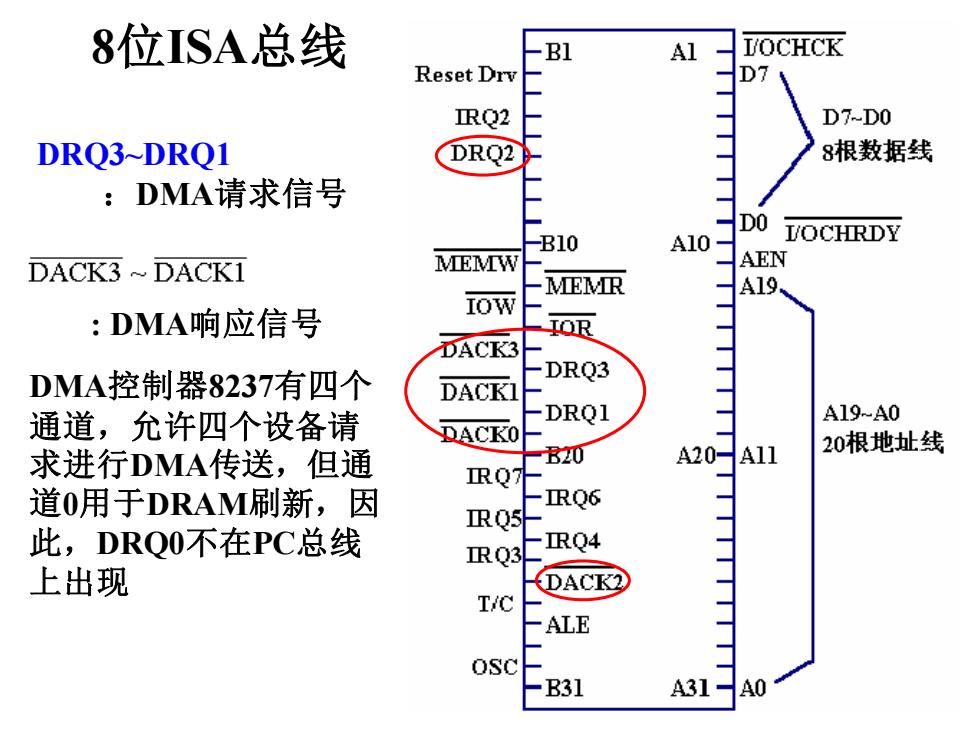

8位ISA总线 -B1 IOCHCK Reset Drv D7 IRQ2 D7-D0 DRQ3~DRQ1 DRQ2 8根数据线 :DMA请求信号 -B10 A10- IOCHRDY DACK3 DACK1 MEMW AEN MEMR 入 A19 IOW :DMA响应信号 IOR DACK3 DMA控制器8237有四个 -DRQ3 DACKI 通道,允许四个设备请 DRQ1 A19-A0 -B20 A20A11 20根地址线 求进行DMA传送,但通 IRQ7 道0用于DRAM刷新,因 -IRQ6 IRQ5 此,DRQ0不在PC总线 IRQ3 IRQ4 上出现 ①ACK② T/C -ALE -B31 A31- A0

8位ISA总线 DRQ3~DRQ1 :DMA请求信号 DMA控制器8237有四个 通道,允许四个设备请 求进行DMA传送,但通 道0用于DRAM刷新,因 此,DRQ0不在PC总线 上出现 : DMA响应信号

8位ISA总线 T/C:计数结束信号 一次DMA请求可传送多个字节,当任一DMA通道传送 结束时,T/C上出现高电平。 Reset Drv:系统总清信号 /O CHCK I/O通道奇偶校验信号。当/O通道上的设 备或存储器的奇偶校验有错时,该信号有效。 VO CHRDY I/O通道准备好信号。该信号为低电平时 (未准备好),使CPU或DMA插入等待周期

8位ISA总线 T/C:计数结束信号 一次DMA请求可传送多个字节,当任一DMA通道传送 结束时,T/C上出现高电平。 Reset Drv:系统总清信号 I/O通道奇偶校验信号。当I/O通道上的设 备或存储器的奇偶校验有错时,该信号有效。 I/O通道准备好信号。该信号为低电平时 (未准备好),使CPU或DMA插入等待周期

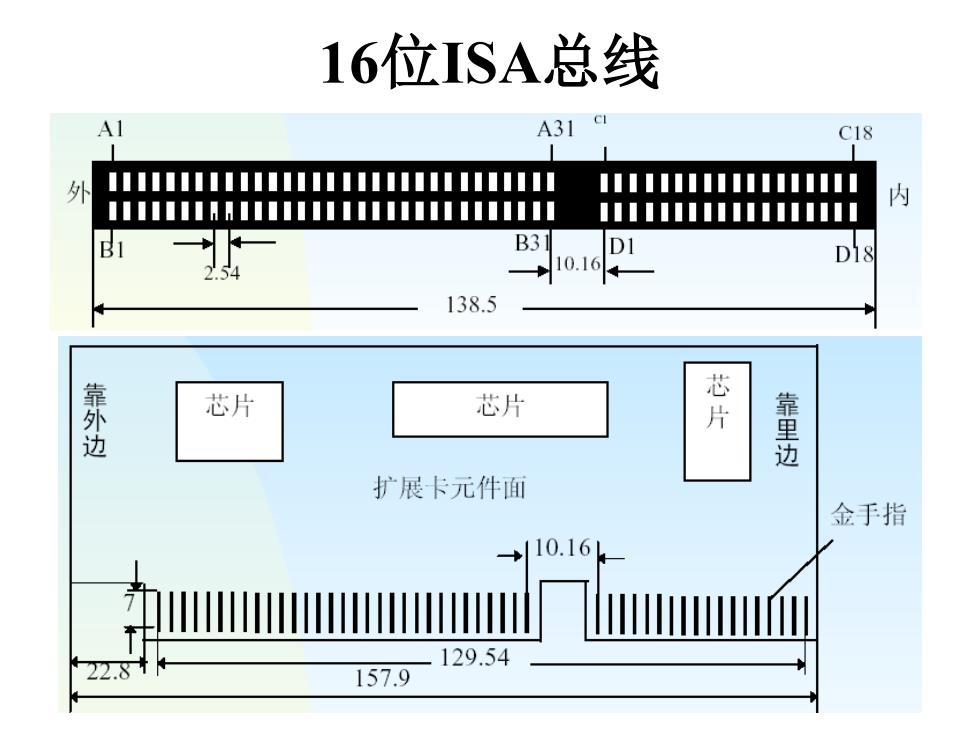

16位ISA总线 Al A31 C18 外 100000000000100010100101011111 000000000000000001 内 JIIIOIIKKIILIIIII00000111101110 B B31 DI 10.16 D18 138.5 靠外边 芯片 芯片 芯 靠里边 扩展卡元件面 金手指 10.16 129.54 157.9

16位ISA总线

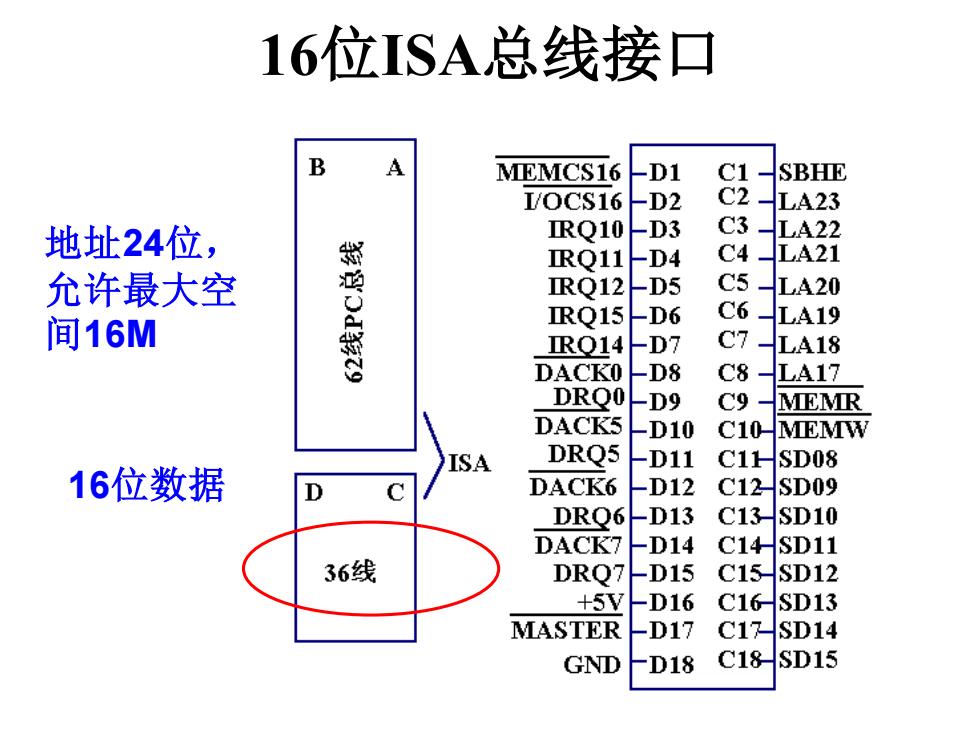

16位ISA总线接口 A MEMCS16 D1 C1 SBHE I/OCS16 D2 LA23 地址24位, IRQ10 C3 LA22 IRQ11 D4 C4 LA21 允许最大空 IRQ12 C5 HLA20 间16M IRQ15 -D6 C6LA19 IRQ14 D7 C7LA18 DACKO -D8 C8-LA17 DRQO D9 C9-MEMR DACK5 -D10 C10-MEMW ISA DRQ5 D11 C1上HSD08 16位数据 DACK6 -D12 C12SD09 DRO6 D13 C13SD10 DACK7 -D14 C14SD11 36线 DRQ7 D15 C15SD12 +5V -D16 C16SD13 MASTER -D17 C17SD14 GND D18 C18 SD15

16位ISA总线接口 地址24位, 允许最大空 间16M 16位数据

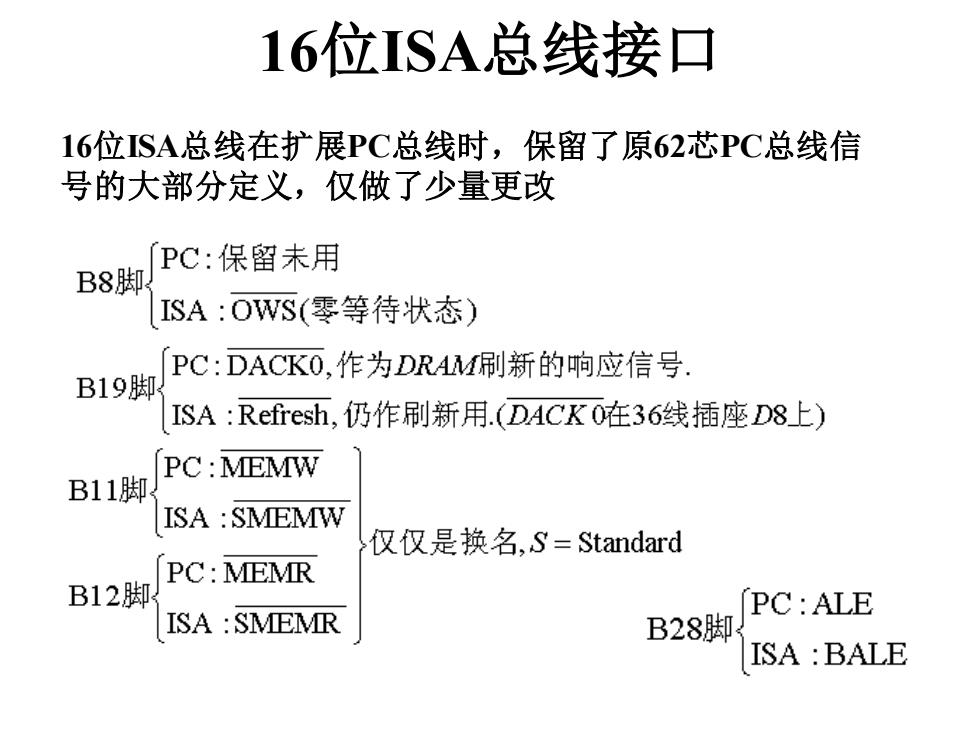

16位ISA总线接口 16位ISA总线在扩展PC总线时,保留了原62芯PC总线信 号的大部分定义,仅做了少量更改 PC:保留未用 B8脚 ISA:OWS(零等待状态) PC:DACKO,作为DRAM刷新的响应信号 B19脚 ISA:Refresh,仍作刷新用.(DACK0在36线插座D8上) PC:MEMW B11脚 ISA SMEMW 仅仅是换名,S=Standard PC:MEMR B12脚 ISA SMEMR PC:ALE B28脚 ISA:BALE

16位ISA总线在扩展PC总线时,保留了原62芯PC总线信 号的大部分定义,仅做了少量更改 16位ISA总线接口