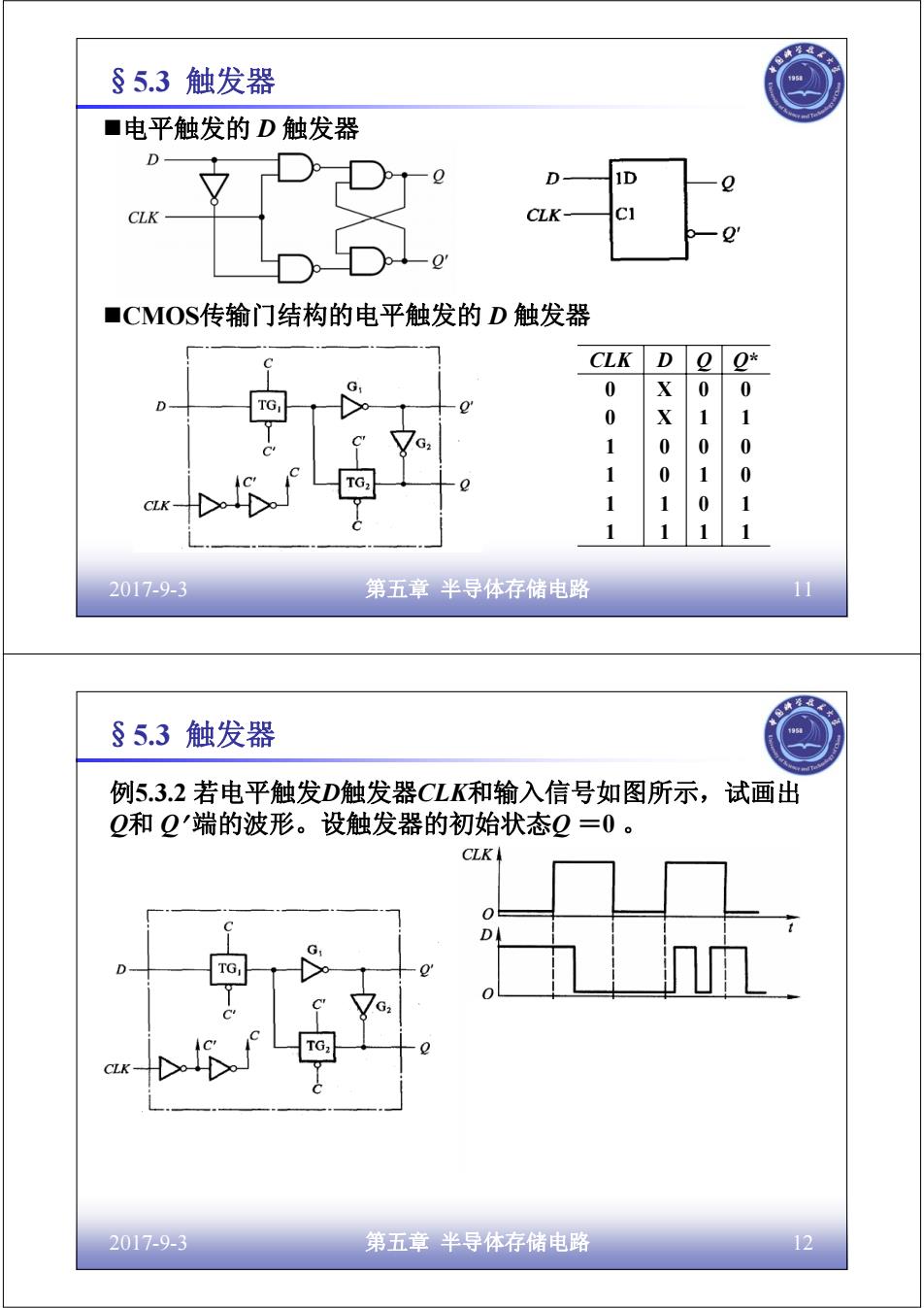

§5.3 触发器 ■电平触发的D触发器 CLK CK- ■CMOS传输门结构的电平触发的D触发器 CLK D Q O* 0 X 0 0 0 X 1 1 1 0 0 0 TG, 1 0 1 0 CLK 1 1 0 1 1 1 2017-9-3 第五章半导体存储电路 §5.3 触发器 例5.3.2若电平触发D触发器CLK和输入信号如图所示,试画出 Q和Q'端的波形。设触发器的初始状态Q=0。 CLK 0 D TG: CLK 2017-9-3 第五章半导体存储电路 12

2017-9-3 第五章 半导体存储电路 11 电平触发的 D 触发器 1 1 1 1 1 1 0 1 1 0 1 0 1 0 0 0 0 X 1 1 0 X 0 0 CLK D Q Q* CMOS传输门结构的电平触发的 D 触发器 §5.3 触发器 2017-9-3 第五章 半导体存储电路 12 例5.3.2 若电平触发D触发器CLK和输入信号如图所示,试画出 Q和 Q′ 端的波形。设触发器的初始状态Q =0 。 0 §5.3 触发器

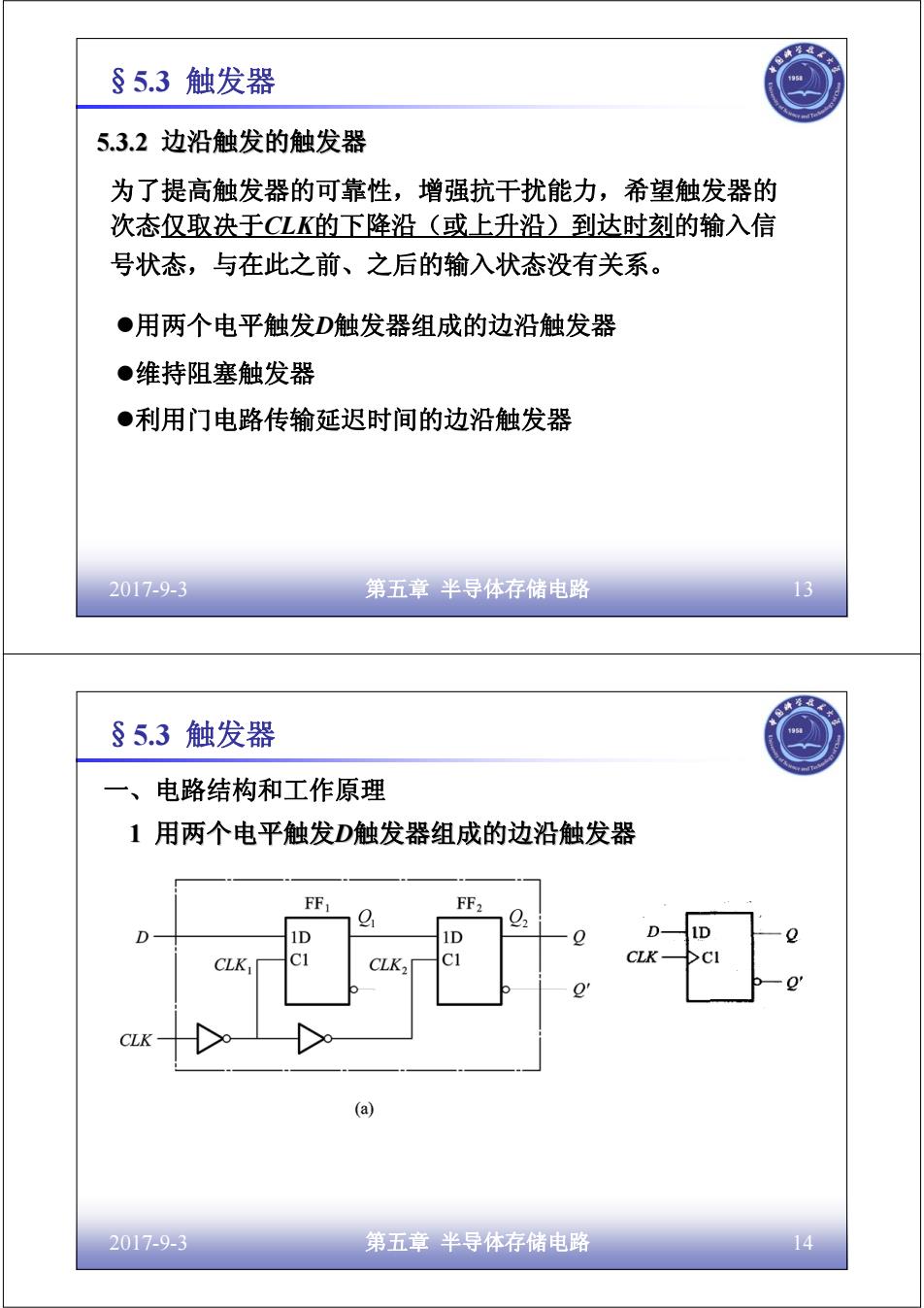

§5.3 触发器 5.3.2边沿触发的触发器 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的 次态仅取决于CLK的下隆沿(或上升沿)到达时刻的输入信 号状态,与在此之前、之后的输入状态没有关系。 ●用两个电平触发D触发器组成的边沿触发器 ●维持阻塞触发器 ●利用门电路传输延迟时间的边沿触发器 2017-9-3 第五章半导体存储电路 §5.3 触发器 一、电路结构和工作原理 1用两个电平触发D触发器组成的边沿触发器 FF, FF2 0 1D 1D ID CLK. CLK2 CLK- >C1 CLK (a) 2017-9-3 第五章半导体存储电路 14

2017-9-3 第五章 半导体存储电路 13 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的 次态仅取决于CLK的下降沿(或上升沿)到达时刻的输入信 号状态,与在此之前、之后的输入状态没有关系。 z用两个电平触发D触发器组成的边沿触发器 z维持阻塞触发器 z利用门电路传输延迟时间的边沿触发器 §5.3 触发器 5.3.2 边沿触发的触发器 2017-9-3 第五章 半导体存储电路 14 1 用两个电平触发D触发器组成的边沿触发器 一、电路结构和工作原理 Q1 1 Q1 2 §5.3 触发器

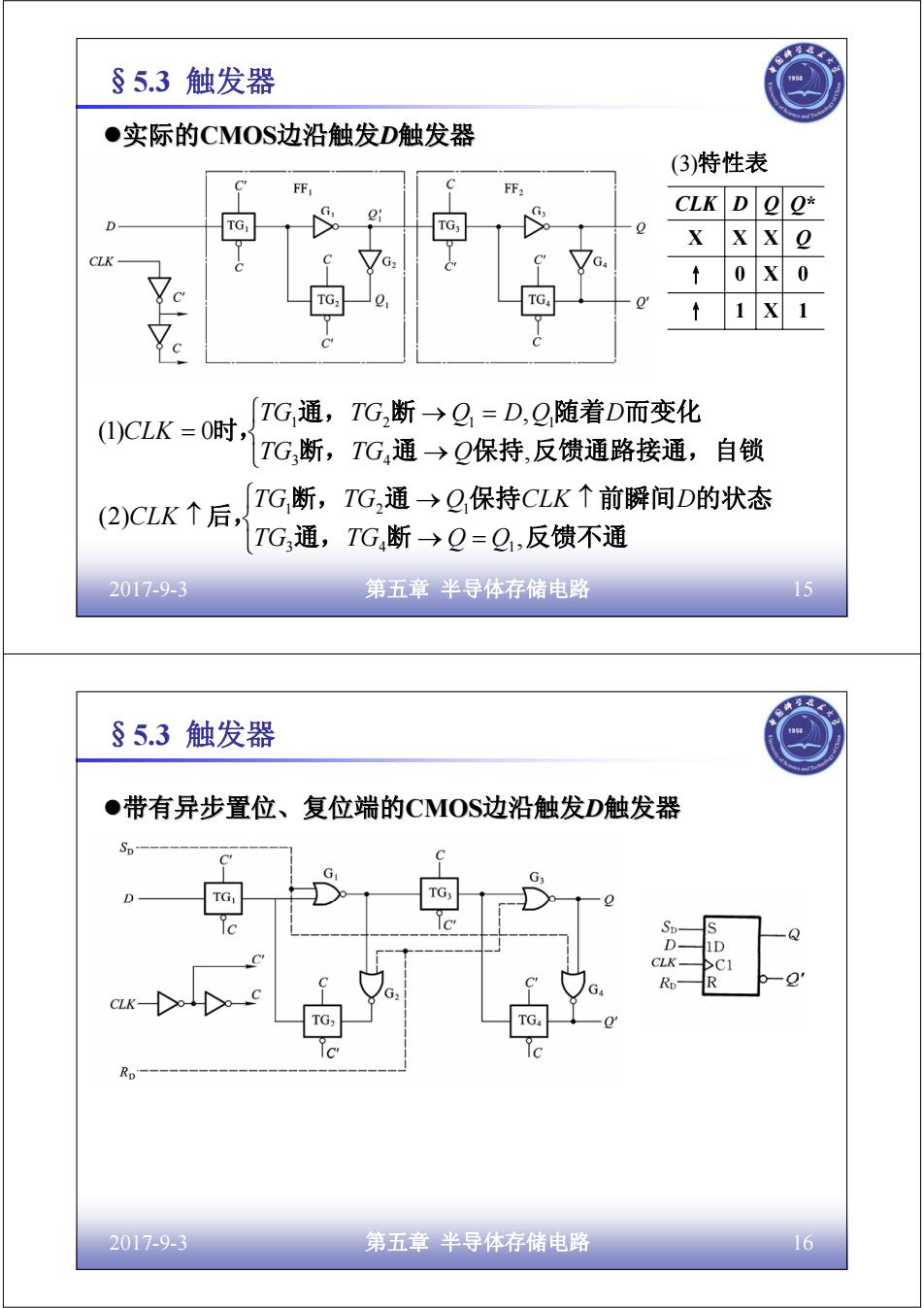

§5.3 触发器 ●实际的CMOS边沿触发D触发器 (3)特性表 FF FF, 2' CLK D O O* D TG Q X CLK 7G2 G 0 0 G TG. (1)CLK=0时, TG通,TG,断→9,=D,9随着D而变化 TG,断,TG,通→Q保持,反馈通路接通,自锁 (2)CLK个后, TG,断,TG,通→Q保持CLK个前瞬间D的状态 TG,通,TG,断→Q=Q,反馈不通 2017-9-3 第五章半导体存储电路 15 §5.3 触发器 ●带有异步置位、复位端的CMOS边沿触发D触发器 Sp G G SD- D 1D CLK- c1 Rp- R CLK- R 2017-9-3 第五章半导体存储电路 16

2017-9-3 第五章 半导体存储电路 15 ⎩ ⎨ ⎧ → → = = 断, 通 保持 反馈通路接通,自锁 通, 断 随着 而变化 时, , , (1) 0 3 4 1 2 1 1 TG TG Q TG TG Q D Q D CLK ⎩ ⎨ ⎧ → = → ↑ ↑ 通, 断 反馈不通 断, 通 保持 前瞬间 的状态 后, , (2) 3 4 1 1 2 1 TG TG Q Q TG TG Q CLK D CLK (3)特性表 ↑ 1 X 1 ↑ 0 X 0 X X X Q CLK D Q Q* z实际的CMOS边沿触发D触发器 §5.3 触发器 2017-9-3 第五章 半导体存储电路 16 z带有异步置位、复位端的CMOS边沿触发D触发器 §5.3 触发器

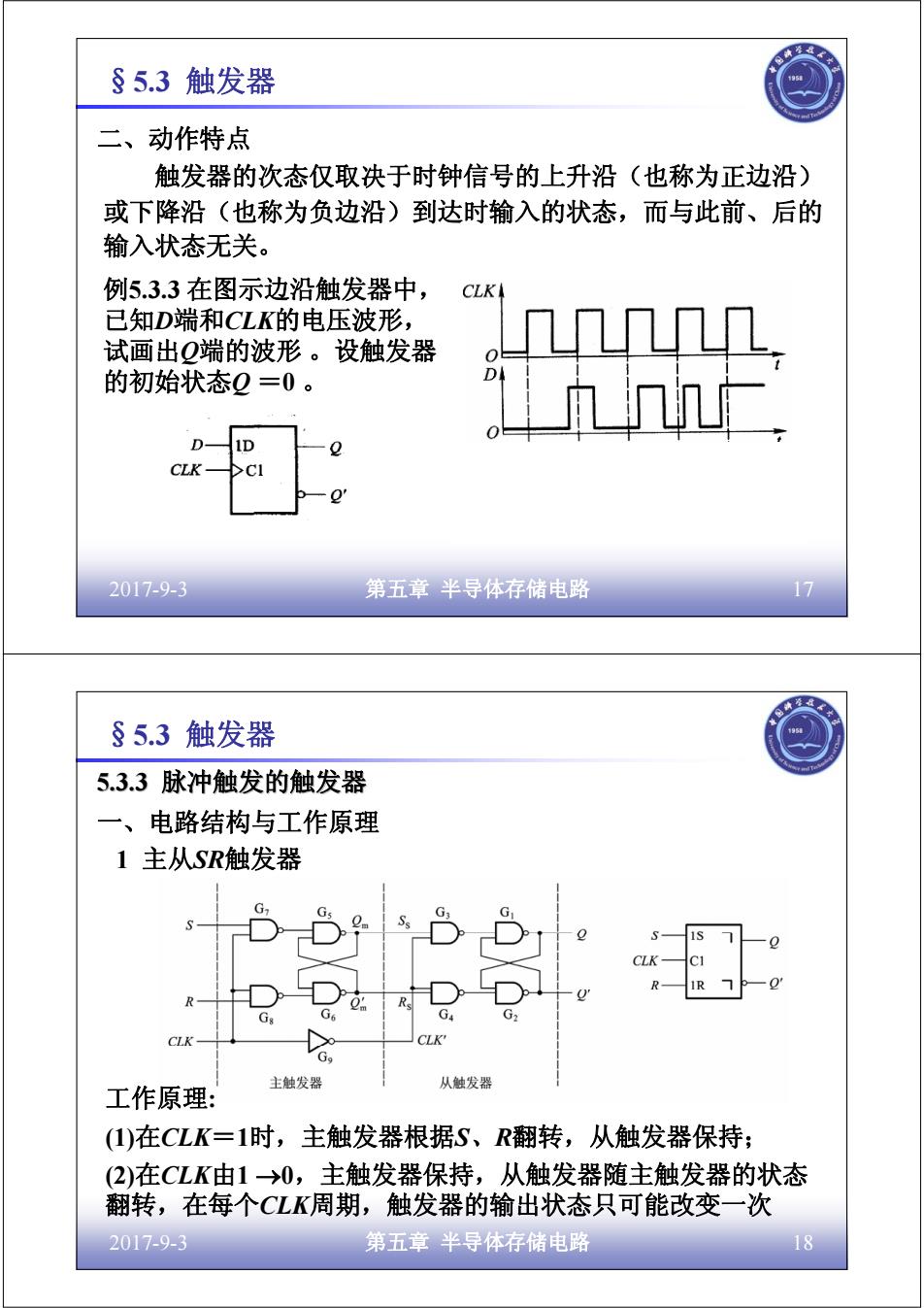

§5.3 触发器 二、动作特点 触发器的次态仅取决于时钟信号的上升沿(也称为正边沿) 或下降沿(也称为负边沿)到达时输入的状态,而与此前、后的 输入状态无关。 例5.3.3在图示边沿触发器中, CLK 已知D端和CLK的电压波形, 试画出Q端的波形。设触发器 的初始状态Q=0。 D CLK 2017-9-3 第五章半导体存储电路 §5.3 触发器 19 5.3.3脉冲触发的触发器 一、电路结构与工作原理 1主从SR触发器 1S CLK- R IR 9 G G CLK 0 CLK' Go 主触发器 从触发器 工作原理: (1)在CLK=1时,主触发器根据S、R翻转,从触发器保持; (2)在CLK由1→0,主触发器保持,从触发器随主触发器的状态 翻转,在每个CLK周期,触发器的输出状态只可能改变一次 2017-9-3 第五章半导体存储电路 18

2017-9-3 第五章 半导体存储电路 17 二、动作特点 触发器的次态仅取决于时钟信号的上升沿(也称为正边沿) 或下降沿(也称为负边沿)到达时输入的状态,而与此前、后的 输入状态无关。 例5.3.3 在图示边沿触发器中, 已知D端和CLK的电压波形, 试画出Q端的波形 。设触发器 的初始状态Q =0 。 0 §5.3 触发器 2017-9-3 第五章 半导体存储电路 18 一、电路结构与工作原理 1 主从SR触发器 工作原理: (1)在CLK=1时,主触发器根据S、R翻转,从触发器保持; (2)在CLK由1 →0,主触发器保持,从触发器随主触发器的状态 翻转,在每个CLK周期,触发器的输出状态只可能改变一次 §5.3 触发器 5.3.3 脉冲触发的触发器

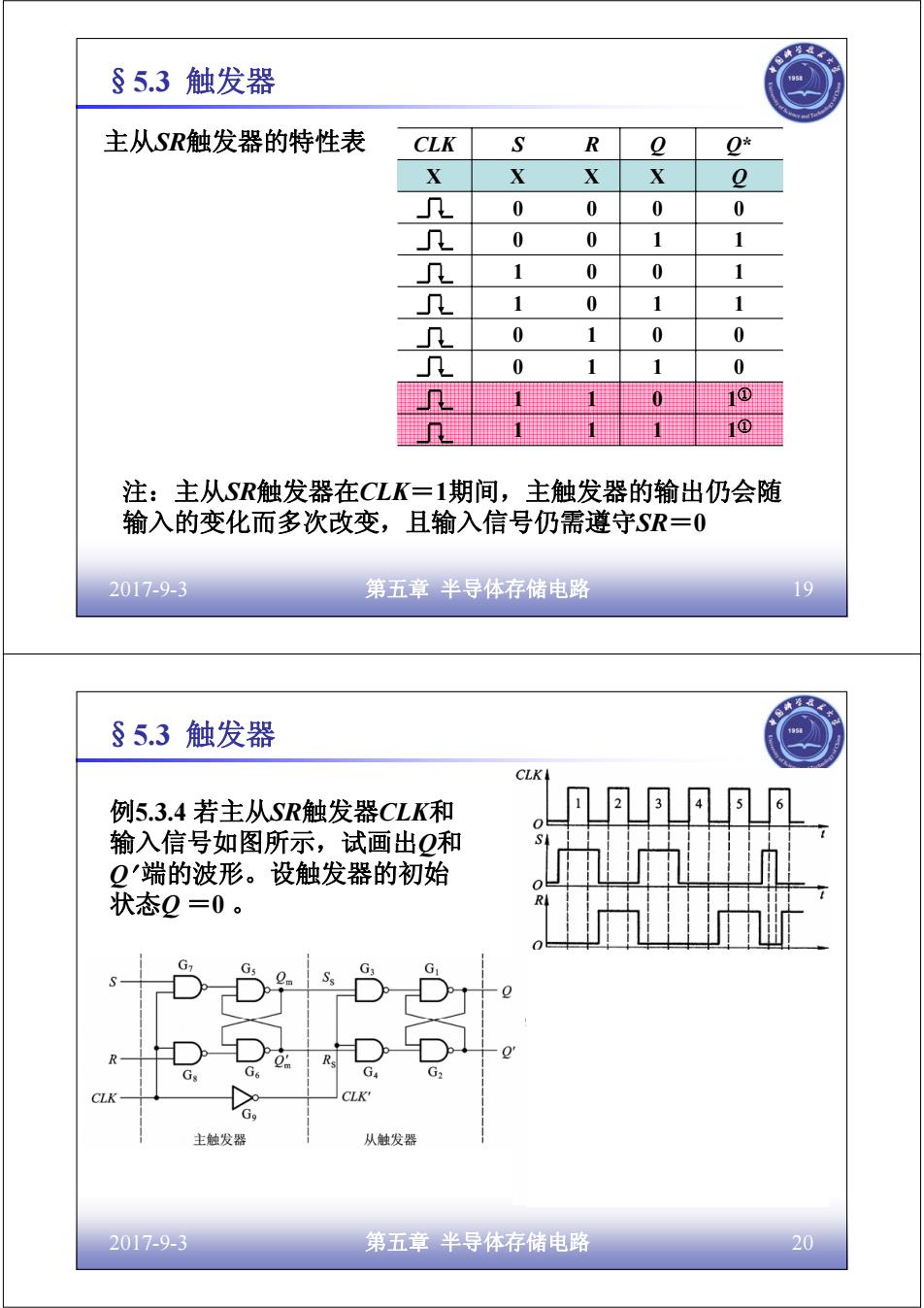

§5.3 触发器 主从SR触发器的特性表 CLK S R 2 O* X X X X 2 几 0 0 0 0 几 0 0 1 1 几 1 0 0 几 1 0 1 1 0 0 0 几 0 1 0 10 注:主从SR触发器在CLK=1期间,主触发器的输出仍会随 输入的变化而多次改变,且输入信号仍需遵守SR=0 2017-9-3 第五章半导体存储电路 19 §5.3 触发器 CLK 例5.3.4若主从SR触发器CLK和 2 45☐6 输入信号如图所示,试画出Q和 Q'端的波形。设触发器的初始 状态2=0。 G G CLK Go 主触发器 从触发器 2017-9-3 第五章半导体存储电路 20

2017-9-3 第五章 半导体存储电路 19 1 1 0 1① 1 1 1 1① 0 1 1 0 0 1 0 0 1 0 1 1 1 0 0 1 0 0 1 1 0 0 0 0 X X X X Q 主从SR触发器的特性表 CLK S R Q Q* 注:主从SR触发器在CLK=1期间,主触发器的输出仍会随 输入的变化而多次改变,且输入信号仍需遵守SR=0 §5.3 触发器 2017-9-3 第五章 半导体存储电路 20 例5.3.4 若主从SR触发器CLK和 输入信号如图所示,试画出Q和 Q′ 端的波形。设触发器的初始 状态Q =0 。 0 §5.3 触发器