实验二Nexys3实验板及设计软件 实验二Nexys3实验板及设计软件 A1.1实验简介 Nexys3实验板专门由linx大学合作计划(UP)为各种层次的大学工科培养计划设计, 由美国Digilent公司(www.digilentinc.com)制作。因IsE软件版本不同,读者所用软件的菜 单排列与名称可能与本实验介绍的略有不同,但其功能基本相同。读者可以参考本实验提供 的软件使用细节。 A1.2实验目的 熟悉Nexys3实验板使用和芯片设计流程,熟悉使用下列软件: ·MATLAB/Simulink(作者使用R2012a). ·System Generator(作者使用14.3). A1.3实验任务 本实验主要分学习使用Simulink元件和Xilinx元件搭建电路模型,熟悉使用Simulink软 件界面,学习使用System Generator(SysGen)学习基于Simulink模型的综合流程。 A1.4实验步骤 1.启动MTALAB,指定一个工作目录(如F:FPGA\DSP\LAB1)为当前目录(见图A1.1)。 IATLAB7.11.0(K2010b Eile Edit Debug Desktop Mindow Help :凸白名马暗与CE目Current Fo1er:B:FPGAVDSP\LAB1 e Shorteuts How to Add What's Iew 图A1.1 MATLAB Simulink的启动按钮与当前目录窗口 2.单击MATLAB工具栏内的Simulink按键(见图A1.1),或在MATLAB命令行中输入simulink。 这时弹出Simulink Library Browser(见图A1.2)

实验二 Nexys 3 实验板及设计软件 实验二 Nexys 3 实验板及设计软件 A1.1 实验简介 Nexys3 实验板专门由 Xilinx 大学合作计划(XUP)为各种层次的大学工科培养计划设计, 由美国 Digilent 公司(www.digilentinc.com)制作。因 ISE 软件版本不同,读者所用软件的菜 单排列与名称可能与本实验介绍的略有不同,但其功能基本相同。读者可以参考本实验提供 的软件使用细节。 A1.2 实验目的 熟悉 Nexys3 实验板使用和芯片设计流程,熟悉使用下列软件: ·MATLAB/Simulink(作者使用 R2012a)。 ·System Generator(作者使用 14.3)。 A1.3 实验任务 本实验主要分学习使用 Simulink 元件和 Xilinx 元件搭建电路模型,熟悉使用 Simulink 软 件界面,学习使用 System Generator(SysGen)学习基于 Simulink 模型的综合流程。 A1.4 实验步骤 1. 启动 MTALAB,指定一个工作目录(如 F:\FPGA\DSP\LAB1)为当前目录(见图 A1.1)。 图 A1.1 MATLAB Simulink 的启动按钮与当前目录窗口 2. 单击MATLAB 工具栏内的Simulink按键(见图A1.1),或在MATLAB 命令行中输入simulink。 这时弹出 Simulink Library Browser(见图 A1.2)

实验二Nexys3实验板及设计软件 Simulink Library Browser ▣☒ Eile Edit View Help D >Enter search term 口蜗直 Libraries Library:Simulink Search Results:(none)Mc -Simulink 中 Communications Blockset Control System Toolbox 甲 EDA Simulator Link Image Acquisition Toolbox Real-Time Workshop Report Generator Signal Processing Blockset Commonly Used Blods Simulink 3D Animation Simulink Extras Simulink Verification and Validation Stateflow Video and Image Processing Blockset Xilinx Blockset Xilinx Reference Blockset Xilinx XtremeDSP Kit Continuous Discontinuities Showing:Simulink 图A1.2 Simulink单元库浏览器 3.选择File→New→Model命令,打开新建模型编辑器。 4.在Simulink Library Browser中浏览Xilinx Blockset(见图A1.3),选择Basic Elements选项。 从右边的元件窗口将以下图标拖曳到模型编辑器中从Xilnx Blockset目录下的Index栏目 下找到延迟(Delay)单元放入编辑器。从Simulink目录下的Sources栏目找到Constant 单元,从同一目录下的Sinks栏目找到Scope单元,均放入电路编辑器。 Xilinx Blockset +AX14 Basic Elements Communication Control Logic .DSP -Data Types .Index In Out .Math System Gatewey In Gateway Out .Memory Generator .Shared Memory .Tools 图A1.3 Xilinx Blocks菜单及当前电路

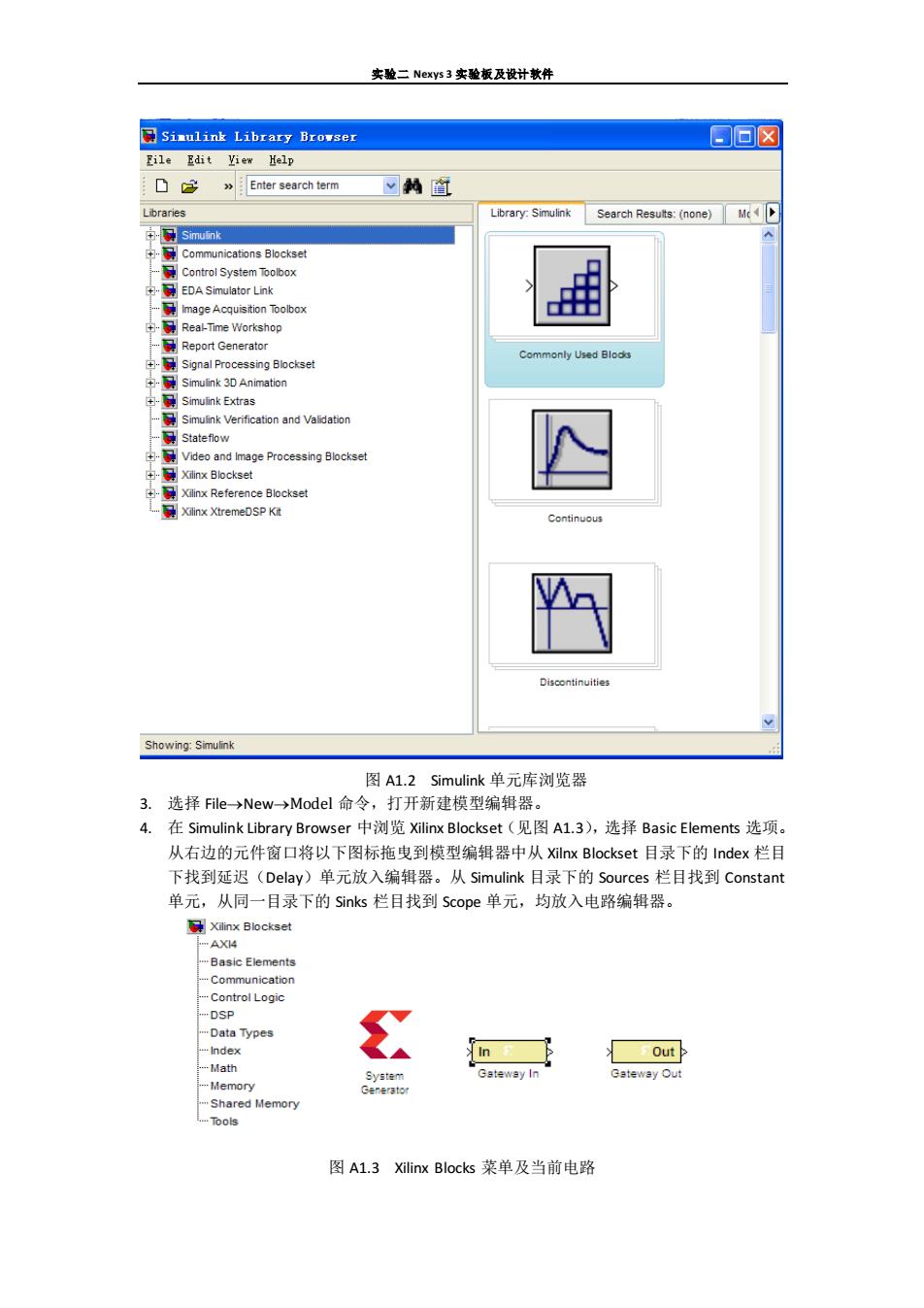

实验二 Nexys 3 实验板及设计软件 图 A1.2 Simulink 单元库浏览器 3. 选择 File→New→Model 命令,打开新建模型编辑器。 4. 在 Simulink Library Browser 中浏览 Xilinx Blockset(见图 A1.3),选择 Basic Elements 选项。 从右边的元件窗口将以下图标拖曳到模型编辑器中从 Xilnx Blockset 目录下的 Index 栏目 下找到延迟(Delay)单元放入编辑器。从 Simulink 目录下的 Sources 栏目找到 Constant 单元,从同一目录下的 Sinks 栏目找到 Scope 单元,均放入电路编辑器。 图 A1.3 Xilinx Blocks 菜单及当前电路

实验二Nexys3实验板及设计软件 5. 连接各模块:在Constant单元的输出端口按下鼠标左键,拉到Gateway In单元的输入端 口。连接成功后鼠标箭头的单线十字变为双线十字,放开鼠标左键后连接线由虚线变为 实线。所有单元前后连接完成后得到如图A1.4所示的电路。将模型保存到文件 delay1.mdl。放入的System Generator图标用于设置仿真参数和设计综合,不必连接到电 路。 In Out Constant Gateway In Gateway Out Delsy 图A1.4延迟单元与输入输出单元组成的电路(delay1.mdl) 6.为比较输入与输出波形,可以在信号源Constant与Gateway In之间连接另一个Scope(见 图A1.5a),或者接一个双输入端口Scope(见图A1.5b)。双击打开Scope,单击Scope 窗口上沿第二个工具图标Parameters,打开窗口后,在Numbers of axes文本框中填入2, 单机OK按钮后Scope的输入端口变为两个。如图A1.5b所示为将Scope输入端口之一 接Constant输出。 n Out Constant Gateway In Gateway Out Delay 图A1.5a输入端接另一个Scope n Out Constant Gateway In Gateway Out Scope 图A1.5b比较输入输出波形(delay2.md) 7.仿真之前先设置各单元的参数。双击各元件弹出参数设置窗口。图A1.6为Gateway In 的参数设置窗口。Gateway In相当与一个采样量化装置,用户可以选择采样周期(Sample period)、量化位宽(Number of bits)、对量化(Quantization)的处理(Truncate/Round) 和对溢出(Overflow)的处理(wrap/Saturate)等。如图A1.6所示设置Gateway In的参 数:位宽为8,小数位为0,Overflow设为Wrap,采样周期为1(默认值)。打开Constant 单元查看参数为单位阶跃输入(保持默认值不变).双击延迟单元查看延迟单位(Latency) 为1(默认值)。Gateway Out的功能是把8位定点数转化为浮点数后输出给Scope上。 打开Gateway Out确认Translate into output选项己被选中,保持参数不变

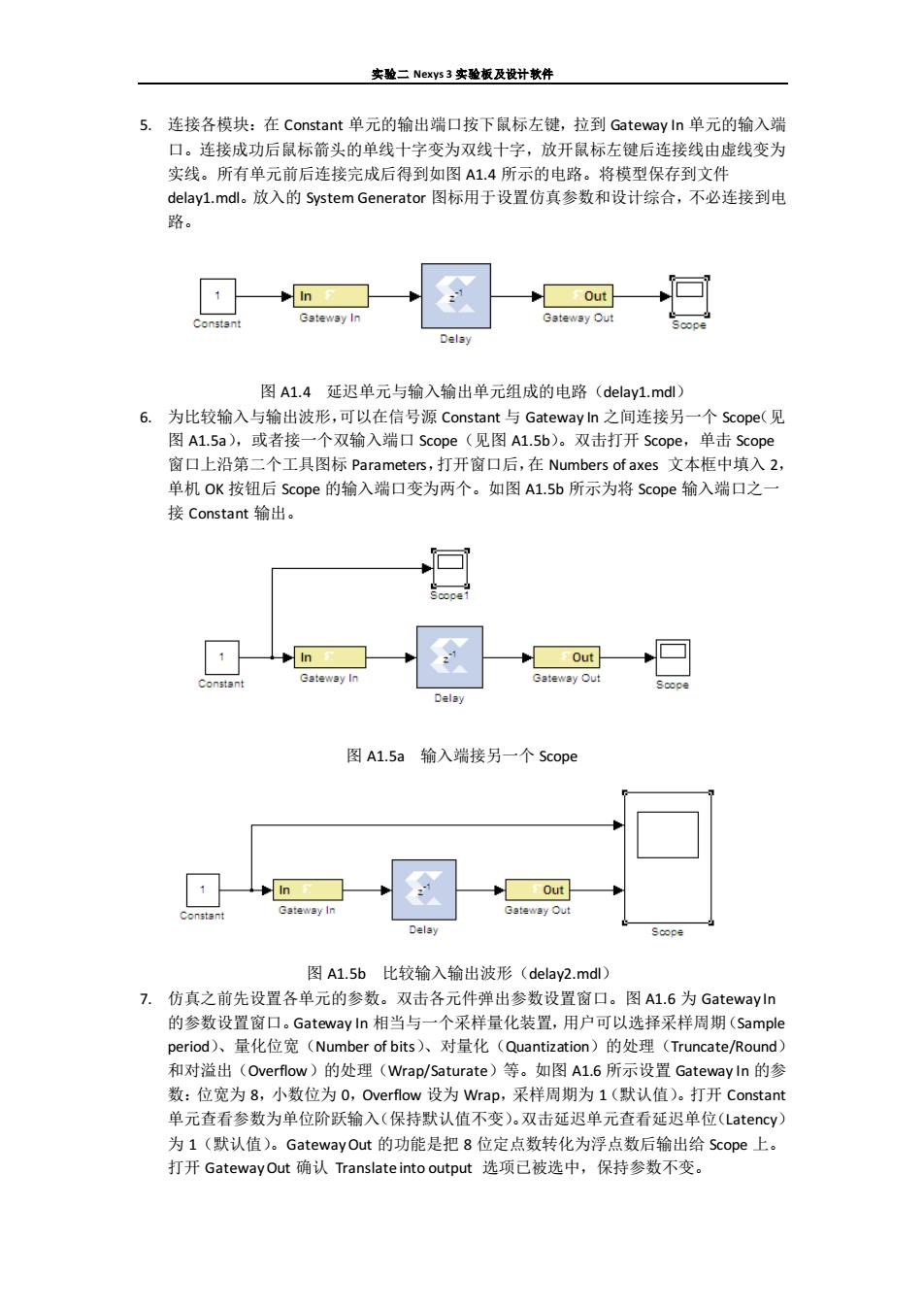

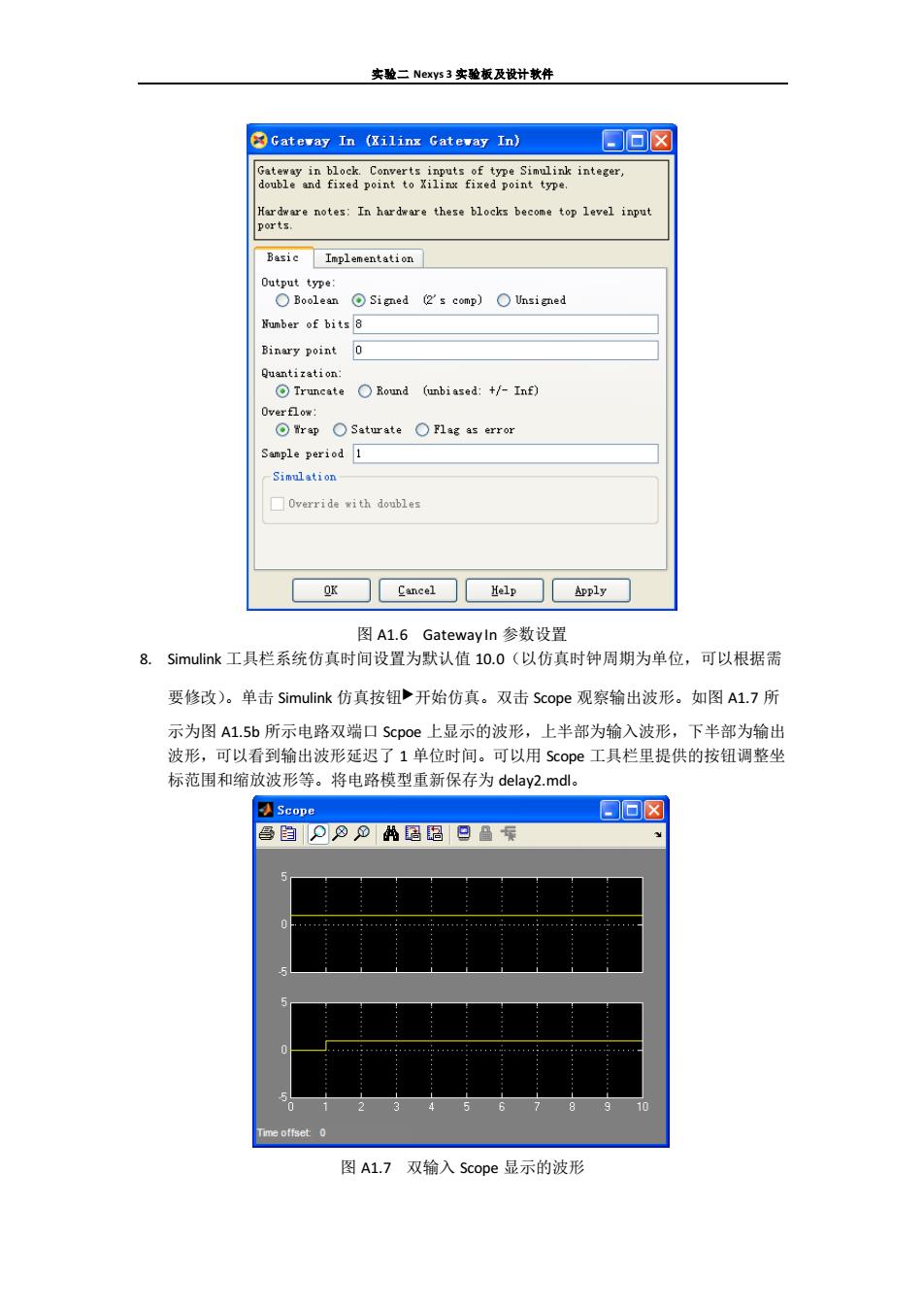

实验二 Nexys 3 实验板及设计软件 5. 连接各模块:在 Constant 单元的输出端口按下鼠标左键,拉到 Gateway In 单元的输入端 口。连接成功后鼠标箭头的单线十字变为双线十字,放开鼠标左键后连接线由虚线变为 实线。所有单元前后连接完成后得到如图 A1.4 所示的电路。将模型保存到文件 delay1.mdl。放入的 System Generator 图标用于设置仿真参数和设计综合,不必连接到电 路。 图 A1.4 延迟单元与输入输出单元组成的电路(delay1.mdl) 6. 为比较输入与输出波形,可以在信号源 Constant 与 Gateway In 之间连接另一个 Scope(见 图 A1.5a),或者接一个双输入端口 Scope(见图 A1.5b)。双击打开 Scope,单击 Scope 窗口上沿第二个工具图标 Parameters,打开窗口后,在 Numbers of axes 文本框中填入 2, 单机 OK 按钮后 Scope 的输入端口变为两个。如图 A1.5b 所示为将 Scope 输入端口之一 接 Constant 输出。 图 A1.5a 输入端接另一个 Scope 图 A1.5b 比较输入输出波形(delay2.mdl) 7. 仿真之前先设置各单元的参数。双击各元件弹出参数设置窗口。图 A1.6 为 Gateway In 的参数设置窗口。Gateway In 相当与一个采样量化装置,用户可以选择采样周期(Sample period)、量化位宽(Number of bits)、对量化(Quantization)的处理(Truncate/Round) 和对溢出(Overflow)的处理(Wrap/Saturate)等。如图 A1.6 所示设置 Gateway In 的参 数:位宽为 8,小数位为 0,Overflow 设为 Wrap,采样周期为 1(默认值)。打开 Constant 单元查看参数为单位阶跃输入(保持默认值不变)。双击延迟单元查看延迟单位(Latency) 为 1(默认值)。Gateway Out 的功能是把 8 位定点数转化为浮点数后输出给 Scope 上。 打开 Gateway Out 确认 Translate into output 选项已被选中,保持参数不变

实验二Nexys3实验板及设计软件 Gateway In (Xilinx Gateway In) 回☒ Gateway in block.Converts inputs of type Simulink integer double and fixed point to Xilinx fixed point type. Hardware notes:In hardware these blocks become top level input ports. Basic Implementation Dutput type: OBoolean Signed (2's comp)OUnsigned Number of bits 8 Binary point 6 Quantization Truncate O Round (unbiased:+/-Inf) Over flow: ⊙rap Saturate○1 ag as error Sample period 1 Simulation Override with doubles Q账 Cancel Help Apply 图A1.6 GatewayIn参数设置 8.Simulink工具栏系统仿真时间设置为默认值10.0(以仿真时钟周期为单位,可以根据需 要修改)。单击Simulink仿真按钮开始仿真。双击Scope观察输出波形。如图A1.7所 示为图A1.5b所示电路双端口Scpoe上显示的波形,上半部为输入波形,下半部为输出 波形,可以看到输出波形延迟了1单位时间。可以用Scope工具栏里提供的按钮调整坐 标范围和缩放波形等。将电路模型重新保存为delay2.mdl。 Scope 回☒ 昌自9超超回昌 Time offset:0 图A1.7双输入Scope显示的波形

实验二 Nexys 3 实验板及设计软件 图 A1.6 Gateway In 参数设置 8. Simulink 工具栏系统仿真时间设置为默认值 10.0(以仿真时钟周期为单位,可以根据需 要修改)。单击 Simulink 仿真按钮▶开始仿真。双击 Scope 观察输出波形。如图 A1.7 所 示为图 A1.5b 所示电路双端口 Scpoe 上显示的波形,上半部为输入波形,下半部为输出 波形,可以看到输出波形延迟了 1 单位时间。可以用 Scope 工具栏里提供的按钮调整坐 标范围和缩放波形等。将电路模型重新保存为 delay2.mdl。 图 A1.7 双输入 Scope 显示的波形

实验二Nexys3实验板及设计软件 9.在Simulink-→Sources目录下找到正弦信号(Sine wave)单元放入电路图。删除Constant 单元,用正弦信号单元代替常数单元接到Gateway In输入。打开Sine Wave单元,设置 参数如下:幅度(Amplitude)为50,频率(Frequency).为2*pi*100,采样时间(Sample time)为1e-4(即采样频率为1okHz)(见图A1.8)。同时设Gateway In的Sample period 为le-4。打开System Generate模块,将Simulink system period时间也设为1e-4。打开 延迟单元将Latency改为10。将Simulink仿真时间改为0.02(即2个正弦波周期)。 Parameters Sine type: Time based Time (t):Use simulation time Amplitude: 50 Bias: 0 Frequency (rad/sec): 2*pi*100 Phase (rad): 0 Sample time: 1e-4 Interpret vector parameters as 1-D 图A1.8 Sine Wave参数设置 10.单机仿真按钮,在Scope中看到如图A1.9所示的波形。分析观察到的延迟是否与电路设 计一致。将仿真正确的电路保存为sinewave.mdl。 Scope 日▣☒ 色自P9见的适超巴鱼 40 20 0.018 002 ime offsot 图A1.9 Scope显示输入输出正弦波形

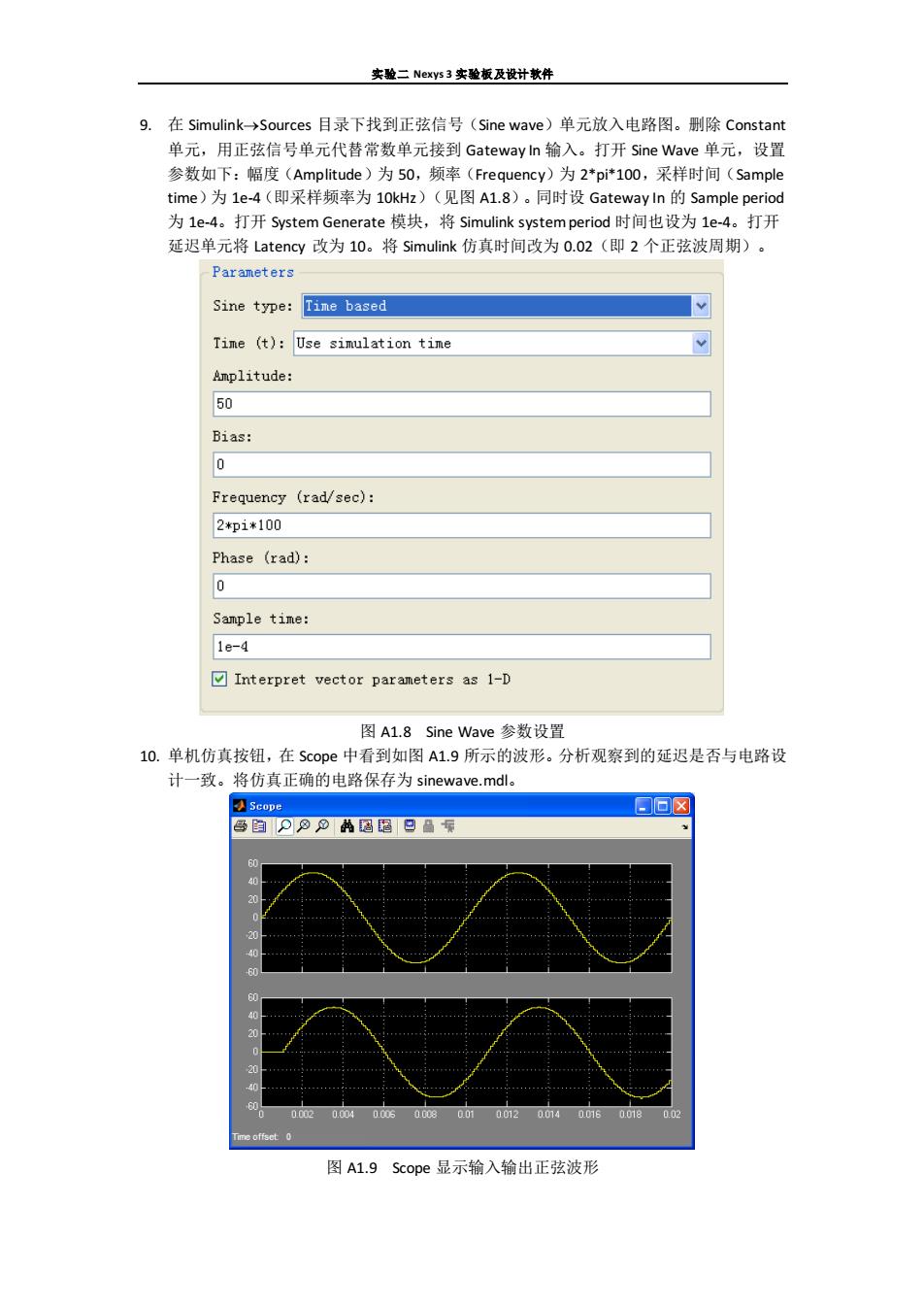

实验二 Nexys 3 实验板及设计软件 9. 在 Simulink→Sources 目录下找到正弦信号(Sine wave)单元放入电路图。删除 Constant 单元,用正弦信号单元代替常数单元接到 Gateway In 输入。打开 Sine Wave 单元,设置 参数如下:幅度(Amplitude)为 50,频率(Frequency)为 2*pi*100,采样时间(Sample time)为 1e-4(即采样频率为 10kHz)(见图 A1.8)。同时设 Gateway In 的 Sample period 为 1e-4。打开 System Generate 模块,将 Simulink system period 时间也设为 1e-4。打开 延迟单元将 Latency 改为 10。将 Simulink 仿真时间改为 0.02(即 2 个正弦波周期)。 图 A1.8 Sine Wave 参数设置 10. 单机仿真按钮,在 Scope 中看到如图 A1.9 所示的波形。分析观察到的延迟是否与电路设 计一致。将仿真正确的电路保存为 sinewave.mdl。 图 A1.9 Scope 显示输入输出正弦波形