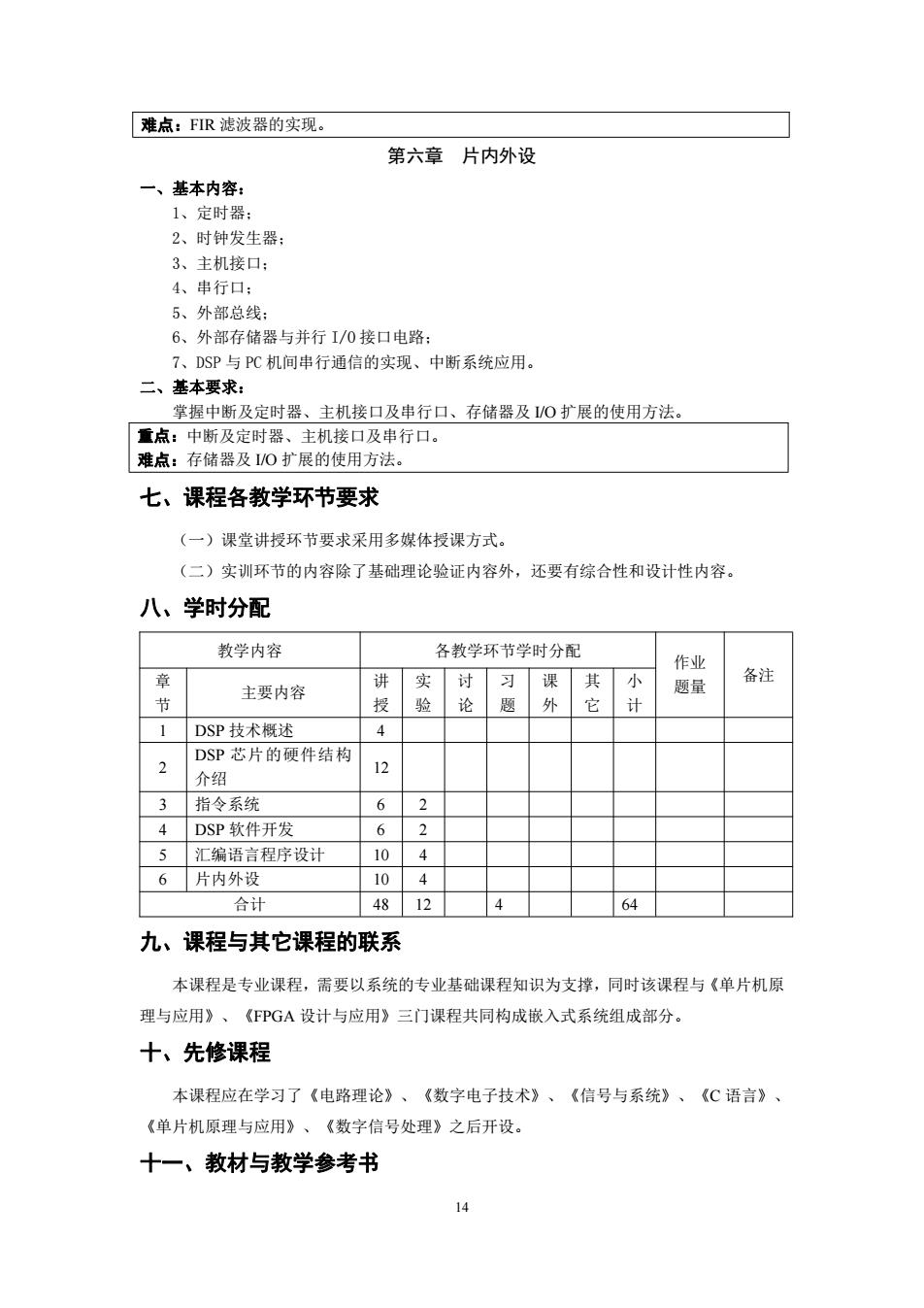

难点:FIR滤波器的实现。 第六章 片内外设 一、基本内容: 1、定时器: 2、时钟发生器: 3、主机接口: 4、串行口: 5、外部总线: 6、外部存储器与并行I/0接口电路: 7、DSP与PC机间串行通信的实现、中断系统应用。 二、基本要求: 掌握中断及定时器、主机接口及串行口、存储器及/O扩展的使用方法。 重点:中断及定时器、主机接口及串行口。 难点:存储器及IO扩展的使用方法。 七、课程各教学环节要求 (一)课堂讲授环节要求采用多媒体授课方式。 (二)实训环节的内容除了基础理论验证内容外,还要有综合性和设计性内容。 八、学时分配 教学内容 各教学环节学时分配 作业 章 讲 实 讨 习 课 其 小 题量 备注 节 主要内容 授 验 论 题 外 它 计 DSP技术概述 4 DSP芯片的硬件结构 2 12 介绍 3 指令系统 6 2 DSP软件开发 6 2 5 汇编语言程序设计 10 4 6 片内外设 10 4 合计 48 12 64 九、课程与其它课程的联系 本课程是专业课程,需要以系统的专业基础课程知识为支撑,同时该课程与《单片机原 理与应用》、《FPGA设计与应用》三门课程共同构成嵌入式系统组成部分。 十、先修课程 本课程应在学习了《电路理论》、《数字电子技术》、《信号与系统》、《C语言》、 《单片机原理与应用》、《数字信号处理》之后开设。 十一、教材与教学参考书 14

14 难点:FIR 滤波器的实现。 第六章 片内外设 一、基本内容: 1、定时器; 2、时钟发生器; 3、主机接口; 4、串行口; 5、外部总线; 6、外部存储器与并行 I/O 接口电路; 7、DSP 与 PC 机间串行通信的实现、中断系统应用。 二、基本要求: 掌握中断及定时器、主机接口及串行口、存储器及 I/O 扩展的使用方法。 重点:中断及定时器、主机接口及串行口。 难点:存储器及 I/O 扩展的使用方法。 七、课程各教学环节要求 (一)课堂讲授环节要求采用多媒体授课方式。 (二)实训环节的内容除了基础理论验证内容外,还要有综合性和设计性内容。 八、学时分配 教学内容 各教学环节学时分配 作业 题量 章 备注 节 主要内容 讲 授 实 验 讨 论 习 题 课 外 其 它 小 计 1 DSP 技术概述 4 2 DSP 芯片的硬件结构 介绍 12 3 指令系统 6 2 4 DSP 软件开发 6 2 5 汇编语言程序设计 10 4 6 片内外设 10 4 合计 48 12 4 64 九、课程与其它课程的联系 本课程是专业课程,需要以系统的专业基础课程知识为支撑,同时该课程与《单片机原 理与应用》、《FPGA 设计与应用》三门课程共同构成嵌入式系统组成部分。 十、先修课程 本课程应在学习了《电路理论》、《数字电子技术》、《信号与系统》、《C 语言》、 《单片机原理与应用》、《数字信号处理》之后开设。 十一、教材与教学参考书

(一)教材: [1]余成波.嵌入式DSP原理及应用.ISBN9787302258070.北京:清华大学出版社, 2012 (该教材是建议采用教材,也可以根据任课教师的建议选用新出版的不同教材) (二)教学参考书: [1]刘艳萍.DSP原理及应用教程.ISBN9787512408708.北京:北京航空航天大学出 版社,2012,第三版, [2]赵训威.基于TMS320C6200系列DSP芯片的应用与开发.ISBN7115102791.北京: 人民邮电出版社,2011. [3]汪春梅.TMS320C55xDSP原理及应用.ISBN9787121138348.北京:电子工业出 版社,2011,第三版

15 (一)教材: [1]余成波.嵌入式 DSP 原理及应用.ISBN 9787302258070.北京:清华大学出版社, 2012. (该教材是建议采用教材,也可以根据任课教师的建议选用新出版的不同教材) (二)教学参考书: [1]刘艳萍.DSP 原理及应用教程. ISBN 9787512408708.北京:北京航空航天大学出 版社,2012,第三版. [2]赵训威.基于 TMS320C6200 系列 DSP 芯片的应用与开发.ISBN 7115102791.北京: 人民邮电出版社,2011. [3]汪春梅.TMS320C55x DSP 原理及应用. ISBN9787121138348.北京:电子工业出 版社,2011,第三版.

《FPGA设计与应用》课程教学大纲 (System Design Based on FPGA) 学时数:40 学分数:2.5 课程类别:专业基础课 适用专业:电子信息工程专业 执笔者:蒋业文 审核人:王东 编写日期:2016年9月 一、课程简介 本课程是电子信息工程专业的一门专业任选课。主要介绍用计算机进行电子系统开发 的基本过程,掌握常用EDA软件的使用方法,重点使学生了解可编程芯片的基本工作原理, 掌握用Verilog HDL(或VHDL)设计数字电路的基本方法,学会用EDA工具软件及对HDL 程序进行仿真分析与综合。 主要内容:介绍了EDA技术、可编程逻辑器件的基本知识及使用方法:VHDL语言设 计方法:EDA的开发工具QuartusⅡ使用方法和技巧:基于VHDL的简单电路、应用电路及 综合电路的设计,通过18个典型数字电路系绞的设计实例(实例安排由简单到复杂),详细 地介绍了基于EDA技术“自顶向下的层次化设计方法和技巧。 二、课程的性质、目的和任务 本课程是电子信息工程专业的任选专业课程。要求学生通过本课程的学习和实验,初步 掌握常用EDA工具的使用方法、FPGA的开发技术以及VHDL语言的编程方法。能比较熟 练地使用Quartus等常用EDA软件对FPGA和CPLD作一些简单电路系统的设计,同时能 较好地使用VHDL语言设计简单的逻辑电路和逻辑系统,学会行为仿真、时序仿真和硬件 测试技术,为现代EDA工程技术的进一步学习,ASIC器件设计以及超大规模集成电路设 计奠定基础。利用Quartus软件一方面可以克服实验室各种条件的限制,另一方面可以针对 不同目的对学生进行训练,培养学生分析、应用和创新的能力。通过本课程的学习,使学生 能够理解和掌握EDA技术的思想,能够利用Quartus软件进行电子系统的设计。 三、课程教学的基本要求 (一)要求学生以VHDL语言为设计基础,并较深入地分析数字系统的工作原理,从 集成化的视角去理解系统的结构优化、时序、速度、面积和功耗等物理性能的设计优化理念, 使学生在学习了相关知识后能够立即动手具有一定应用价值的电路,真正做到学以致用。 (二)要求学生利用自己的计算机在课余时间完成自主设计项目,强化学习效果。 (三)本课程总学时为40学时,课堂教学为40学时,共2.5学分,实验另外开设。 四、教学手段与方法 以多媒体技术为主要手段的理论教学及实例教学。 五、考核方式与成绩评定 16

16 《FPGA 设计与应用》课程教学大纲 (System Design Based on FPGA) 学 时 数:40 学 分 数:2.5 课程类别:专业基础课 适用专业:电子信息工程专业 执 笔 者:蒋业文 审 核 人:王东 编写日期:2016 年 9 月 一、课程简介 本课程是电子信息工程专业的一门专业任选课。主要介绍用计算机进行电子系统开发 的基本过程,掌握常用 EDA 软件的使用方法,重点使学生了解可编程芯片的基本工作原理, 掌握用 Verilog HDL(或 VHDL)设计数字电路的基本方法,学会用 EDA 工具软件及对 HDL 程序进行仿真分析与综合。 主要内容:介绍了 EDA 技术、可编程逻辑器件的基本知识及使用方法;VHDL 语言设 计方法;EDA 的开发工具 QuartusⅡ使用方法和技巧;基于 VHDL 的简单电路、应用电路及 综合电路的设计,通过 18 个典型数字电路系绞的设计实例(实例安排由简单到复杂),详细 地介绍了基于 EDA 技术“自顶向下”的层次化设计方法和技巧。 二、课程的性质、目的和任务 本课程是电子信息工程专业的任选专业课程。要求学生通过本课程的学习和实验,初步 掌握常用 EDA 工具的使用方法、FPGA 的开发技术以及 VHDL 语言的编程方法。能比较熟 练地使用 Quartus 等常用 EDA 软件对 FPGA 和 CPLD 作一些简单电路系统的设计,同时能 较好地使用 VHDL 语言设计简单的逻辑电路和逻辑系统,学会行为仿真、时序仿真和硬件 测试技术,为现代 EDA 工程技术的进一步学习,ASIC 器件设计以及超大规模集成电路设 计奠定基础。利用 Quartus 软件一方面可以克服实验室各种条件的限制,另一方面可以针对 不同目的对学生进行训练,培养学生分析、应用和创新的能力。通过本课程的学习,使学生 能够理解和掌握 EDA 技术的思想,能够利用 Quartus 软件进行电子系统的设计。 三、课程教学的基本要求 (一)要求学生以 VHDL 语言为设计基础,并较深入地分析数字系统的工作原理,从 集成化的视角去理解系统的结构优化、时序、速度、面积和功耗等物理性能的设计优化理念, 使学生在学习了相关知识后能够立即动手具有一定应用价值的电路,真正做到学以致用。 (二)要求学生利用自己的计算机在课余时间完成自主设计项目,强化学习效果。 (三)本课程总学时为 40 学时,课堂教学为 40 学时,共 2.5 学分,实验另外开设。 四、教学手段与方法 以多媒体技术为主要手段的理论教学及实例教学。 五、考核方式与成绩评定

(一)考核方式 考核方式为开卷考试。严格考核学生出勤情况,达到学籍管理规定的旷课量取消考试资 格。 (二)成绩评定 综合成绩根据平时成绩、期末成绩评定,平时成绩占30%,期末成绩占70%。 六、课程的教学内容、重点和难点 第一章EDA技术概述 一、EDA技术及其发展 二、EDA技术实现目标 三、硬件描述语言 四、HDL综合 五、自顶向下的设计技术 六、EDA技术的优势 七、EDA设计流程 1、设计输入(原理图HDL文本编辑) 2、综合 3、适配 4、时序仿真与功能仿真 5、编程下载 6、硬件测试 八、ASIC及其设计流程 1、ASIC设计简介 2、ASIC设计一般流程简述 九、常用EDA工具 1、设计输入编辑器 2、HDL综合器 3、仿真器 4、适配器 5、下载器 十、QuartusⅡ概述 十一、P核 十二、EDA技术发展趋势管窥 重点:常用EDA工具。 难点:P核。 第二章FPGA与CPLD的结构原理 一、PLD概述 1、PLD的发展历程 2、PLD分类 二、简单PLD结构原理 1、逻辑元件符号表示 2、PROM结构原理 12

17 (一)考核方式 考核方式为开卷考试。严格考核学生出勤情况,达到学籍管理规定的旷课量取消考试资 格。 (二)成绩评定 综合成绩根据平时成绩、期末成绩评定,平时成绩占 30%,期末成绩占 70% 。 六、课程的教学内容、重点和难点 第一章 EDA 技术概述 一、EDA 技术及其发展 二、EDA 技术实现目标 三、硬件描述语言 四、HDL 综合 五、自顶向下的设计技术 六、EDA 技术的优势 七、EDA 设计流程 1、设计输入(原理图/HDL 文本编辑) 2、综合 3、适配 4、时序仿真与功能仿真 5、编程下载 6、硬件测试 八、ASIC 及其设计流程 1、ASIC 设计简介 2、ASIC 设计一般流程简述 九、常用 EDA 工具 1、设计输入编辑器 2、HDL 综合器 3、仿真器 4、适配器 5、下载器 十、 Quartus II 概述 十一、IP 核 十二、 EDA 技术发展趋势管窥 重点:常用 EDA 工具。 难点:IP 核。 第二章 FPGA 与 CPLD 的结构原理 一、PLD 概述 1、PLD 的发展历程 2、PLD 分类 二、简单 PLD 结构原理 1、逻辑元件符号表示 2、PROM 结构原理

3、PLA结构原理 4、PAL结构原理 5、GAL结构原理 三、CPLD的结构原理 四、FPGA的结构原理 1、查找表逻辑结构 2、Cyclone III系列器件的结构原理 五、硬件测试 1、内部逻辑测试 2、JTAG边界扫描 六、PLD产品概述 1、Altera公司的PLD器件 2、Lattice公司的PLD器件 3、Xilinx公司的PLD器件 4、Actel公司的PLD器件 5、Altera的FPGA配置方式 七、CPLD/FPGA的编程与配置 I、CPLD在系统编程 2、FPGA配置方式 3、FPGA专用配置器件 4、使用单片机配置FPGA 5、使用CPLD配置FPGA 重点:CPLD和FPGA的编程与配置。 难点:FPGA/CPLD测试技术。 第三章 组合电路的VHDL设计 一、多路选择器及其VHDL描述 二、半加器及其VHDL描述 三、4选1多路选择器及其VHDL描述 1、4选1多路选择器及CASE语句表述方式 2、CASE语句 3、EEE库预定义标准逻辑位与矢量 4、其他预定义标准数据类型 5、信号定义和数据对象 6、并置操作符 7、4选1多路选择器的VHDL不同描述方式 四、全加器及其VHDL表述 1、全加器设计及例化语句应用 2、VHDL例化语句 3、8位加法器设计及算术操作符应用 五、乘法器及其VHDL表述 1、统计位矢中含'1'个数的电路模块设计 2、FOR LOOP循环语句用法 3、移位相加型乘法器的VHDL表述方法 18

18 3、PLA 结构原理 4、PAL 结构原理 5、GAL 结构原理 三、CPLD 的结构原理 四、FPGA 的结构原理 1、查找表逻辑结构 2、Cyclone III 系列器件的结构原理 五、硬件测试 1、内部逻辑测试 2、JTAG 边界扫描 六、PLD 产品概述 1、Altera 公司的 PLD 器件 2、Lattice 公司的 PLD 器件 3、Xilinx 公司的 PLD 器件 4、Actel 公司的 PLD 器件 5、Altera 的 FPGA 配置方式 七、CPLD/FPGA 的编程与配置 1、CPLD 在系统编程 2、FPGA 配置方式 3、FPGA 专用配置器件 4、使用单片机配置 FPGA 5、使用 CPLD 配置 FPGA 重点:CPLD 和 FPGA 的编程与配置。 难点:FPGA/CPLD 测试技术。第三章 组合电路的 VHDL 设计 一、多路选择器及其 VHDL 描述 二、半加器及其 VHDL 描述 三、4 选 1 多路选择器及其 VHDL 描述 1、4 选 1 多路选择器及 CASE 语句表述方式 2、CASE 语句 3、IEEE 库预定义标准逻辑位与矢量 4、其他预定义标准数据类型 5、信号定义和数据对象 6、并置操作符 7、4 选 1 多路选择器的 VHDL 不同描述方式 四、全加器及其 VHDL 表述 1、全加器设计及例化语句应用 2、VHDL 例化语句 3、8 位加法器设计及算术操作符应用 五、乘法器及其 VHDL 表述 1、统计位矢中含 '1' 个数的电路模块设计 2、FOR_LOOP 循环语句用法 3、移位相加型乘法器的 VHDL 表述方法