第一章 引言 1.32金属互连线电感的研究现状 由于射频和微波通信市场的巨大潜力,国际上很多大学在十几年前就开始研究片 上电感,产生了一系列富有成果的论文。Chik Patrick Yuel.)提出了采用衬底地屏蔽 来降低半导体衬底电场损耗的思路;Sunderarajan S.Mohan!.l8I根据电感的几何参 数提出简单的电感表达式:Ali M.Niknejad1.2)在电磁场分析的基础上得到了著名的 电感分析设计软件ASITIC;Adam C.Watson1.2提出了宽带电感模型。 早在1960年就有人研究过在硅片上做平面电感,当时得出的结论是在硅集成电路 中集成电感是不实际的。直到l990年,Nguyen和Meyer首次发现电感能够在硅工艺 集成电路制作。近年来,随着无线通信技术的迅猛发展,人们越来越希望在射频集成 电路(RFIC)中集成电感,以满足低功耗、高集成度的要求,使得硅基集成电感成为 微电子领域一个新研究热点。与GAs半绝缘衬底不同,硅衬底是半导体,衬底的损 耗比较大,很难获得高的品质因数。最近,很多研究人员对非标准工艺的方法提高电 感的性能比较感兴趣,比如使用高电阻率(150-2002·)的硅衬底、将线圈下面的 硅腐蚀掉等(本文的研究集中在:在不改变工艺前提下实现片上电感的优化设计方法)。 硅基螺旋电感是实现片上电感的主要方式,它利用集成电路中的金属互连线围绕 成螺旋状而使其具有电感的特性。在标准CMOS工艺中,由于组成螺旋电感的金属连 线电阻较高,高频硅基衬底的损耗较大,使得硅基螺旋电感的品质因数普遍不高。螺 旋电感处于复杂的电磁场环境下,其模型建立和仿真也非常困难。十多年来,有许多 人致力于硅基集成螺旋电感的研究,这些研究主要集中在两个方面:一是建立硅基螺 旋电感的模型。目前,电感的模型从经典的窄带π模型12]发展为可按比例缩小的宽 带模型21,123-124。建模的主要目标是为了快速、精确、灵活地对硅基螺旋电感进行 仿真;二是关于硅基集成螺旋电感的设计和优化,主要目标是使硅基螺旋电感的品质 因数在一定的工作频率上最大化25-12刀。电感的寄生电容影响了电感的使用范围和品 质因数,因此电感的寄生电容也开始被分析研究28-13训。目前,科研人员还主要将 电感当成集成电路的一个元件在研究。 具有射频工艺的芯片代工厂可以提供片上电感,模型也足够精确,可以放到EDA 工具中仿真。通常,电感采用并联的金属互连线顶部两层金属设计而成,具有固定间 距、线宽和内半径,通过不同圈数实现不同电感值。线圈的形状通常为圆形(非常大 的多边形边数)和方形。芯片代工厂一般只提供单端电感,不提供差分电感,而且多 数没有地屏蔽,没有接地环。相对单一的电感种类,使得电路设计人员不能根据电路 的具体需调整电感,比如增大金属线宽,并联金属层数等,电路设计没有灵活性,不 能根据电路的实际需要增加和减少电感的寄生参量,不能任意调整电感值

第一章 引言 4 1.3.2 金属互连线电感的研究现状 由于射频和微波通信市场的巨大潜力,国际上很多大学在十几年前就开始研究片 上电感,产生了一系列富有成果的论文。Chik Patrick Yue[1.1] 提出了采用衬底地屏蔽 来降低半导体衬底电场损耗的思路;Sunderarajan S. Mohan[1.18] 根据电感的几何参 数提出简单的电感表达式;Ali M. Niknejad [1.21] 在电磁场分析的基础上得到了著名的 电感分析设计软件 ASITIC;Adam C. Watson [1.22]提出了宽带电感模型。 早在 1960 年就有人研究过在硅片上做平面电感,当时得出的结论是在硅集成电路 中集成电感是不实际的。直到 1990 年,Nguyen 和 Meyer 首次发现电感能够在硅工艺 集成电路制作。近年来,随着无线通信技术的迅猛发展,人们越来越希望在射频集成 电路(RF IC)中集成电感,以满足低功耗、高集成度的要求,使得硅基集成电感成为 微电子领域一个新研究热点。与 GaAs 半绝缘衬底不同,硅衬底是半导体,衬底的损 耗比较大,很难获得高的品质因数。最近,很多研究人员对非标准工艺的方法提高电 感的性能比较感兴趣,比如使用高电阻率(150-200Ω·m)的硅衬底、将线圈下面的 硅腐蚀掉等(本文的研究集中在:在不改变工艺前提下实现片上电感的优化设计方法)。 硅基螺旋电感是实现片上电感的主要方式,它利用集成电路中的金属互连线围绕 成螺旋状而使其具有电感的特性。在标准 CMOS 工艺中,由于组成螺旋电感的金属连 线电阻较高,高频硅基衬底的损耗较大,使得硅基螺旋电感的品质因数普遍不高。螺 旋电感处于复杂的电磁场环境下,其模型建立和仿真也非常困难。十多年来,有许多 人致力于硅基集成螺旋电感的研究,这些研究主要集中在两个方面:一是建立硅基螺 旋电感的模型。目前,电感的模型从经典的窄带π模型[1.22]发展为可按比例缩小的宽 带模型 [1.21, 1.23-1.24]。建模的主要目标是为了快速、精确、灵活地对硅基螺旋电感进行 仿真;二是关于硅基集成螺旋电感的设计和优化,主要目标是使硅基螺旋电感的品质 因数在一定的工作频率上最大化[1.25-1.27]。电感的寄生电容影响了电感的使用范围和品 质因数,因此电感的寄生电容也开始被分析研究 [1.28-1.31] 。目前,科研人员还主要将 电感当成集成电路的一个元件在研究。 具有射频工艺的芯片代工厂可以提供片上电感,模型也足够精确,可以放到 EDA 工具中仿真。通常,电感采用并联的金属互连线顶部两层金属设计而成,具有固定间 距、线宽和内半径,通过不同圈数实现不同电感值。线圈的形状通常为圆形(非常大 的多边形边数)和方形。芯片代工厂一般只提供单端电感,不提供差分电感,而且多 数没有地屏蔽,没有接地环。相对单一的电感种类,使得电路设计人员不能根据电路 的具体需调整电感,比如增大金属线宽,并联金属层数等,电路设计没有灵活性,不 能根据电路的实际需要增加和减少电感的寄生参量,不能任意调整电感值

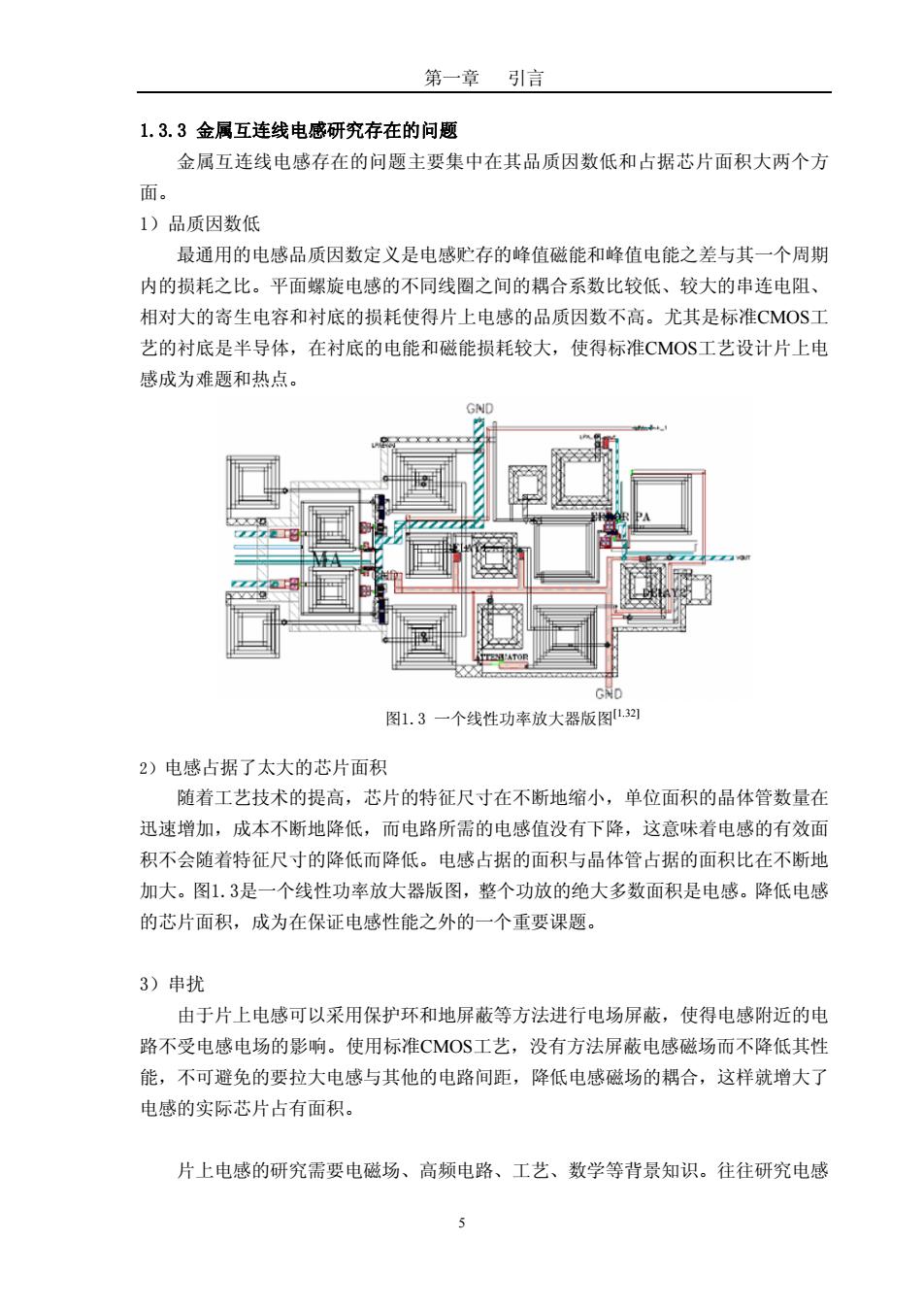

第一章 引言 1.3.3金属互连线电感研究存在的问题 金属互连线电感存在的问题主要集中在其品质因数低和占据芯片面积大两个方 面。 1)品质因数低 最通用的电感品质因数定义是电感贮存的峰值磁能和峰值电能之差与其一个周期 内的损耗之比。平面螺旋电感的不同线圈之间的耦合系数比较低、较大的串连电阻、 相对大的寄生电容和衬底的损耗使得片上电感的品质因数不高。尤其是标准CMOS工 艺的衬底是半导体,在衬底的电能和磁能损耗较大,使得标准CMOS工艺设计片上电 感成为难题和热点。 GND GND 图1.3一个线性功率放大器版图,3 2)电感占据了太大的芯片面积 随着工艺技术的提高,芯片的特征尺寸在不断地缩小,单位面积的晶体管数量在 迅速增加,成本不断地降低,而电路所需的电感值没有下降,这意味着电感的有效面 积不会随着特征尺寸的降低而降低。电感占据的面积与晶体管占据的面积比在不断地 加大。图1.3是一个线性功率放大器版图,整个功放的绝大多数面积是电感。降低电感 的芯片面积,成为在保证电感性能之外的一个重要课题。 3)串扰 由于片上电感可以采用保护环和地屏蔽等方法进行电场屏蔽,使得电感附近的电 路不受电感电场的影响。使用标准CMOS工艺,没有方法屏蔽电感磁场而不降低其性 能,不可避免的要拉大电感与其他的电路间距,降低电感磁场的耦合,这样就增大了 电感的实际芯片占有面积。 片上电感的研究需要电磁场、高频电路、工艺、数学等背景知识。往往研究电感

第一章 引言 5 1.3.3 金属互连线电感研究存在的问题 金属互连线电感存在的问题主要集中在其品质因数低和占据芯片面积大两个方 面。 1)品质因数低 最通用的电感品质因数定义是电感贮存的峰值磁能和峰值电能之差与其一个周期 内的损耗之比。平面螺旋电感的不同线圈之间的耦合系数比较低、较大的串连电阻、 相对大的寄生电容和衬底的损耗使得片上电感的品质因数不高。尤其是标准CMOS工 艺的衬底是半导体,在衬底的电能和磁能损耗较大,使得标准CMOS工艺设计片上电 感成为难题和热点。 图1.3 一个线性功率放大器版图[1.32] 2)电感占据了太大的芯片面积 随着工艺技术的提高,芯片的特征尺寸在不断地缩小,单位面积的晶体管数量在 迅速增加,成本不断地降低,而电路所需的电感值没有下降,这意味着电感的有效面 积不会随着特征尺寸的降低而降低。电感占据的面积与晶体管占据的面积比在不断地 加大。图1.3是一个线性功率放大器版图,整个功放的绝大多数面积是电感。降低电感 的芯片面积,成为在保证电感性能之外的一个重要课题。 3)串扰 由于片上电感可以采用保护环和地屏蔽等方法进行电场屏蔽,使得电感附近的电 路不受电感电场的影响。使用标准CMOS工艺,没有方法屏蔽电感磁场而不降低其性 能,不可避免的要拉大电感与其他的电路间距,降低电感磁场的耦合,这样就增大了 电感的实际芯片占有面积。 片上电感的研究需要电磁场、高频电路、工艺、数学等背景知识。往往研究电感

第一章引言 的人具有物理背景,而缺少电路知识,将电感作为一个元器件研究。具有电路知识的 人往往不具备物理背景,很难对电感优化设计。电感的设计要根据电路的需要来调整 电感的电感值、寄生电阻和寄生电容,达到电路的性能最佳。 1.4论文的组织结构 片上电感不是一个理想元件,除了固有的电感外,它还具有寄生的电阻、电容以 及衬底损耗。论文的第二章至第四章就是在使用电磁理论分析电感固有和寄生参量的 基础上,针对降低电感的芯片面积、提高电感的品质因数以及改善使用电感电路的性 能展开的。 第二章讲述了片上电感的常规设计方法,从片上电感的物理特性出发,分析了片 上电感品质因数低的种种原因:耦合系数低、有寄生电容、串联电阻欧姆损耗大、衬 底的电场和磁场损耗等。本章的内容为电感的优化设计提供了理论依据。 第三章在第二章的理论指导下,从集成电路设计以及工艺的角度出发,分析了电 感的耦合系数、寄生电容、串联电阻以及衬底损耗,结合已有的优化设计和新提出的 方法为电感的优化指出了方向。从集成电路设计的角度出发,在不改变工艺的前提下, 新提出的片上电感优化方法主要有: 1)采用电感半径和整体线圈宽度比值大的结构增大线圈间的耦合系数: 2)采用“Z”字开槽的连接方式设计垂直串连电感,增大电感的耦合系数,降低 电感的芯片面积: 3)从改进的分布电容公式出发,提出降低电感临近线圈之间寄生电容以及电感与 衬底之间寄生电容的方法: 4)借鉴分立元件的LTZ金属线结构,提出利用集成电路互连线实现相同阻抗小 横截面积的金属线并联(多电流路径)成同一个金属线圈,进而抑制电流拥挤 效应: 5)在衬底损耗物理模型的基础上,提出多p结衬底隔离、低电感电压、小电感电 流以及小面积电感等方法降低电感衬底损耗。 在深入了解电感的寄生参量的物理和电学性质,以及深刻理解影响电感应用电路 的性能的基础上,提出合理利用片上电感的寄生参量优化电路设计,比如将金属地屏 蔽结构引起的高品质因数寄生电容并入LC CVO中的并联电容等电路优化设计方法。 论述了p结衬底隔离明显降低电感与衬底之间电容的前提条件,进而提出电感自调谐 振荡器,理论上证明了该结构比常规LC VCO性能好。不再将电感当成一个元件,而 是一个LCR参数相互关联的子电路,作为一个整体放到应用电路中,根据电路的性能 优化,提出可行的电感优化方向。 第四章在提出可缩放的地屏蔽开路通路去嵌入方法基础上,流片验证了第三章提 6

第一章 引言 6 的人具有物理背景,而缺少电路知识,将电感作为一个元器件研究。具有电路知识的 人往往不具备物理背景,很难对电感优化设计。电感的设计要根据电路的需要来调整 电感的电感值、寄生电阻和寄生电容,达到电路的性能最佳。 1.4 论文的组织结构 片上电感不是一个理想元件,除了固有的电感外,它还具有寄生的电阻、电容以 及衬底损耗。论文的第二章至第四章就是在使用电磁理论分析电感固有和寄生参量的 基础上,针对降低电感的芯片面积、提高电感的品质因数以及改善使用电感电路的性 能展开的。 第二章讲述了片上电感的常规设计方法,从片上电感的物理特性出发,分析了片 上电感品质因数低的种种原因:耦合系数低、有寄生电容、串联电阻欧姆损耗大、衬 底的电场和磁场损耗等。本章的内容为电感的优化设计提供了理论依据。 第三章在第二章的理论指导下,从集成电路设计以及工艺的角度出发,分析了电 感的耦合系数、寄生电容、串联电阻以及衬底损耗,结合已有的优化设计和新提出的 方法为电感的优化指出了方向。从集成电路设计的角度出发,在不改变工艺的前提下, 新提出的片上电感优化方法主要有: 1)采用电感半径和整体线圈宽度比值大的结构增大线圈间的耦合系数; 2)采用“Z”字开槽的连接方式设计垂直串连电感,增大电感的耦合系数,降低 电感的芯片面积; 3)从改进的分布电容公式出发,提出降低电感临近线圈之间寄生电容以及电感与 衬底之间寄生电容的方法; 4)借鉴分立元件的LITZ金属线结构,提出利用集成电路互连线实现相同阻抗小 横截面积的金属线并联(多电流路径)成同一个金属线圈,进而抑制电流拥挤 效应; 5)在衬底损耗物理模型的基础上,提出多pn结衬底隔离、低电感电压、小电感电 流以及小面积电感等方法降低电感衬底损耗。 在深入了解电感的寄生参量的物理和电学性质,以及深刻理解影响电感应用电路 的性能的基础上,提出合理利用片上电感的寄生参量优化电路设计,比如将金属地屏 蔽结构引起的高品质因数寄生电容并入LC CVO中的并联电容等电路优化设计方法。 论述了pn结衬底隔离明显降低电感与衬底之间电容的前提条件,进而提出电感自调谐 振荡器,理论上证明了该结构比常规LC VCO性能好。不再将电感当成一个元件,而 是一个LCR参数相互关联的子电路,作为一个整体放到应用电路中,根据电路的性能 优化,提出可行的电感优化方向。 第四章在提出可缩放的地屏蔽开路通路去嵌入方法基础上,流片验证了第三章提

第一章引言 出的部分电感的优化结构和优化方法,例如降低芯片面积的叠层结构电感、高品质因 数和自谐振频率的差分电感以及采用降低相邻线圈电压和拉开大电压差线圈间距的方 法降低差分电感的临近金属间寄生电容、采用多层金属并联降低电感的直流电阻、并 联小横截面积金属抑制电流拥挤效应、p结衬底隔离降低衬底损耗等电感优化方法。 分析了各种地屏蔽结构,提出了地屏蔽结构提高电感性能的前提条件。 第五章对全文进行了总结,指出了片上电感还需要深入研究的工作方向。 近几年关于片上电感的硕士、博士论文以及期刊、会议论文大量涌现。但是很少 有人系统的从电感的物理本质以及寄生参量的特性出发研究电感。本论文系统的分析 了片上电感的电磁现象以及寄生参量的特性,进而提出了种种优化方法,最后给出了 试验验证。指出电感的优化设计不能独立的进行,需要将电感当成一个LC℉相互关联 的子电路,放到电感电路中进行优化设计。要以电路合适的性价比为条件优化设计电 感,为今后的电感优化设计指明了方向。 参考文献 [1.1]Chik Patrick Yue.On-chip spiral inductors for silicon-based radio-frequency integrated circuits [D]. A dissertation of the department of electrical engineering of STANFORD University for the doctor philosophy,1998. [1.2]T.H.Lee.The Design of CMOS Radio-Frequency Integrated Circuits [M].New York,New York: Cambridge University Press,1998. [1.3]Gramegna,G;Paparo,M.;Erratico,P.G;De Vita,P..A sub-1-dB NF+2.3-kV ESD-protected 900-MHz CMOS LNA [J].IEEE Journal of Solid-State Circuits,2001,36(7):1010-1017 [1.4]Egels,M.;Gaubert,J.;Pannier,P;Bourdel,S..Design method for fully integrated CMOS RF LNA [J].Electronics Letters,2004,40(24):1513-1514. [1.5]Vauhkonen,A.;Tarvainen,E..Inductors allow low-voltage performance for IC mixers [C].IEEE International Conference on Electronics,Circuits and Systems,1998,1(9):329-332. [1.6]Tae Wook Kim;Bonkee Kim;Lee,K.A new mixer linearization method and optimization of integrated inductor for single balance mixer LO buffer [C].IEEE Radio Frequency Integrated Circuits(RF IC)Symposium,2004.Digest of Papers.2004,6-8(6):43-46. [1.7]Burghartz,J.N.;Soyuer,M.;Jenkins,K.A.;Hulvey,M.D..High-Q inductors in standard silicon interconnect technology and its application to an integrated RF power amplifier [C].International Electron Devices Meeting,1995,10-13(9):1015-1018. [1.8]Gupta,R.;Ballweber,B.M.;Allstot,D.J.Design and optimization of CMOS RF power amplifiers [J].IEEE Journal of Solid-State Circuits,2001,36(2):166-175. >

第一章 引言 7 出的部分电感的优化结构和优化方法,例如降低芯片面积的叠层结构电感、高品质因 数和自谐振频率的差分电感以及采用降低相邻线圈电压和拉开大电压差线圈间距的方 法降低差分电感的临近金属间寄生电容、采用多层金属并联降低电感的直流电阻、并 联小横截面积金属抑制电流拥挤效应、pn结衬底隔离降低衬底损耗等电感优化方法。 分析了各种地屏蔽结构,提出了地屏蔽结构提高电感性能的前提条件。 第五章对全文进行了总结,指出了片上电感还需要深入研究的工作方向。 近几年关于片上电感的硕士、博士论文以及期刊、会议论文大量涌现。但是很少 有人系统的从电感的物理本质以及寄生参量的特性出发研究电感。本论文系统的分析 了片上电感的电磁现象以及寄生参量的特性,进而提出了种种优化方法,最后给出了 试验验证。指出电感的优化设计不能独立的进行,需要将电感当成一个 LCR 相互关联 的子电路,放到电感电路中进行优化设计。要以电路合适的性价比为条件优化设计电 感,为今后的电感优化设计指明了方向。 参考文献 [1.1] Chik Patrick Yue. On-chip spiral inductors for silicon-based radio-frequency integrated circuits [D]. A dissertation of the department of electrical engineering of STANFORD University for the doctor philosophy, 1998. [1.2] T.H. Lee. The Design of CMOS Radio-Frequency Integrated Circuits [M]. New York, New York: Cambridge University Press, 1998. [1.3] Gramegna, G.; Paparo, M.; Erratico, P.G.; De Vita, P.. A sub-1-dB NF±2.3-kV ESD-protected 900-MHz CMOS LNA [J]. IEEE Journal of Solid-State Circuits, 2001, 36(7):1010 – 1017. [1.4] Egels, M.; Gaubert, J.; Pannier, P.; Bourdel, S.. Design method for fully integrated CMOS RF LNA [J]. Electronics Letters, 2004, 40 (24):1513 – 1514. [1.5] Vauhkonen, A.; Tarvainen, E.. Inductors allow low-voltage performance for IC mixers [C]. IEEE International Conference on Electronics, Circuits and Systems, 1998, 1(9):329 – 332. [1.6] Tae Wook Kim; Bonkee Kim; Lee, K. A new mixer linearization method and optimization of integrated inductor for single balance mixer LO buffer [C]. IEEE Radio Frequency Integrated Circuits (RF IC) Symposium, 2004. Digest of Papers. 2004, 6-8(6):43 – 46. [1.7] Burghartz, J.N.; Soyuer, M.; Jenkins, K.A.; Hulvey, M.D.. High-Q inductors in standard silicon interconnect technology and its application to an integrated RF power amplifier [C]. International Electron Devices Meeting, 1995, 10-13(9):1015 – 1018. [1.8] Gupta, R.; Ballweber, B.M.; Allstot, D.J. Design and optimization of CMOS RF power amplifiers [J]. IEEE Journal of Solid-State Circuits, 2001, 36(2):166 – 175

第一章引言 [1.9]Joonho Gil;Seong-Sik Song;Hyunjin Lee;Hyungcheol Shin.A-119.2 dBc/Hz at 1 MHz,1.5 mW, fully integrated,2.5-GHz,CMOS VCO using helical inductors [J].IEEE Microwave and Wireless Components Letters,[see also IEEE Microwave and Guided Wave Letters]2003,13(11):457- 459 [1.10]Yong Zhan;Harjani,R.;Sapatnekar,S.S..On the selection of on-chip inductors for the optimal VCO design [C]Proceedings of the IEEE Custom Integrated Circuits Conference,2004, 3-6(10):277-280. [1.11]Mohan,S.S.;Hershenson,M.D.M.;Boyd,S.P;Lee,T.H..Bandwidth extension in CMOS with optimized on-chip inductors [J].IEEE Journal of Solid-State Circuits,2000,35(3):346-355. [1.12]Soorapanth,T.;Wong,S.S.A 0-dB IL 2140+30 MHz bandpass filter utilizing Q-enhanced spiral inductors in standard CMOS [J].IEEE Journal of Solid-State Circuits,2002,37(5):579-586. [1.13]Niranjan Talwalkar.Integrated CMOS Transmit-Receive Switch Using On-Chip Spiral Inductors [D].A DISSERTATION FOR THE DEGREE OF DOCTOR OF PHILOSOPHY OF THE DEPARTMENT OF ELECTRICAL ENGINEERING OF STANFORD UNIVERSITY.2004 [1.14]Lucyszyn,S.;Robertson,I.D.Monolithic narrow-band filter using ultrahigh-Q tunable active inductors [J].IEEE Transactions on Microwave Theory and Techniques,1994,42(12):2617- 2622. [1.15]Curtis Leifso,James W.Haslett,John GMcRory.Monolithic tunable active inductor with independent Q control [J].IEEE Trans.Microwave theory and techniques,2000,48(6):1024- 1029 [1.16]Francesco Svelto and Rinaldo Castello.A bond-wire inductor-MOS varactor VCO tunable from 1.8 to 2.4 GHz [J].IEEE Trans.Microwave theiry and techniques,2002,50(1):403-407. [1.17]Dec,A.;Suyama,K.A 1.9-GHz CMOS VCO with micromachined electromechanically tunable capacitors [J].IEEE Journal of Solid-State Circuits,35(8):1231-1237. [1.18]Tony Yeung.Analysis and Design of On-chip Spiral Inductors and Transformers for Silicon RF Integrated Circuits [D]A thesis for Master of Philosophy in Electrical and Electronic Engineering at The Hong Kong University of Science and Technology in December 1998. [1.19]Sunderarajan S.Mohan.The design,modeling and optimization of on-chip inductor and transformer circuits [D].A dissertation of the department of electrical engineering of STANFORD University for the doctor philosophy,1999. [1.20]Ali M.Niknejad.Analysis,Simulation,and Applications of Passive Devices on Conductive Substrates [D].A dissertation for the degree of Doctor of Philosophy in Engineering-Electrical Engineering and Computer Science in the UNIVERSITY of CALIFORNIA at BERKELEY,2000. [1.21]Adam C.Watson.Analysis and Modeling of Single-Ended and Differential Spiral Inductors in

第一章 引言 8 [1.9] Joonho Gil; Seong-Sik Song; Hyunjin Lee; Hyungcheol Shin. A -119.2 dBc/Hz at 1 MHz, 1.5 mW, fully integrated, 2.5-GHz, CMOS VCO using helical inductors [J]. IEEE Microwave and Wireless Components Letters, [see also IEEE Microwave and Guided Wave Letters] 2003, 13(11):457 – 459. [1.10]Yong Zhan; Harjani, R.; Sapatnekar, S.S.. On the selection of on-chip inductors for the optimal VCO design [C] Proceedings of the IEEE Custom Integrated Circuits Conference, 2004, 3-6(10) :277 – 280. [1.11]Mohan, S.S.; Hershenson, M.D.M.; Boyd, S.P.; Lee, T.H. . Bandwidth extension in CMOS with optimized on-chip inductors [J]. IEEE Journal of Solid-State Circuits, 2000, 35(3):346 – 355. [1.12]Soorapanth, T.; Wong, S.S. A 0-dB IL 2140±30 MHz bandpass filter utilizing Q-enhanced spiral inductors in standard CMOS [J]. IEEE Journal of Solid-State Circuits, 2002, 37(5):579 – 586. [1.13]Niranjan Talwalkar. Integrated CMOS Transmit-Receive Switch Using On-Chip Spiral Inductors [D]. A DISSERTATION FOR THE DEGREE OF DOCTOR OF PHILOSOPHY OF THE DEPARTMENT OF ELECTRICAL ENGINEERING OF STANFORD UNIVERSITY, 2004. [1.14]Lucyszyn, S.; Robertson, I.D. Monolithic narrow-band filter using ultrahigh-Q tunable active inductors [J]. IEEE Transactions on Microwave Theory and Techniques, 1994, 42(12):2617 – 2622. [1.15]Curtis Leifso, James W.Haslett, John G.McRory. Monolithic tunable active inductor with independent Q control [J]. IEEE Trans. Microwave theory and techniques, 2000, 48(6): 1024 – 1029. [1.16]Francesco Svelto and Rinaldo Castello. A bond-wire inductor-MOS varactor VCO tunable from 1.8 to 2.4 GHz [J]. IEEE Trans. Microwave theiry and techniques,2002, 50(1):403-407. [1.17]Dec, A.; Suyama, K. A 1.9-GHz CMOS VCO with micromachined electromechanically tunable capacitors [J]. IEEE Journal of Solid-State Circuits, 35(8): 1231 – 1237. [1.18]Tony Yeung. Analysis and Design of On-chip Spiral Inductors and Transformers for Silicon RF Integrated Circuits [D] A thesis for Master of Philosophy in Electrical and Electronic Engineering at The Hong Kong University of Science and Technology in December 1998. [1.19]Sunderarajan S. Mohan. The design, modeling and optimization of on-chip inductor and transformer circuits [D]. A dissertation of the department of electrical engineering of STANFORD University for the doctor philosophy, 1999. [1.20]Ali M. Niknejad. Analysis, Simulation, and Applications of Passive Devices on Conductive Substrates [D]. A dissertation for the degree of Doctor of Philosophy in Engineering–Electrical Engineering and Computer Science in the UNIVERSITY of CALIFORNIA at BERKELEY, 2000. [1.21]Adam C. Watson. Analysis and Modeling of Single-Ended and Differential Spiral Inductors in