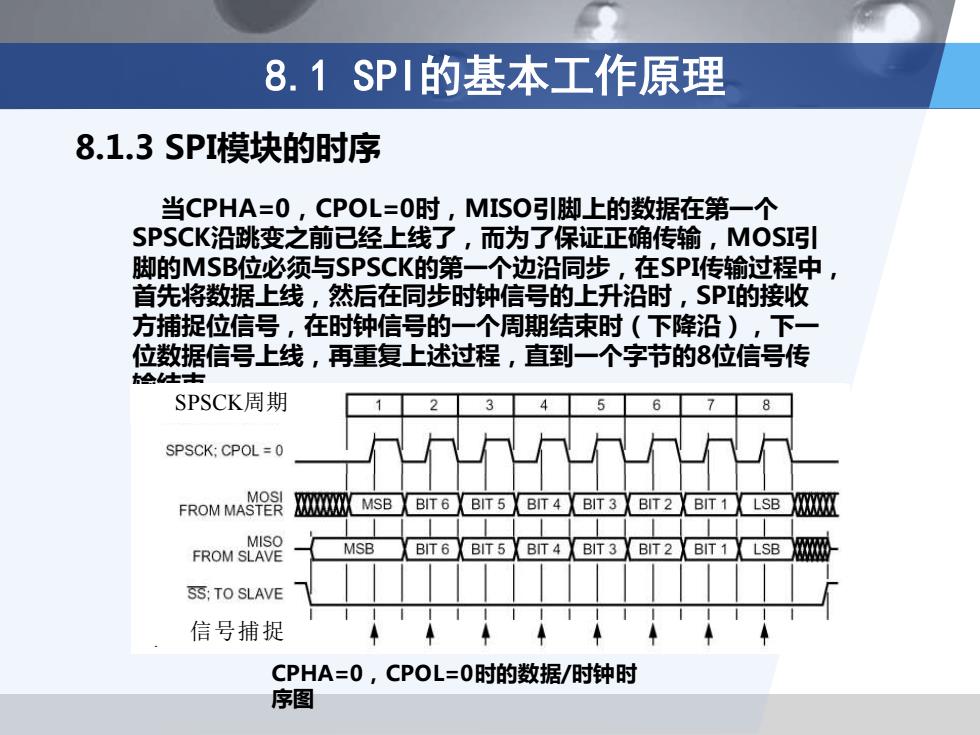

8.1SPI的基本工作原理 8.1.3SPI模块的时序 当CPHA=0,CPOL=0时,MISO引脚上的数据在第一个 SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引 脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中, 首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收 方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一 位数据信号上线,再重复上述过程,直到一个字节的8位信号传 h△士-与 SPSCK周期 3 4 5 6 SPSCK:CPOL =0 FROM MAST2器 XX MSB BITG (BIT 5 BIT 4 MIsO FROM SLAVE MSB (BIT 6X BIT 5 BIT 4 BIT 3 X BIT 2 X BIT 1 LSB SS:TO SLAVE 信号捕捉 CPHA=0,CPOL=0时的数据/时钟时 序图

8.1.3 SPI模块的时序 当CPHA=0,CPOL=0时,MISO引脚上的数据在第一个 SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引 脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中, 首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收 方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一 位数据信号上线,再重复上述过程,直到一个字节的8位信号传 输结束。 SPSCK周期 信号捕捉 点 CPHA=0,CPOL=0时的数据/时钟时 序图 8.1 SPI的基本工作原理

8.1SPI的基本工作原理 8.1.3SPI模块的时序 3 4 5 6 8 SPSCK:CPOL =1 MOSI FROM MASTER BIT 6 BIT 5 BIT 4 BIT 3 BIT2 BIT 1 LSB MISO FROM SLAVE MSB BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 LSB SS:TO SLAVE 信号捕捉 CPHA=0,CPOL=1时的数据/时钟时序 图

8.1.3 SPI模块的时序 8.1 SPI的基本工作原理 信号捕捉 CPHA=0,CPOL=1时的数据/时钟时序 图