电子科越女学 University of Electrsic Science and Technology China 时域测试技术综合实验 信号采集抽取功能设计实验

信号采集抽取功能设计实验 时域测试技术综合实验

一、实验目的 1.了解信号采集过程中抽取功能的作用, 2.掌握分级计数器的设计原理; 3,掌握利用计数器控制FFO写使能以实现抽取的方法。 二、实验内容 1.利用计数器控制FIFO写使能,实现抽取; 2.利用分级计数的方式编写一个计数器,该计数器的模最大为 65536;

一、实验目的 1. 了解信号采集过程中抽取功能的作用; 2. 掌握分级计数器的设计原理; 3. 掌握利用计数器控制FIFO写使能以实现抽取的方法。 二、实验内容 1.利用计数器控制FIFO写使能,实现抽取; 2. 利用分级计数的方式编写一个计数器,该计数器的模最大为 65536;

三、预备知识 1.了解高速数据采集与测试技术实验平台硬件结构; 2.熟悉Verilog HDL硬件描述语言; 3.掌握Xilinx ISE Design Suite?开发软件使用方法。 四、实验设备与工具 硬件:高速数据采集与测试技术实验平台, 微型计算机, XILINX USB调试下载器。 软件:Windows操作系统, Xilinx ISE Design Suite 14.7

三、预备知识 1. 了解高速数据采集与测试技术实验平台硬件结构; 2. 熟悉Verilog HDL硬件描述语言; 3. 掌握Xilinx ISE Design Suite开发软件使用方法。 四、实验设备与工具 硬件:高速数据采集与测试技术实验平台, 微型计算机, XILINX USB调试下载器。 软件:Windows操作系统, Xilinx ISE Design Suite 14.7

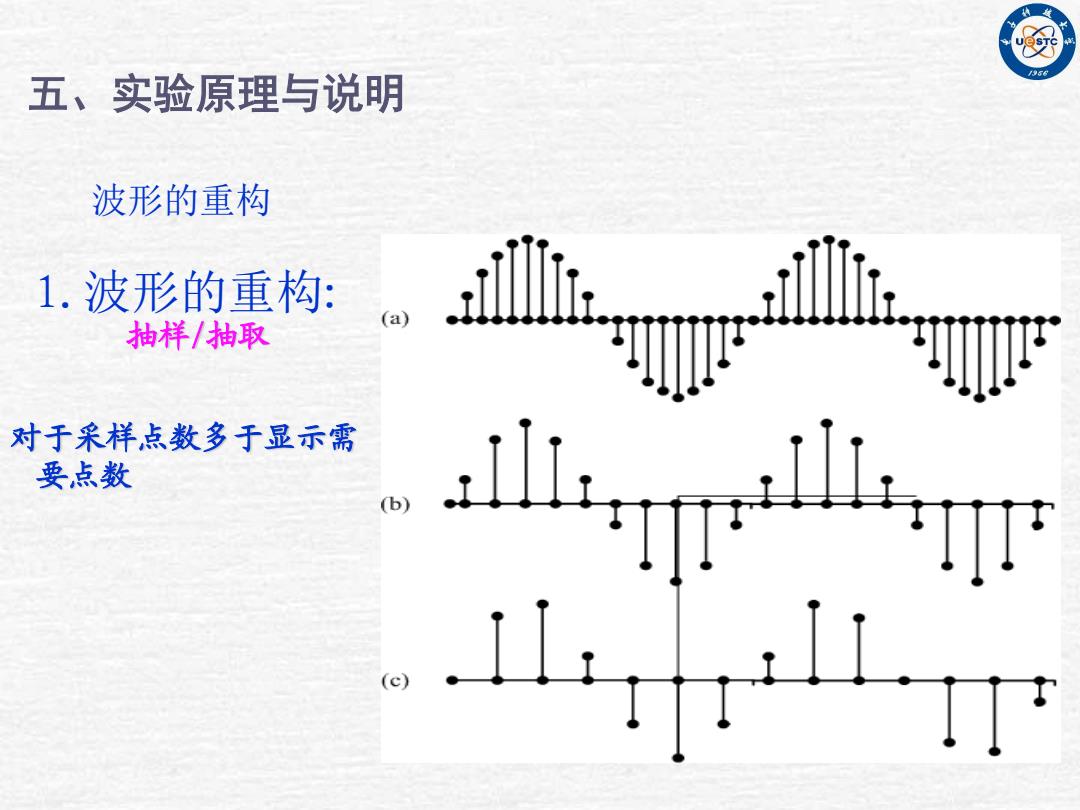

五、实验原理与说明 波形的重构 1.波形的重构: 抽样/抽取 对于采样点数多于显示需 要点数 b) c)

1.波形的重构: 波形的重构 抽样/抽取 对于采样点数多于显示需 要点数 五、实验原理与说明

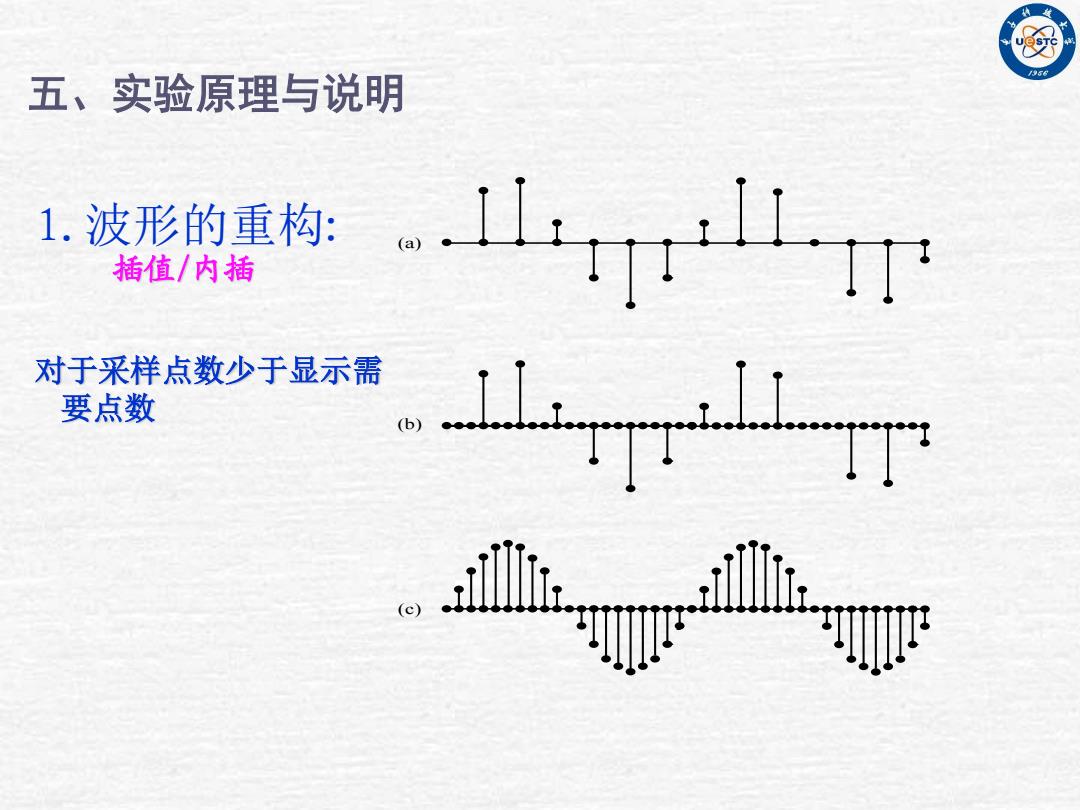

五、实验原理与说明 1的1T 插值/内插 对于采样点数少于显示需 要点数

1.波形的重构: 插值/内插 (a) (b) (c) 对于采样点数少于显示需 要点数 五、实验原理与说明