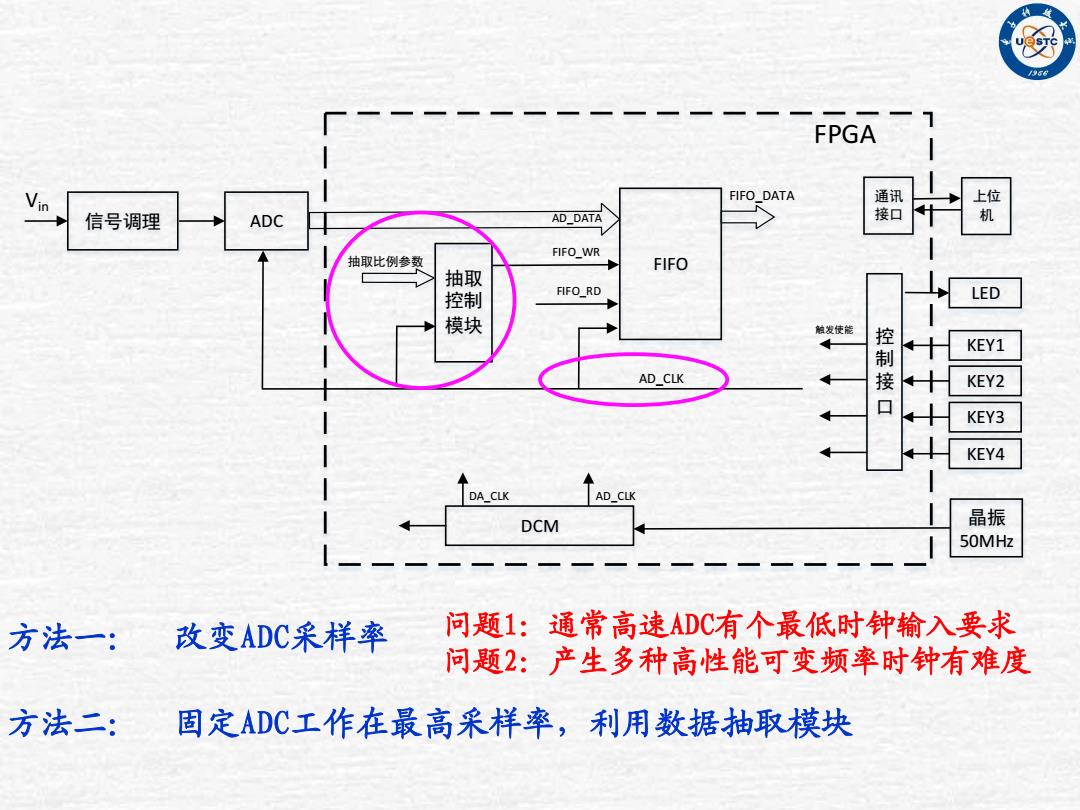

FPGA Vin FIFO DATA 通讯 上位 信号调理 ADC AD_DATA 接口 机 FIFO_WR 抽取比例参数 FIFO 抽取 控制 FIFO RD LED 模块 触发使能 控制 KEY1 AD_CLK KEY2 KEY3 KEY4 DA CLK AD_CLK DCM 晶振 50MHz 方法一: 改变ADC采样率 问题1:通常高速ADC有个最低时钟输入要求 问题2:产生多种高性能可变频率时钟有难度 方法二: 固定ADC工作在最高采样率,利用数据抽取模块

DCM 晶振 50MHz 控 制 接 口 KEY1 KEY2 KEY3 KEY4 LED FPGA 信号调理 ADC Vin FIFO FIFO_DATA FIFO_WR FIFO_R D AD_CLK DA_CLK AD_CLK AD_DATA 触发使能 通讯 接口 上位 机 抽取 控制 模块 抽取比例参数 方法一: 改变ADC采样率 问题1:通常高速ADC有个最低时钟输入要求 问题2:产生多种高性能可变频率时钟有难度 方法二: 固定ADC工作在最高采样率,利用数据抽取模块

S/H 8-BIT 8 ADC1 Selectable DI DEMUX LATCH Data Bus Output 16 LVDS Pairs INPUT MUX VINQ+ S/H VINQ- 8-BIT ADC2 Selectable Data Bus Output Typical Limits Units Symbol Parameter Conditions (Note 8) (Note 8) (Limits) AC ELECTRICAL CHARACTERISTICS Normal Mode(non DES)or DES Mode in ADC08D1020 1.3 1.0 GHz(min) Maximum Input Clock 1:2 Demux Output fCLK (max) Frequency Normal Mode(non DES)or DES Mode in 1.0 GHz (max) Non-demux Output Minimum Input Clock Normal Mode(non DES) 200 MHz fCLK (min) Frequency DES Mode 500 MHz 200MHz≤fcK≤1GHz 20 %(min) 50 (Normal Mode)(Note 12) 80 %(max) Input Clock Duty Cycle 500MH≤fcLK≤1GHz 20 %(min) 50 (DES Mode)(Note 12) 80 %(max) Input Clock Low Time (Note 11) 500 200 ps(min)

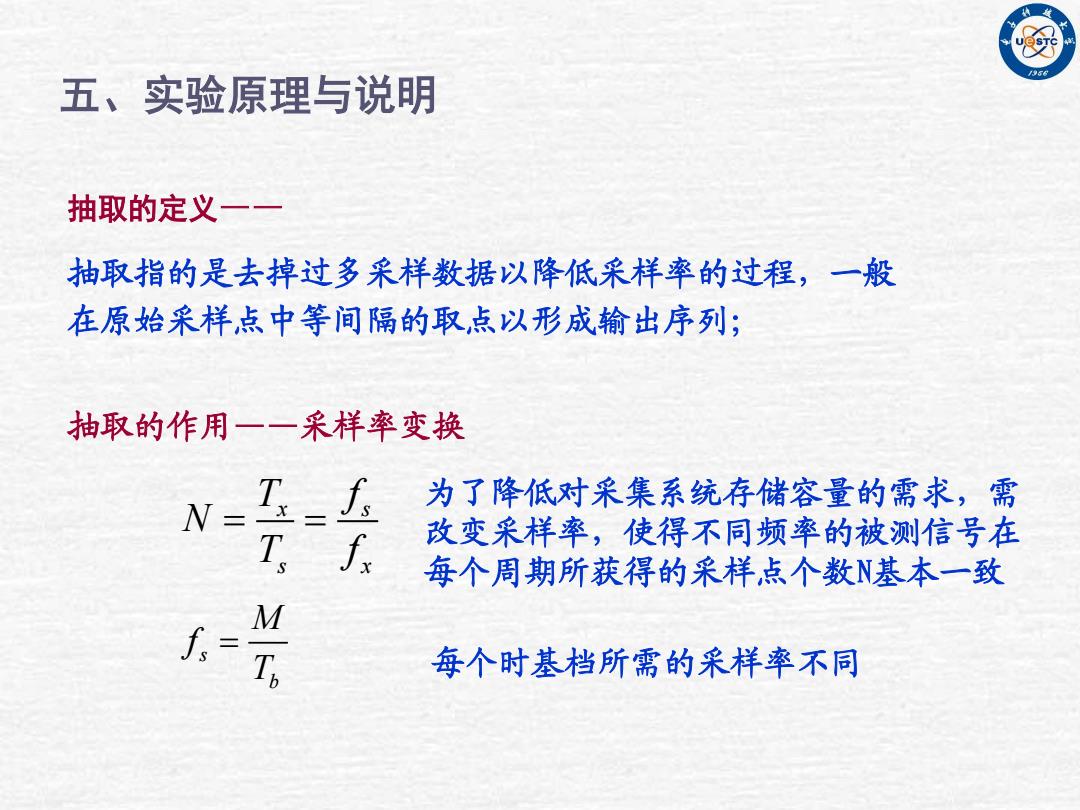

956 五、实验原理与说明 抽取的定义一一 抽取指的是去掉过多采样数据以降低采样率的过程,一般 在原始采样点中等间隔的取,点以形成输出序列; 抽取的作用一一采样率变换 为了降低对采集系统存储容量的需求,需 N= = T f 改变采样率,使得不同频率的被测信号在 每个周期所获得的采样,点个数N基本一致 M 每个时基档所需的采样率不同

五、实验原理与说明 抽取的定义—— 抽取指的是去掉过多采样数据以降低采样率的过程,一般 在原始采样点中等间隔的取点以形成输出序列; 抽取的作用——采样率变换 x s s x T f N T f = = s b M f T = 为了降低对采集系统存储容量的需求,需 改变采样率,使得不同频率的被测信号在 每个周期所获得的采样点个数N基本一致 每个时基档所需的采样率不同

利用计数器实现抽取 不抽取时,如果将存储器FFO的写使能打开,且一直维持高电平, 则采样数据将被连续存入FIFO中。图1中1、2、3、4...等均会被 存入FIFO。 数据时钟 采样数据 01X23 4 5 6 FIFO写使能 不抽取时采样数据存储时序图

利用计数器实现抽取 不抽取时,如果将存储器FIFO的写使能打开,且一直维持高电平, 则采样数据将被连续存入FIFO中。图1中1、2、3、4……等均会被 存入FIFO。 0 1 2 3 4 5 6 数据时钟 采样数据 FIFO写使能 不抽取时采样数据存储时序图

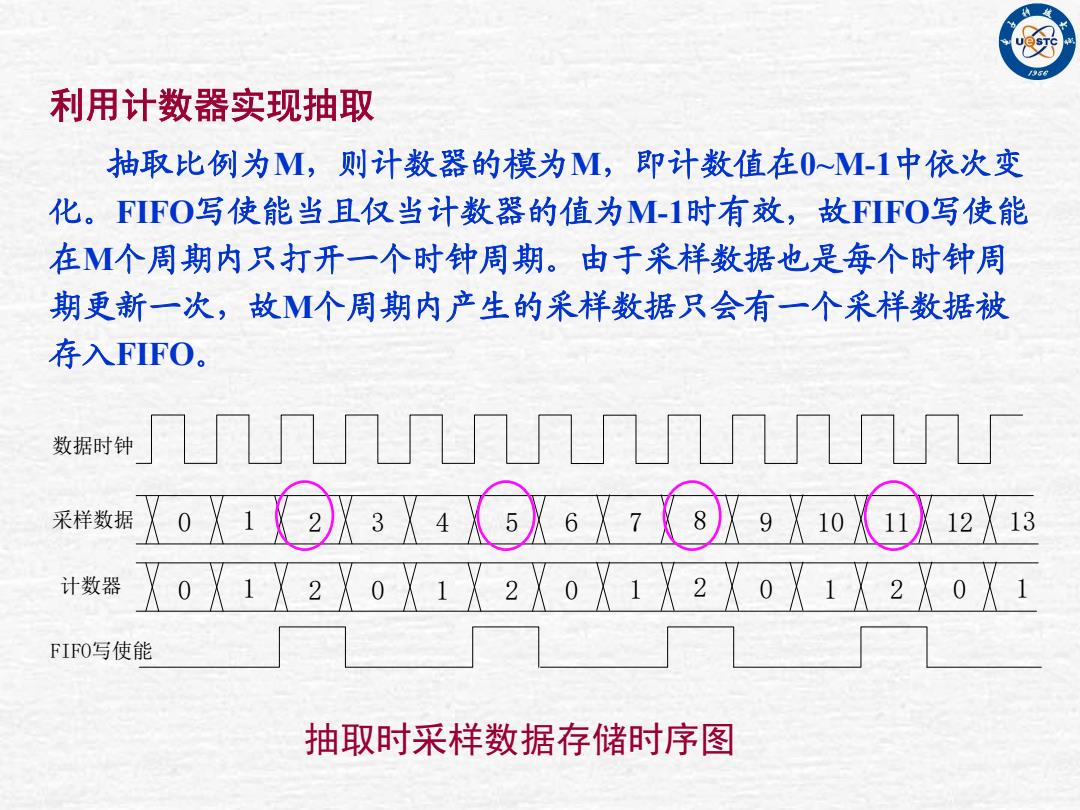

利用计数器实现抽取 抽取比例为M,则计数器的模为M,即计数值在0~M-1中依次变 化。FIFO写使能当且仅当计数器的值为M-1时有效,故FIFO写使能 在M个周期内只打开一个时钟周期。由于采样数据也是每个时钟周 期更新一次,故M个周期内产生的采样数据只会有一个采样数据被 存入FIFO。 数据时钟 L具P 采样数据 0123X4⑤678X9X10⊙12X18 计数器 0X1X2 2 FIFO写使能 抽取时采样数据存储时序图

利用计数器实现抽取 抽取比例为M,则计数器的模为M,即计数值在0~M-1中依次变 化。FIFO写使能当且仅当计数器的值为M-1时有效,故FIFO写使能 在M个周期内只打开一个时钟周期。由于采样数据也是每个时钟周 期更新一次,故M个周期内产生的采样数据只会有一个采样数据被 存入FIFO。 抽取时采样数据存储时序图 0 1 2 3 4 5 6 数据时钟 采样数据 FIFO写使能 7 8 9 10 11 12 13 计数器 0 1 2 0 1 2 0 1 2 0 1 2 0 1