1.省电(Idle) ●为了减少功耗,可使时钟发生器处于省电dle)状态; ●当时钟发生器退出省电状态时,若进入Idle前是旁路模 式,仍返回旁路模式;若进入Idle前是锁定模式,仍返回 锁定模式,返回到锁定模式的方式与时钟模式寄存器 CLKMD的省电位IAI(Initialize-After-Idle)有关: ◆IAI=O:PLL将使用与进入Idle状态之前相同的锁定 设置进行锁定,不需重新启动锁定序列过程; IAI=1:PLL将重新启动锁定序列过程 进入锁相状态过程:在旁路模式下,CLKMD的PLL ENABLE1 →启动PLL→进入锁相序列:产生配置的输出频率,输出 与输入锁相,进入锁定模式(之前都是旁路模式) 14

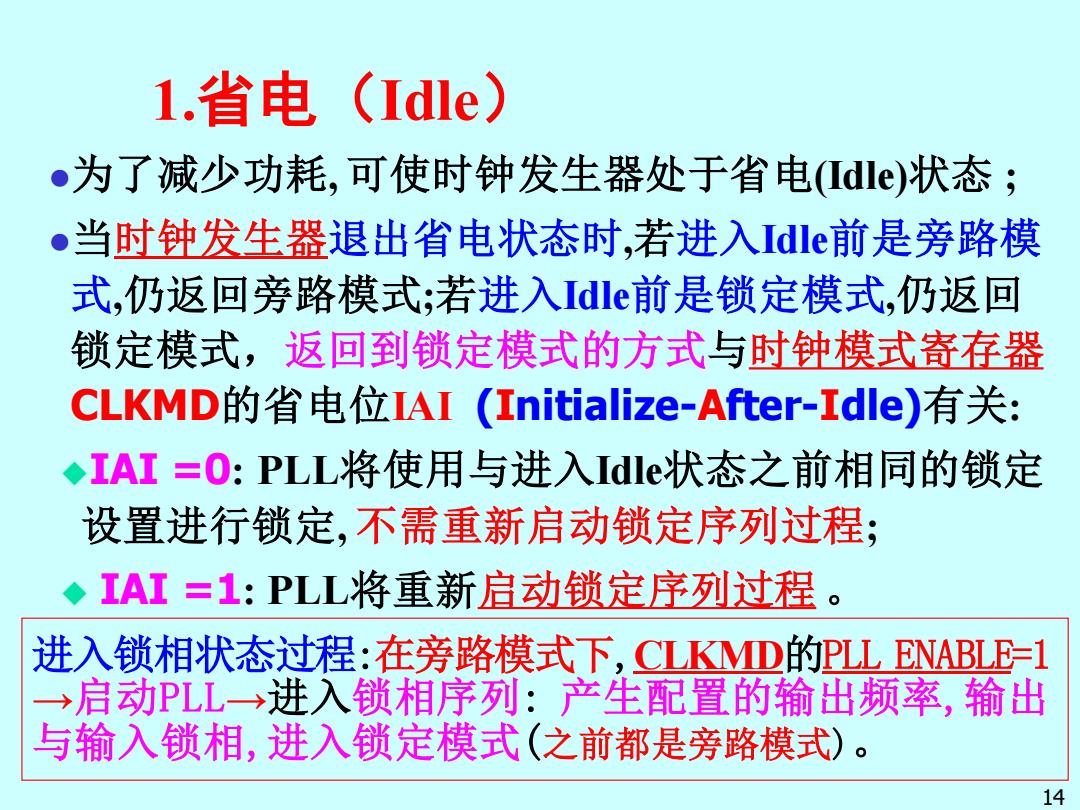

1.省电(Idle) ⚫为了减少功耗, 可使时钟发生器处于省电(Idle)状态 ; ⚫当时钟发生器退出省电状态时,若进入Idle前是旁路模 式,仍返回旁路模式;若进入Idle前是锁定模式,仍返回 锁定模式,返回到锁定模式的方式与时钟模式寄存器 CLKMD的省电位IAI (Initialize-After-Idle)有关: ◆IAI =0: PLL将使用与进入Idle状态之前相同的锁定 设置进行锁定, 不需重新启动锁定序列过程; ◆ IAI =1: PLL将重新启动锁定序列过程 。 14 进入锁相状态过程:在旁路模式下,CLKMD的PLL ENABLE=1 →启动PLL→进入锁相序列: 产生配置的输出频率,输出 与输入锁相,进入锁定模式(之前都是旁路模式)

2.DSP复位 在DSP复位期间和复位之后,PLL工作于旁路模式, 输出的时钟频率由CLKMD引脚(TMS320C5510 芯片上有)上的电平确定: ◆如果CLKMD引脚为低电平,则输出CPU时钟频 率等于输入频率; ◆如果CLKMD引脚为高电平,则输出CPU时钟频 率等于输入频率的1/2。 输出频率=输入频率 注意:5509(A)等无CLKMD引脚! 复位值:BYPASS DIV=O0 15

2.DSP复位 ⚫在DSP复位期间和复位之后,PLL工作于旁路模式, 输出的时钟频率由CLKMD引脚(TMS320C5510 芯片上有)上的电平确定: ◆ 如果CLKMD引脚为低电平,则输出CPU时钟频 率等于输入频率; ◆ 如果CLKMD引脚为高电平,则输出CPU时钟频 率等于输入频率的1/2。 注意: 5509(A)等无CLKMD引脚! 15 输出频率=输入频率 复位值: BYPASS DIV=00

3.失锁 锁相环PLL对输入时钟跟踪锁定之后,可能会由于 其他原因使其输出时钟相位发生偏移,导致失锁。 出现失锁现象后,PLL的动作由时钟模式寄存器 CLKMD中的IOB确定: ◆IOB=O:时钟发生器不中断PLL,PLL继续输出时钟; 输出频率= PLLMULT2-31)× 输入频率 PLL DIV0~3)+1 I0B=1:时钟发生器切换到旁路模式,重新启动锁 定序列过程。 进入锁相状态过程:在旁路模式下,CLKMD的PLL ENABLE=1→启动PLL→进入锁相序列:产生输出频率, 输出与输入锁相,进入锁定模式(之前都是旁路模式)

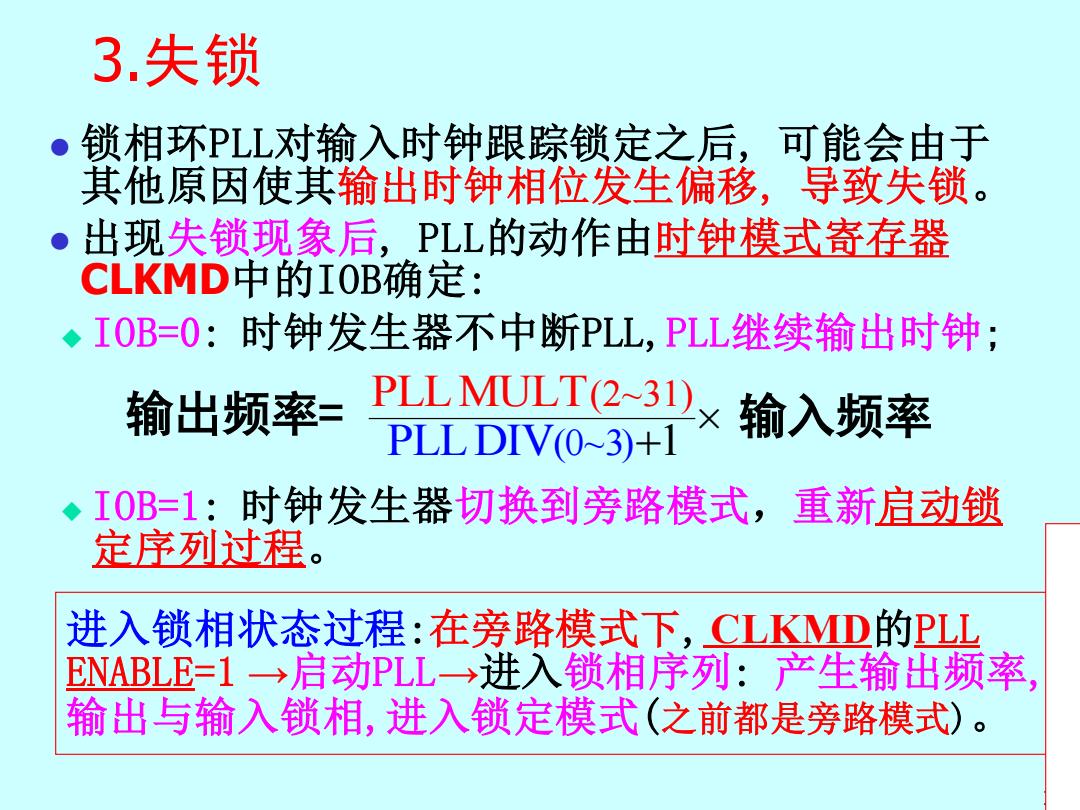

3.失锁 ⚫ 锁相环PLL对输入时钟跟踪锁定之后, 可能会由于 其他原因使其输出时钟相位发生偏移, 导致失锁。 ⚫ 出现失锁现象后, PLL的动作由时钟模式寄存器 CLKMD中的IOB确定: ◆ IOB=0: 时钟发生器不中断PLL,PLL继续输出时钟; ◆ IOB=1: 时钟发生器切换到旁路模式,重新启动锁 定序列过程。 16 ( (2~31) P 0~3) PLLMUL LLDIV T 1 + 输出频率= 输入频率 进入锁相状态过程:在旁路模式下, CLKMD的PLL ENABLE=1 →启动PLL→进入锁相序列: 产生输出频率, 输出与输入锁相,进入锁定模式(之前都是旁路模式)。 DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT

例8-1,TMS320VC5509A系统的晶体振荡器频率为12MHz。 通过设置DPLL,使系统时钟时钟频率为144Mz。 CLKMD.4) 解(1)原理:使DPLL工作在锁定模式: (PLL ENABLE)=1b 144MHz PLL MULTXI2MHZ 即: PLL MULT-12 PLL DIV+1 PLL DIV+1 取PLLDIV=0,PLL MULT=12,即寄存器CLKMD的位: D6D5(PLL DIV)=00b,D11~D7(PLL MULT)=12=01100b; 时钟模式寄存器(CLKMD)的其它位均取为0。 (2)汇编语言实现: MOV#0000011000010000b,pot(#1c00h) MOV #0610h,port(#1c00h) :1c00h为时钟模式寄存器(CLKMD)的地址。 17

P 1 L 44 L MHz P D LL M IV 12MHz 1 ULT = + PLL D PLL M IV UL 2 T=1 +1 解(1)原理:使DPLL工作在锁定模式: (PLL ENABLE)=1b 即: 取PLL DIV=0, PLL MULT=12, 即寄存器CLKMD的位 : D6D5(PLL DIV)=00b, D11~D7(PLL MULT)=12=01100b; 时钟模式寄存器(CLKMD)的其它位均取为0。 (2)汇编语言实现: MOV #0000 0110 0001 0000b, port(#1c00h) 或MOV #0610h, port(#1c00h) ;1c00h为时钟模式寄存器(CLKMD)的地址。 例8-1,TMS320VC5509A系统的晶体振荡器频率为12MHz。 通过设置DPLL, 使系统时钟时钟频率为144MHz。 17 (CLKMD. 4)

(3)C语言实现: (例8-1) ioport unsigned int *clkmd; CSL安装程序: clkmd=(unsigned int *)0x1c00; TMS320C55x Chip *clkmd=0x0610 头文件需包含该锁 Support Library (4)使用csl实现: 相PLL时钟库头文件 (sprc133.zip)(含 #include csl_pll.h; C5500.exe及说明文件) PLL Config Config PLL= CSL使用参考文献: 01 *iai* TMS320C55x Chip 0 *iob* Support Library API 在头文件中 Reference Guide 12 /*pllmult*/ 进行配置 SPRU433J,A) 0 *div 在C程序(通常在初始化部分)中执 行该函数,完成对DPLL的设置 PLL config(&Config._PLL)参考8.9.3节PLL config0函数 也可用PLL setFreq(Uint16mul,Uint16diW函数直接设置DPLL 18

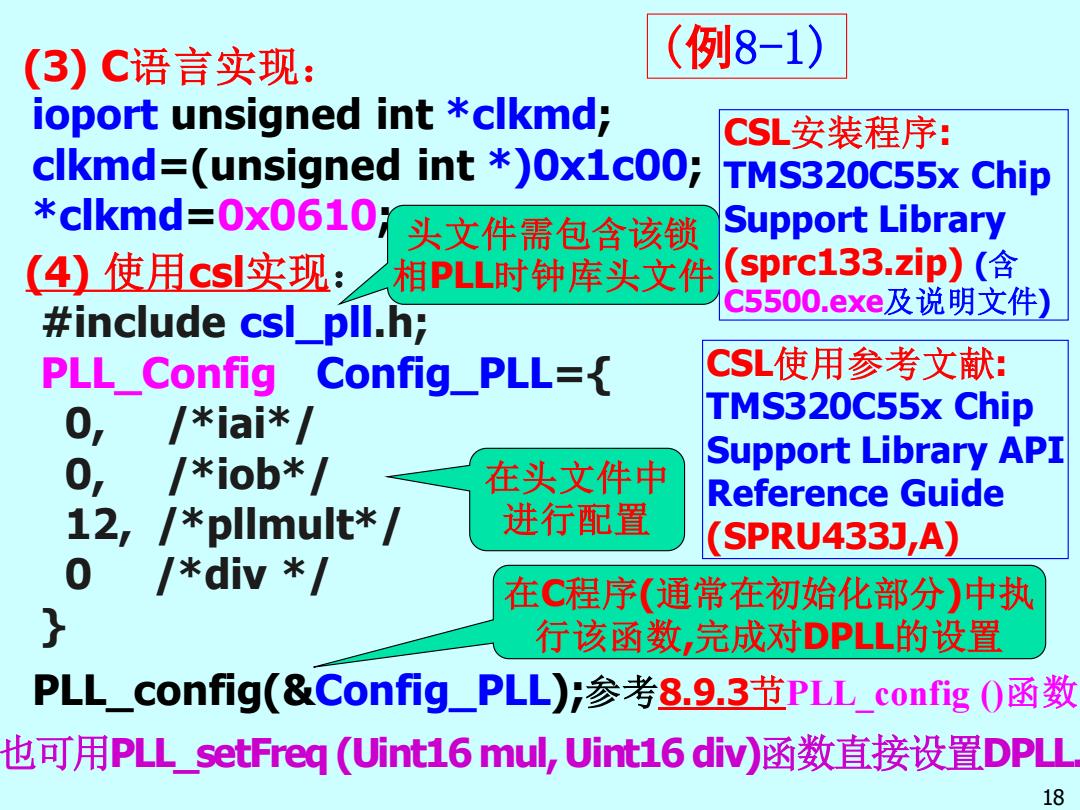

(3) C语言实现: ioport unsigned int *clkmd; clkmd=(unsigned int *)0x1c00; *clkmd=0x0610; (4) 使用csl实现: #include csl_pll.h; PLL_Config Config_PLL={ 0, /*iai*/ 0, /*iob*/ 12, /*pllmult*/ 0 /*div */ } PLL_config(&Config_PLL);参考8.9.3节PLL_config ()函数 在头文件中 进行配置 头文件需包含该锁 相PLL时钟库头文件 在C程序(通常在初始化部分)中执 行该函数,完成对DPLL的设置 (例8-1) 18 CSL安装程序: TMS320C55x Chip Support Library (sprc133.zip) (含 C5500.exe及说明文件) 也可用PLL_setFreq (Uint16 mul, Uint16 div)函数直接设置DPLL. CSL使用参考文献: TMS320C55x Chip Support Library API Reference Guide (SPRU433J,A)