2.锁定模式(LOCK mode):PLL使能 ○在锁定模式,时钟发生器输出时钟信号与输入信号保持锁相 状态。进入锁相状态过程:在旁路模式下,CLKMD.4的 PLL ENABLE=1→启动PLL→进入锁相序列:产生配置的输 出频率,输出与输入锁相,进入锁定模式(之前都是旁路模式)。 ®输出CPU时钟频率(可是输入信号的分频或倍频)由下式确定: PLL MULT2-31) 输出频率= 输入频率 PLL DIV(0~3)+1 3.Idle模式 Idle Configuration Register(ICR) ●为了降低功耗,可以加载Idle配置,执行IDLE指令后,使 DSP的时钟发生器进入Idle模式; o当时钟发生器处于Idle模式时,输出时钟停止(保持高电 平),CLKOUT引脚被拉为高电平

2.锁定模式(LOCK mode): PLL使能 ⚫在锁定模式,时钟发生器输出时钟信号与输入信号保持锁相 状态。进入锁相状态过程:在旁路模式下,CLKMD.4的 PLL ENABLE=1→启动PLL→进入锁相序列:产生配置的输 出频率,输出与输入锁相,进入锁定模式(之前都是旁路模式)。 ⚫输出CPU时钟频率(可是输入信号的分频或倍频)由下式确定: 3. Idle模式 ⚫为了降低功耗,可以加载Idle配置,执行IDLE指令后,使 DSP的时钟发生器进入Idle模式; ⚫当时钟发生器处于Idle模式时,输出时钟停止(保持高电 平), CLKOUT引脚被拉为高电平。 9 ( (2~31) P 0~3) PLL MUL LL DIV T 1 输出频率 + = 输入频率 Idle Configuration Register (ICR) DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT

表8-1时钟模式寄存器CLKMD 时钟模式寄存器CLKMD位于IO空间,地址为:1c00h 表8-1时钟模式寄存器CLKMD 位 字段 说 ■ 15 Rsvd 保图 退出Idle状态后,决定PLL如何重新获得锁相御 14 IAI 0 PLL使用与进入Idle状态之前相同的锁定设 置进行锁定,不需重新启动锁相的锁定序列。 Initialize-After-Idle 1 PLL将重新启动锁相的锁定序列过程 失锁时如何初始化P工心锁相序列过程: 0时钟发生器不中断PLL,时钟发生器仍处于锁 13 IOB 定模式(L0CK=1),PLL继续输出当前时钟; 1 Initialize-On-Break 时钟发生器切换到旁路模式(LOCK=O),PLL重 新启动锁相的锁定序列过程 12 TEST 必须保持为0 11~7 PLL MULT锁定模式下的PLL倍频值, 231 65 PLL DIV 锁定模式下的PLL分频值,03

表8-1 时钟模式寄存器CLKMD 位 字 段 说 明 15 Rsvd 保留 14 IAI 退出Idle状态后, 决定PLL如何重新获得锁相: 0 PLL使用与进入Idle状态之前相同的锁定设 置进行锁定, 不需重新启动锁相的锁定序列。 1 PLL将重新启动锁相的锁定序列过程 13 IOB 失锁时如何初始化PLL锁相序列过程: 0 时钟发生器不中断PLL,时钟发生器仍处于锁 定模式(LOCK=1),PLL继续输出当前时钟; 1 时钟发生器切换到旁路模式(LOCK=0), PLL重 新启动锁相的锁定序列过程 12 TEST 必须保持为0 11~7 PLL MULT 锁定模式下的PLL倍频值,2~31 表8-1 时钟模式寄存器CLKMD 时钟模式寄存器CLKMD位于IO空间,地址为:1c00h 10 Initialize-After-Idle Initialize-On-Break 6~5 PLL DIV 锁定模式下的PLL分频值,0~3 与输入锁相,进入锁定模式(之前都是旁路模式)

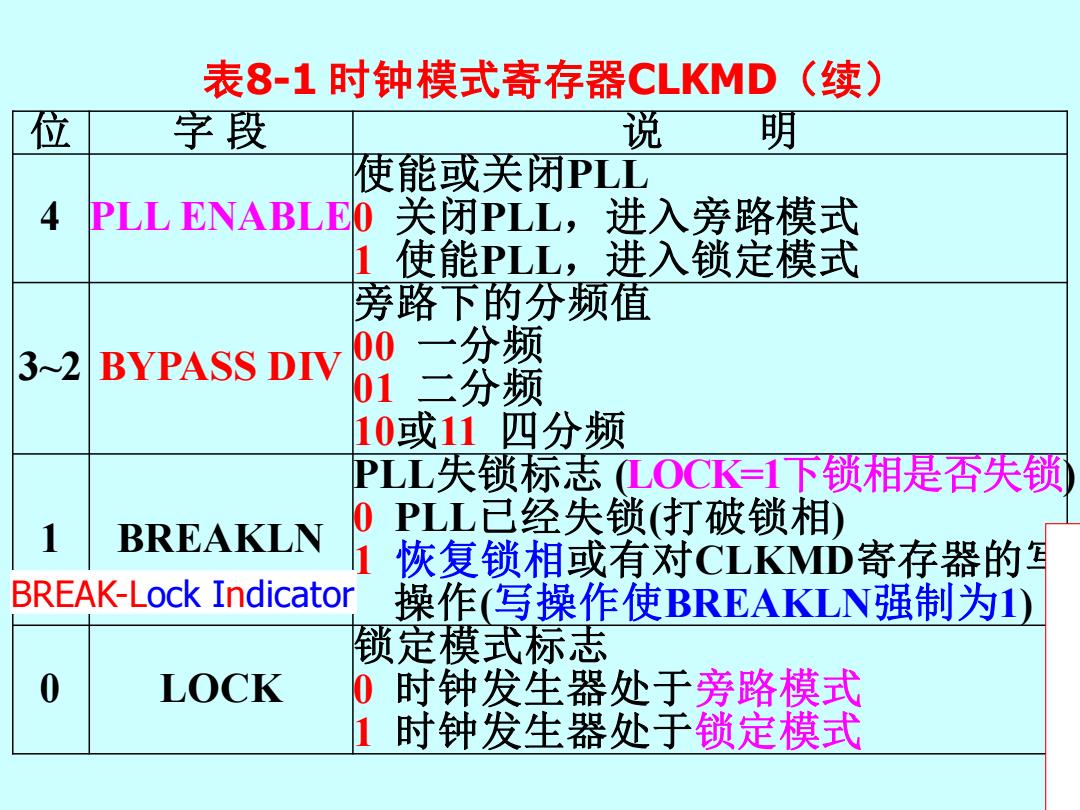

表8-1时钟模式寄存器CLKMD(续) 位 字段 说 明 使能或关闭PL工 4 PLL ENABLE0关闭PLL,进入旁路模式 1使能PLL,进入锁定模式 旁路下的分频值 3~2BYPASS DV 二分 10或11四分频 PLL失锁标志亿0CK=1下锁相是否失锁 BREAKLN 0PLL已经失锁(打破锁相) 1 恢复锁相或有对CLKMD寄存器的生 BREAK-Lock Indicator 操作(写操作使BREAKLN强制为1) 锁定模式标志 0 LOCK 0上 时钟发生器处于旁路模式 1时钟发生器处于锁定模式

表8-1 时钟模式寄存器CLKMD(续) 位 字 段 说 明 4 PLL ENABLE 使能或关闭PLL 0 关闭PLL,进入旁路模式 1 使能PLL,进入锁定模式 3~2 BYPASS DIV 旁路下的分频值 00 一分频 01 二分频 10或11 四分频 1 BREAKLN PLL失锁标志 (LOCK=1下锁相是否失锁) 0 PLL已经失锁(打破锁相) 1 恢复锁相或有对CLKMD寄存器的写 操作(写操作使BREAKLN强制为1) 0 LOCK 锁定模式标志 0 时钟发生器处于旁路模式 1 时钟发生器处于锁定模式 11 BREAK-Lock Indicator DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT

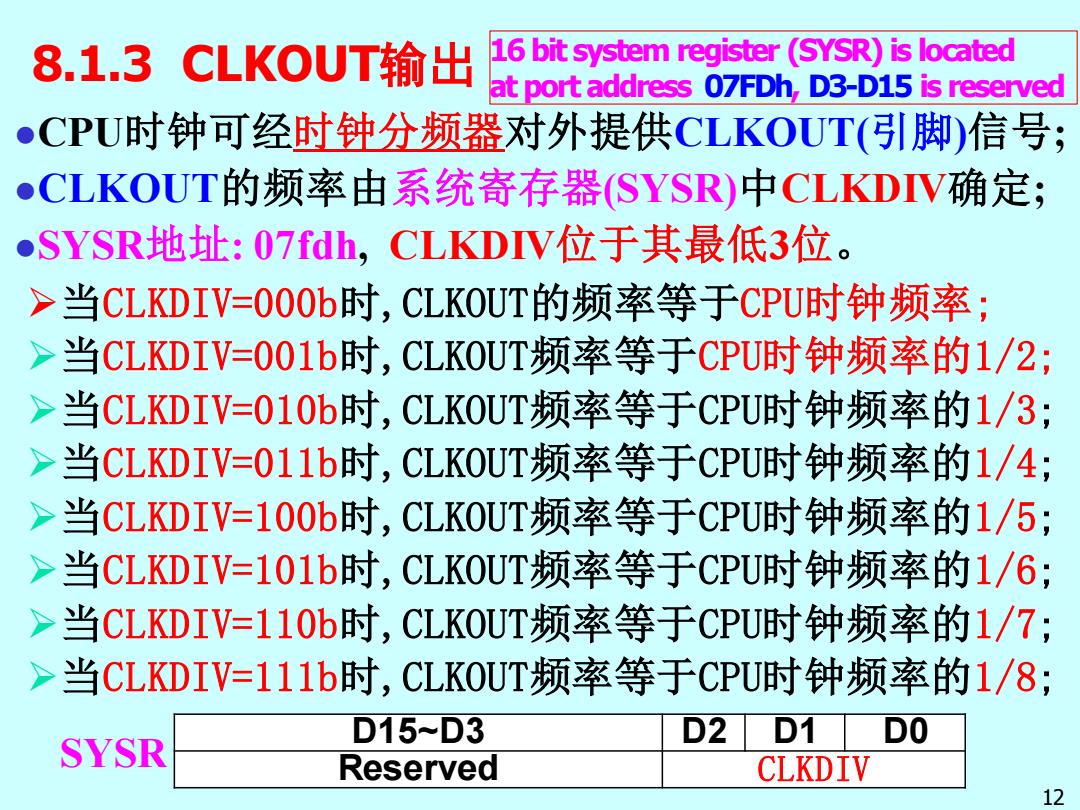

8.1.3 CLKOUT输出 16 bit system register (SYSR)is located at port address 07FDh,D3-D15 is reserved ●CPU时钟可经时钟分频器对外提供CLKOUT(引脚)信号; ●CLKOUT的频率由系统寄存器(SYSR)中CLKDIV确定; ●SYSR地址:07fdh, CLKDIV位于其最低3位。 >当CLKDIV=O00b时,CLKOUT的频率等于CPU时钟频率; > 当CLKDIV=-001b时,CLK0UT频率等于CPU时钟频率的1/2; >当CLKDIV=-010b时,CLKOUT频率等于CPU时钟频率的1/3; >当CLKDIV=011b时,CLK0UT频率等于CPU时钟频率的1/4; >当CLKDIV=100b时,CLK0UT频率等于CPU时钟频率的1/5; > 当CLKDIV=-101b时,CLK0UT频率等于CPU时钟频率的1/6; >当CLKDIV=110b时,CLK0UT频率等于CPU时钟频率的1/7; >当CLKDIV=111b时,CLK0UT频率等于CPU时钟频率的1/8; D15~D3 D2 D1 DO SYSR Reserved CLKDIV 12

8.1.3 CLKOUT输出 ⚫CPU时钟可经时钟分频器对外提供CLKOUT(引脚)信号; ⚫CLKOUT的频率由系统寄存器(SYSR)中CLKDIV确定; ⚫SYSR地址: 07fdh, CLKDIV位于其最低3位。 ➢当CLKDIV=000b时,CLKOUT的频率等于CPU时钟频率; ➢当CLKDIV=001b时,CLKOUT频率等于CPU时钟频率的1/2; ➢当CLKDIV=010b时,CLKOUT频率等于CPU时钟频率的1/3; ➢当CLKDIV=011b时,CLKOUT频率等于CPU时钟频率的1/4; ➢当CLKDIV=100b时,CLKOUT频率等于CPU时钟频率的1/5; ➢当CLKDIV=101b时,CLKOUT频率等于CPU时钟频率的1/6; ➢当CLKDIV=110b时,CLKOUT频率等于CPU时钟频率的1/7; ➢当CLKDIV=111b时,CLKOUT频率等于CPU时钟频率的1/8; 12 16 bit system register (SYSR) is located at port address 07FDh, D3-D15 is reserved D15~D3 D2 D1 D0 Reserved CLKDIV SYSR DSP时钟发生器 ÷ CLKDIV CPU时钟 CPU、外设、 其他器件 CLKIN CLKOUT

8.1.4使用要点 ●通过对时钟模式寄存器(CLKMD)的操作,可 根据需要设定时钟发生器的工作模式和输出 频率。 在设置过程中除了工作模式、分频值和倍频 值以外,还要注意其他因素对PLL的影响。 13

8.1.4 使用要点 ⚫通过对时钟模式寄存器(CLKMD)的操作, 可 根据需要设定时钟发生器的工作模式和输出 频率。 ⚫在设置过程中除了工作模式、分频值和倍频 值以外, 还要注意其他因素对PLL的影响。 13