第六章 时序逻辑电路 2)双时钟输入二进制同步可逆计数器 里 1J J C1 C1 C1 1K 1K 1K 加计数脉冲 & & CPU 减计数脉冲 CPD CP和CPD互相排斥 CPU=CP,CPD=0 CPO=CPU+CPD CPD=CP,CPU=0

(2)双时钟输入二进制同步可逆计数器 加计数脉冲 减计数脉冲 CP0= CPU+ CPD CPU和CPD互相排斥 CPU= CP,CPD= 0 CPD= CP,CPU= 0 CPU Q0 1J 1K C1 1 FF0 Q0 Q2 1J 1K C1 1 FF2 Q2 Q1 1J 1K C1 1 FF1 Q1 1 & 1 & 1 CPD

第六障 时序哭辑电路 四集成二进制同步计数器 L.集成4位二进制同步加法计数器 1074LS161和74LS163 逻辑功能示意图 引脚排列图 VcC CO Qo QQ O3 CTTLD 001020 8 161514131211109 C 74161(3) CT 74161 1234567 8 8↓↓↓↓ CR CP Do D1D2D3CT地 CR Do DI D2 D3 记住常见的引脚符号及功能,搞清楚:控制信号是低电平有 效还是高电平有效,控削信号是异步控制还是同步控制

(四) 集成二进制同步计数器 1. 集成 4 位二进制同步加法计数器 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 VCC CO Q0 Q1 Q2 Q3CTT LD CR CP D0 D1 D2 D3CTP 地 引脚排列图 逻辑功能示意图 Q0 Q1 Q2 Q3 CTT LD CO CP CTP CR D0 D1 D2 D3 1) 74LS161 和 74LS163 记住常见的引脚符号及功能,搞清楚:控制信号是低电平有 效还是高电平有效;控制信号是异步控制还是同步控制!

第六障 时序逻辑电路 74163 状态表 输 入 输 出 注 CR LD CTP CTT CP D3 D2 DI Do 23+122t121+12o+1C0 0 X × × 个 × ××X 0 0 0 0 0 清零 1 0 × X 个 d;dd do d d do 置数 1 1 1 1 个 XXX 数 1 1 0 X × × 持 1 1 X 0 X ×XX 保保 持 0 C0=CTr·000'0 74163与74161的唯一不同之处是:. 74163是同步清零,而74161是异步

74161的状态表 输 入 输 出 注 CR LD CTPCTT CP D3 D2 D1 D0 Q3 n+1 Q2 n+1 Q1 n+1 Q0 n+1CO 0 1 0 d3 d2 d1d0 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 d3 d2 d1 d0 计 数 保 持 保 持 0 清零 置数 3 2 1 0 n n n n CO CTT Q Q Q Q 74163 74163与74161的唯一不同之处是: 74163是同步清零,而74161是异步

第六障 时序逻辑电路 2) CC4520 (双4位二进制同步加法计数器) DD2CR20320220202EN2CP 0001020 16151413121110 9 CC4520 1-2 CC4520 1 234567 8 ICPIEN1O010 101031CR Vss EN CP CR 表6.2.3CC4520的状态表 输 入 输 出 异 CR EN CP Q3 03 Q*1 Qo 注 1 ¥ × 0 0 0 0 清零 0 1 ↑ 加计数 上升沿有效 清零 0 ↓ 0 加计数 下降沿有效 0 0 × 保持 0 × 1 保持

2) CC4520(双4位二进制同步加法计数器) VDD 2CR2Q32Q22Q12Q02EN2CP 1EN1Q0 1Q1 1Q1Q31CR VSS 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 Q0 Q1 Q2 Q3 EN CP CR 2 1 使能端 也可作 计数脉 冲输入 计数脉 冲输入 也可作 使能端 异 步 清 零

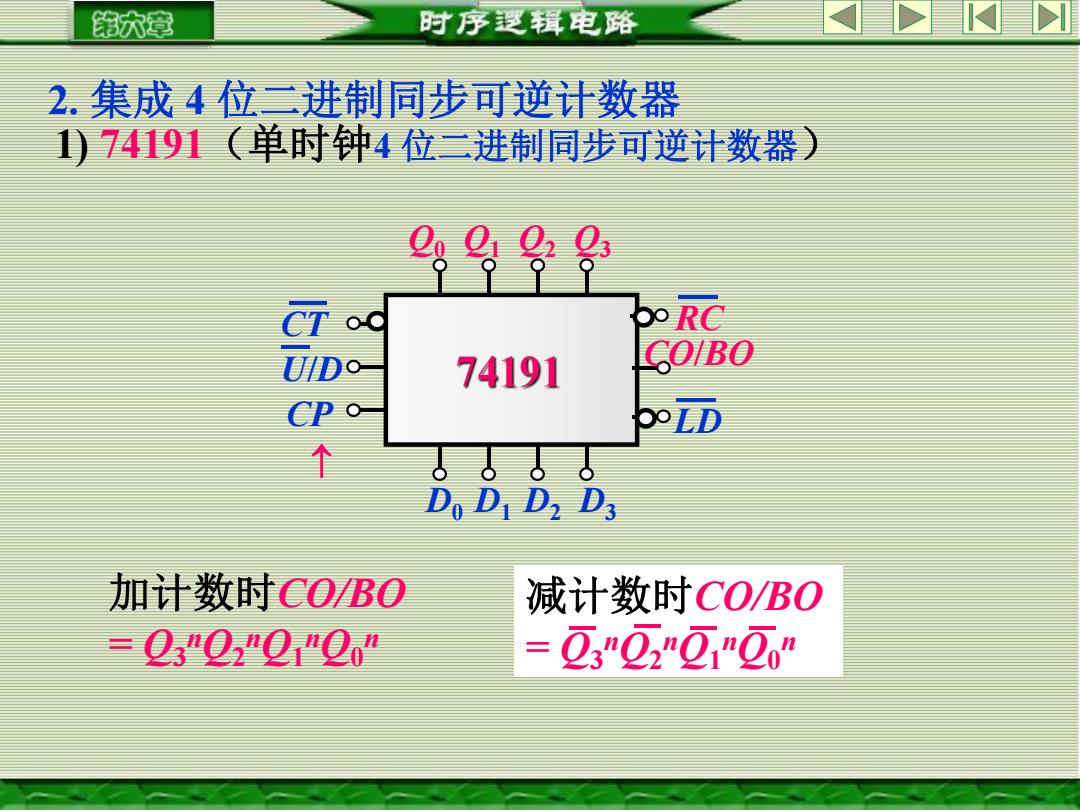

第六障 时序逻辑电路 2.集成4位二进制同步可逆计数器 1074191(单时钟4位二进制同步可逆计数器) CT oo RC UID 74191 COIBO DO DDD 加计数时COBO 减计数时COBO =0'02"0"00' 3"Q2""n

2. 集成 4 位二进制同步可逆计数器 1) 74191(单时钟4 位二进制同步可逆计数器) Q0 Q1 Q2 Q3 U/D LD CO/BO CP CT D0 D1 D2 D3 RC 加计数时CO/BO = Q3nQ2nQ1nQ0n 减计数时CO/BO = Q3nQ2nQ1nQ0n