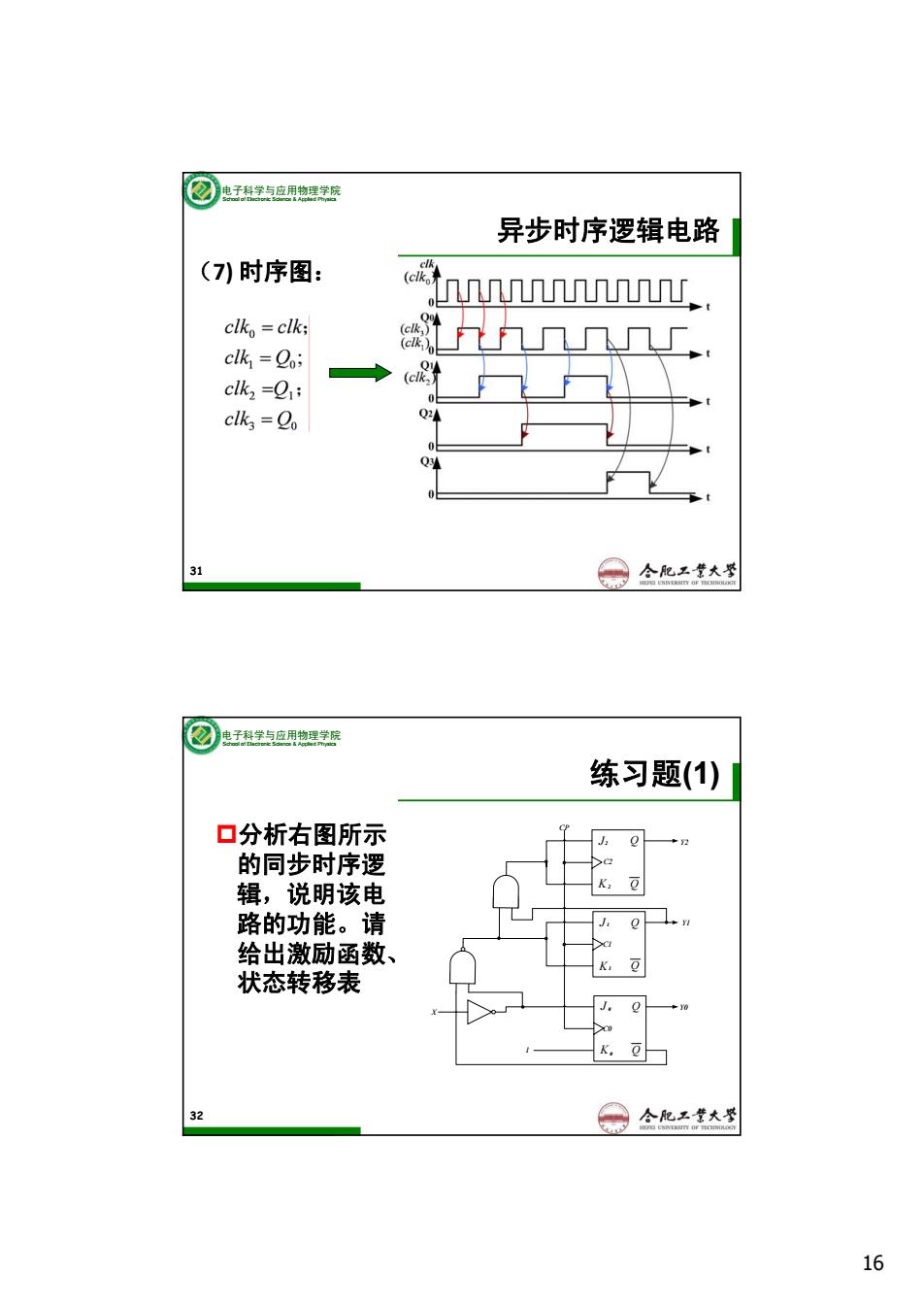

电子科学与应用物理学院 异步时序逻辑电路 (7)时序图: clk (clk。 clko clk; (clk (ck) clk =2o; clk2=21: clks=2o 31 合肥工营大举 电子科学与应用物理学院 练习题(1) 口分析右图所示 的同步时序逻 辑,说明该电 路的功能。请 给出激励函数、 K 状态转移表 32 合肥工营大举 16

16 31 电子科学与应用物理学院 School of Electronic Science & Applied Physics 异步时序逻辑电路 (7) 时序图: 32 电子科学与应用物理学院 School of Electronic Science & Applied Physics 练习题(1) 分析右图所示 的同步时序逻 辑,说明该电 路的功能。请 给出激励函数、 状态转移表 J Q Q K SET CLR J Q Q K SET CLR J Q Q K SET CLR CP Y2 Y1 Y0 1 X C2 C1 C0 2 2 1 1 0 0

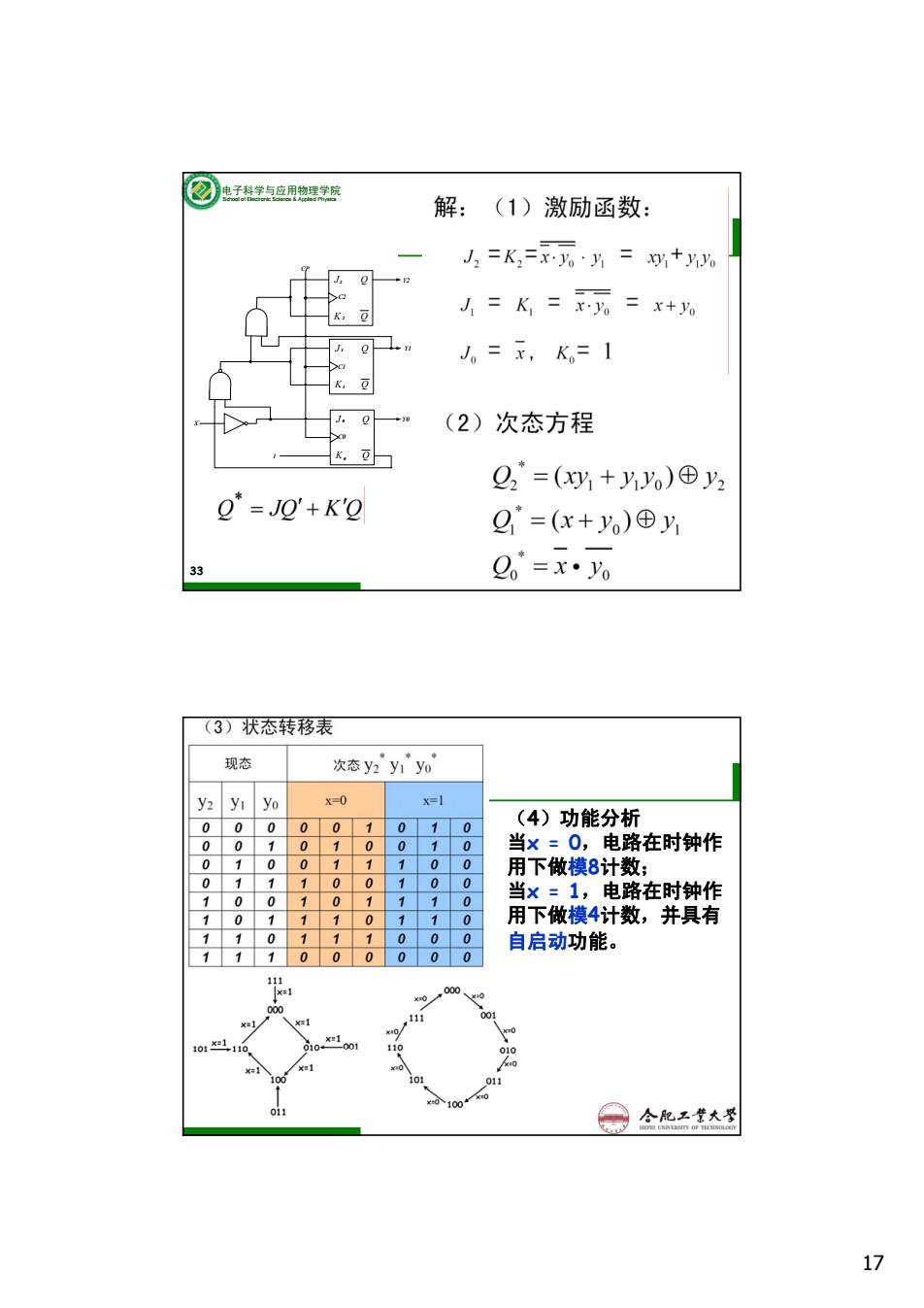

② 电子科学与应用物理学院 解:(1)激励函数: J,=K,=x。y=xy+% J=K=x 三x+yo J。=x,K=1 K,O (2)次态方程 K,可 92=(y+y)⊕2 o"=J0'+KQ 9=(x+yo)⊕y 33 9。=x·0 (3)状态转移表 现态 次态2y1y0 y2 yo X=0 x=1 0 0 0 0 01 0 1 0 (4)功能分析 0 1 0 0 当×=0,电路在时钟作 0 0 0 0 0 用下做模8计数; 0 0 0 0 0 当x=1,电路在时钟作 0 0 0 0 用下做模4计数,并具有 0 0 自启动功能。 1 1 1 0 0 0 0 0 11 000 ×=1 1 101 011 001 011 合肥工营大举 17

17 33 电子科学与应用物理学院 School of Electronic Science & Applied Physics J Q Q K SET CLR J Q Q K SET CLR J Q Q K SET CLR CP Y2 Y1 Y0 1 X C2 C1 C0 2 2 1 1 0 0 34 电子科学与应用物理学院 School of Electronic Science & Applied Physics (4)功能分析 当x = 0,电路在时钟作 用下做模8计数; 当x = 1,电路在时钟作 用下做模4计数,并具有 自启动功能

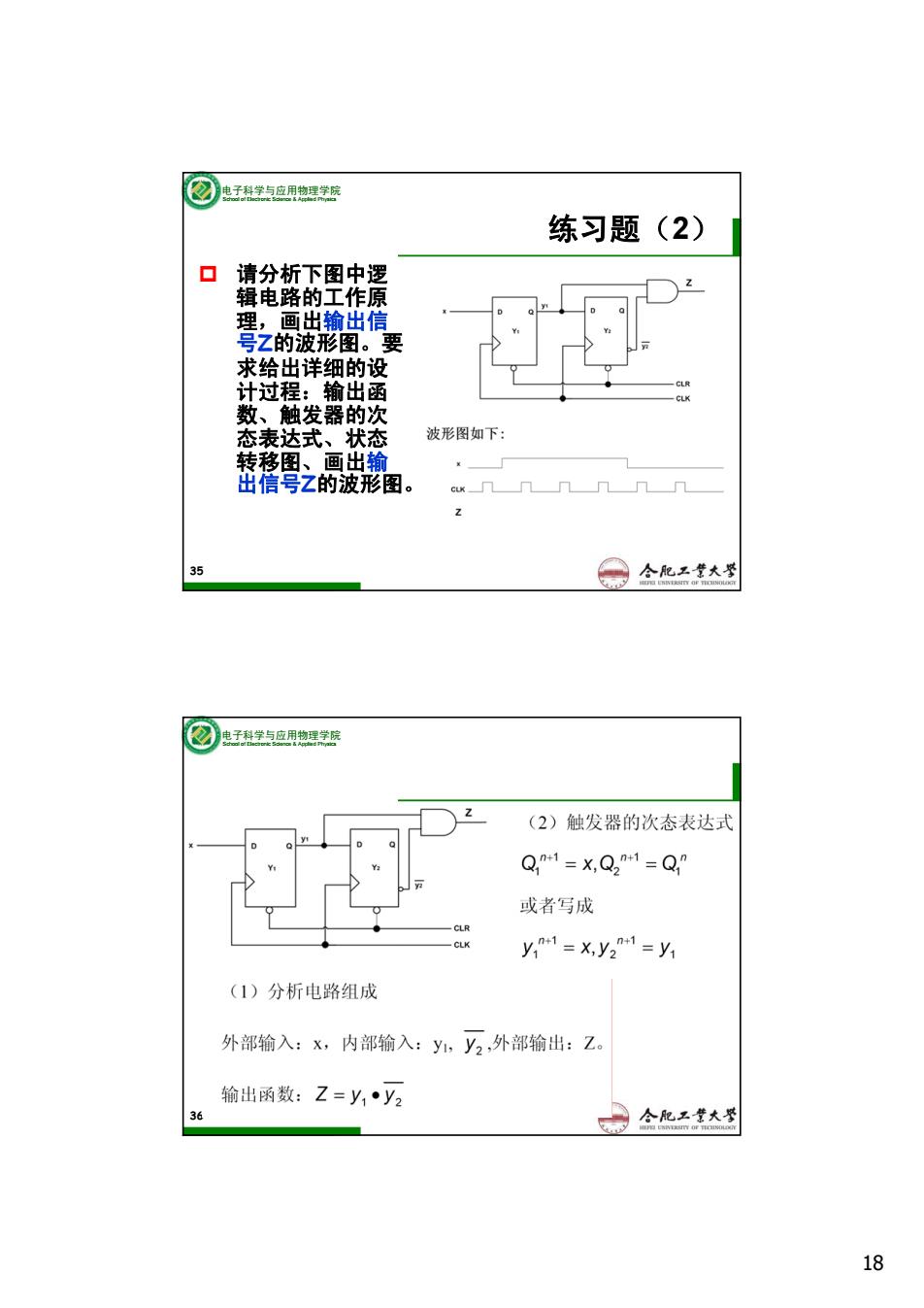

电子科学与应用物理学院 练习题(2) ▣ 请分析下图中逻 辑电路的工作原 理,画出输出信 号之的波形图。要 求给出详细的设 计过程:输出函 数、触发器的次 态表达式、状态 波形图如下: 转移图、画出输 出信号Z的波形图。 c几几几几L几几 2 35 合肥工营大举 电子科学与应用物理学院 1 (2)触发器的次态表达式 Qa1=x.Qa1=Qm 或者写成 CLR CLK y,*1=X,y21=y (1)分析电路组成 外部输入:x,内部输入:y,y2,外部输出:Z。 输出函数:Z=y,·y2 36 合肥工营大坚 18

18 35 电子科学与应用物理学院 School of Electronic Science & Applied Physics 练习题(2) 请分析下图中逻 辑电路的工作原 理,画出输出信 号Z的波形图。要 求给出详细的设 计过程:输出函 数、触发器的次 态表达式、状态 转移图、画出输 出信号Z的波形图。 36 电子科学与应用物理学院 School of Electronic Science & Applied Physics

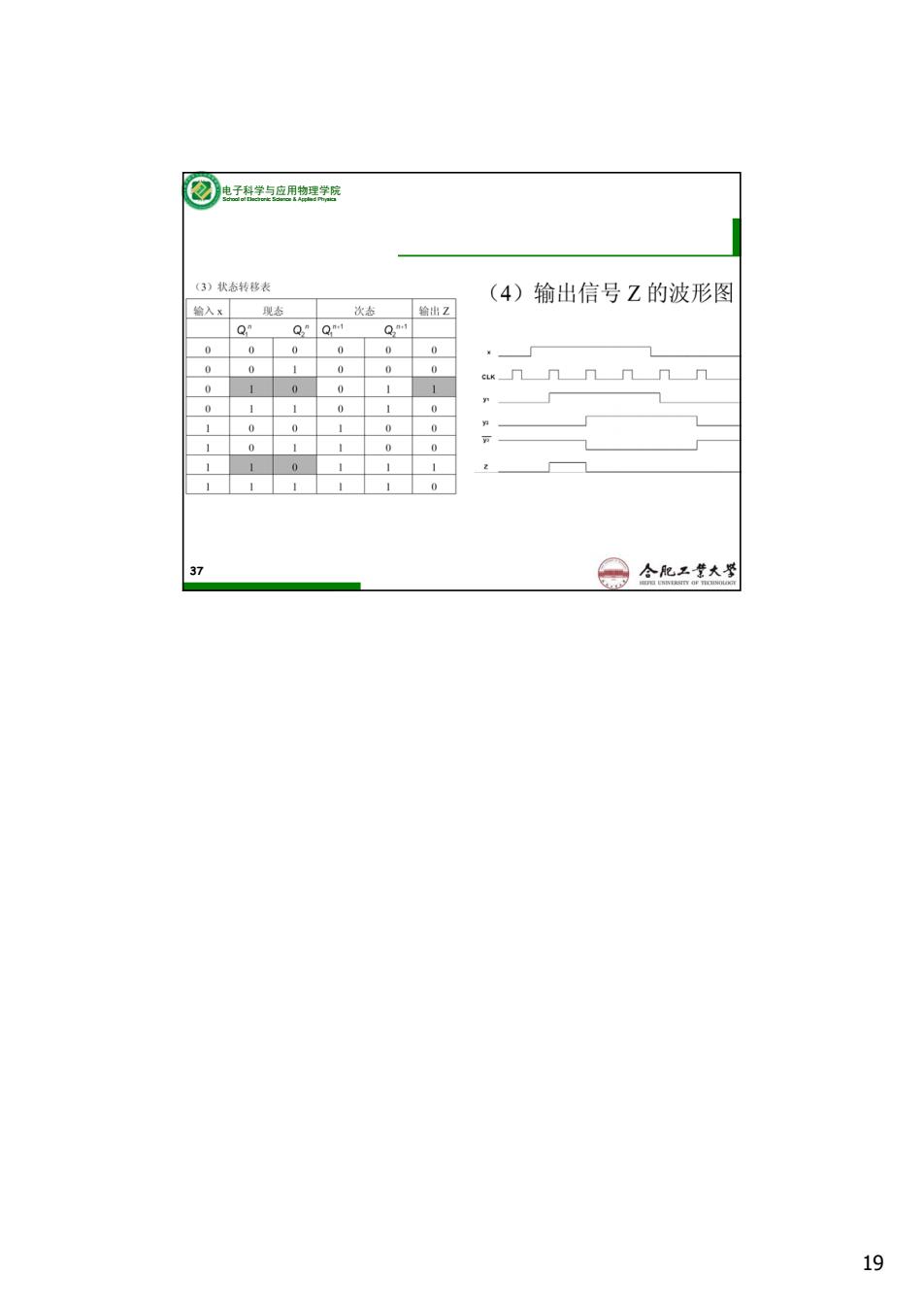

② 电子科学与应用物理学院 (3)状态转移表 (4)输出信号Z的波形图 输入x 现态 次态 输出Z Q," Q” Qn1 0 0 0 0 0 y 0 0 0 0 0 1 37 e 合肥工营大举 19

19 37 电子科学与应用物理学院 School of Electronic Science & Applied Physics

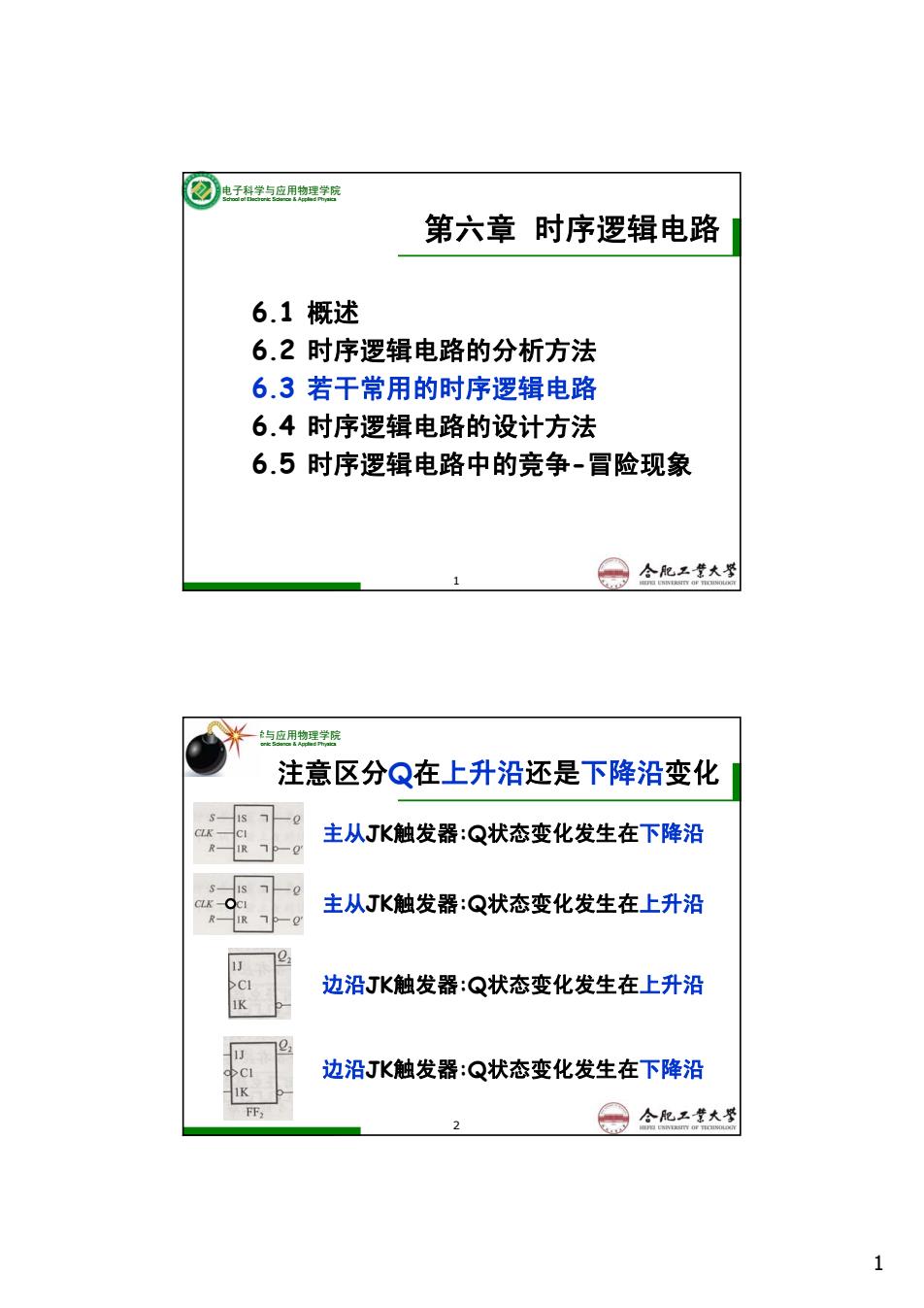

② 电子科学与应用物理学院 第六章时序逻辑电路 6.1概述 6.2时序逻辑电路的分析方法 6.3若干常用的时序逻辑电路 6.4时序逻辑电路的设计方法 6.5时序逻辑电路中的竞争-冒险现象 合肥工璧大举 与应用物理学院 注意区分Q在上升沿还是下降沿变化 CLK-CI 主从JK触发器:Q状态变化发生在下降沿 R-IR S-Is CLK-OCI 主从JK触发器:Q状态变化发生在上升沿 R-IR >C1 边沿JK触发器:Q状态变化发生在上升沿 K >C1 边沿JK触发器:Q状态变化发生在下降沿 K FF> 合肥工营大坚 2 1

1 1 电子科学与应用物理学院 School of Electronic Science & Applied Physics 第六章 时序逻辑电路 6.1 概述 6.2 时序逻辑电路的分析方法 6.3 若干常用的时序逻辑电路 6.4 时序逻辑电路的设计方法 6.5 时序逻辑电路中的竞争-冒险现象 2 电子科学与应用物理学院 School of Electronic Science & Applied Physics 注意区分Q在上升沿还是下降沿变化 主从JK触发器:Q状态变化发生在下降沿 边沿JK触发器:Q状态变化发生在下降沿 边沿JK触发器:Q状态变化发生在上升沿 主从JK触发器:Q状态变化发生在上升沿