电子科学与应用物理学院 6.3.1寄存器和移位寄存器 一、寄存器 (数码寄存器) 74LS75是由同步SR触发器构 0 成的电平触发D触发器构成的, D CLK 电路图如图6.3.1所示。由于D g 触发器是由同步SR触发器构成 D CI 的,故在时钟ck=1期间,Q g 随D改变。 D g CLK- CI e 图6.3.1 合肥工营大举 3 电子科学与气应用物理学院 ·、寄存器(数码寄存器) D 1D Q 74HC175为由CMOS边沿触发器构 >C1 成的4位寄存器,其逻辑电路如图 R 06 6.3.2所示。 D ID 0 Do~D3为并行数据输入端; >CI R CLK为寄存脉冲输入端 ID R'D为清零端 CI R 0 此寄存器为并行输入/并行输出方式。 D 在LK↑时,将Do~D3数据存入, >C1 与此前后的D状态无关,而且具有 异步置零(清零)功能。 图6.3.2 合肥五营大举 4 2

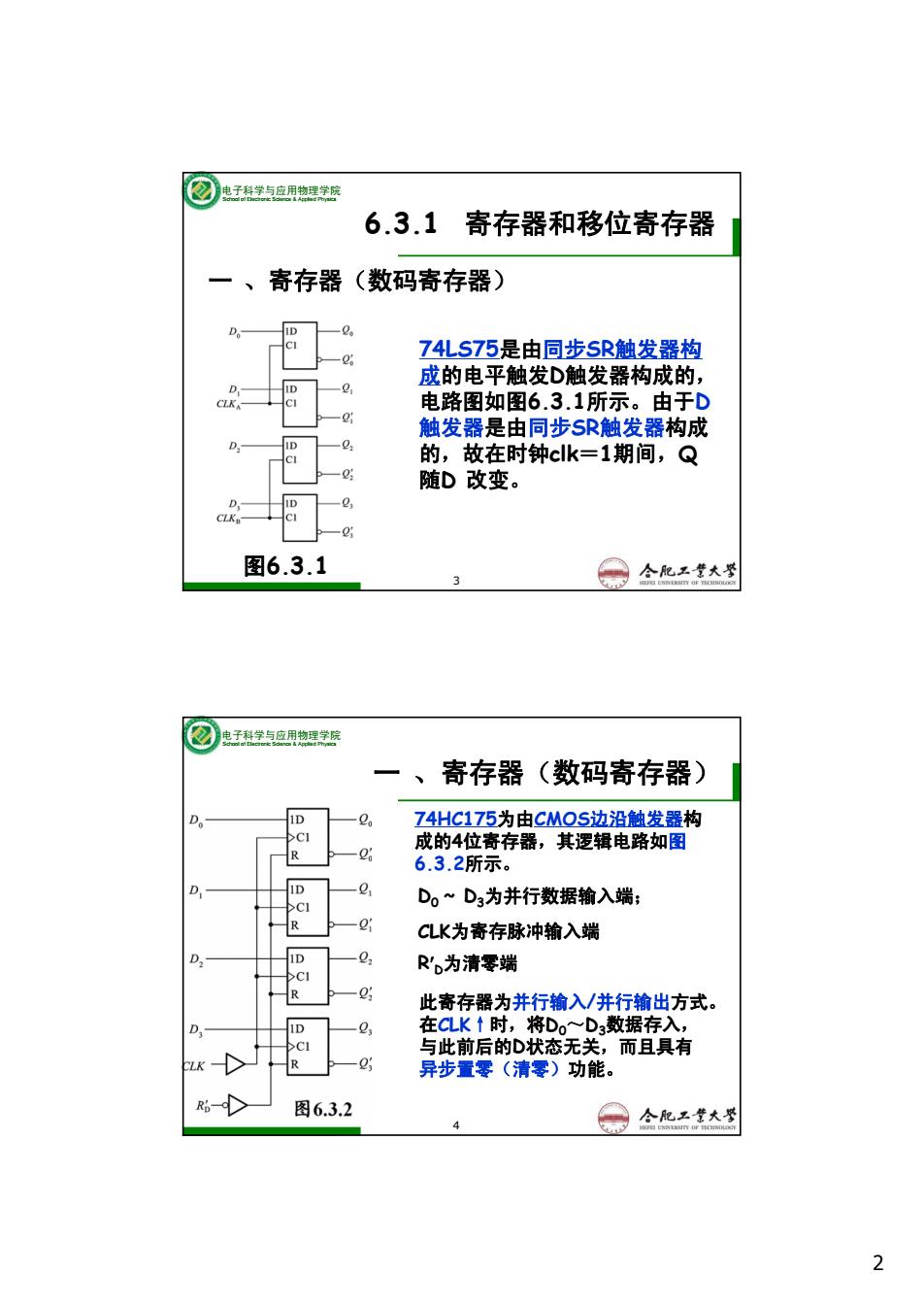

2 3 电子科学与应用物理学院 School of Electronic Science & Applied Physics 一 、寄存器(数码寄存器) 74LS75是由同步SR触发器构 成的电平触发D触发器构成的, 电路图如图6.3.1所示。由于D 触发器是由同步SR触发器构成 的,故在时钟clk=1期间,Q 随D 改变。 6.3.1 寄存器和移位寄存器 图6.3.1 4 电子科学与应用物理学院 School of Electronic Science & Applied Physics 一 、寄存器(数码寄存器) R′D为清零端 此寄存器为并行输入/并行输出方式。 在CLK↑时,将D0~D3数据存入, 与此前后的D状态无关,而且具有 异步置零(清零)功能。 74HC175为由CMOS边沿触发器构 成的4位寄存器,其逻辑电路如图 6.3.2所示。 D0 ~ D3为并行数据输入端; CLK为寄存脉冲输入端

电子科学与应用物理学院 二、移位寄存器 移位寄存器不仅具有数码存储功能,还具有移位的 功能,即在移位脉冲的作用下,依次左移或右移。故移 位寄存器除了寄存代码外,还可以实现数据的串行-并 行转换、数值运算以及数据处理等。 1.由心触发器构成的4位移位寄存器(右移): 电路如图6.3.3所示。 并 行 输 出 22 12 FF。 FF FF. FF D D ID D串行 输出 移位CLK 脉冲 图6.3.3 电子科学与应用物理学院 1.由D触发器构成的4位移位寄存器(右移) 并 行 输 出 1o. FFo FF, 醫 CLK 图6.3.3 其中D为串行输入端,Do为串行输出端,Q3~Qo为 并行输出端,CLK为移位脉冲输入端 因为触发器由传输延迟时间tpd,所以在CLK↑到达 时,各触发器按前一级触发器原来的状态翻转。 合肥工营大举 6 3

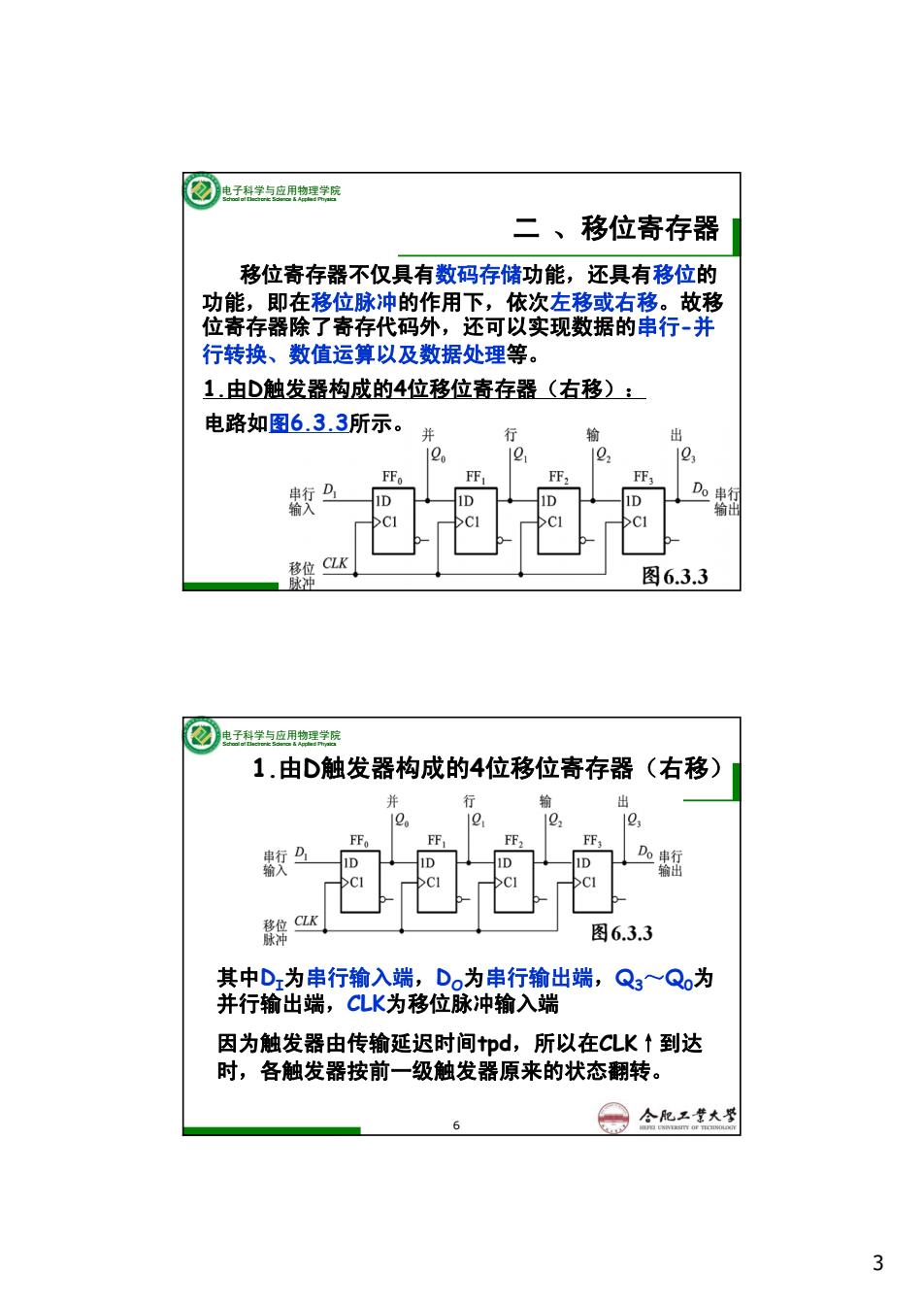

3 5 电子科学与应用物理学院 School of Electronic Science & Applied Physics 二 、移位寄存器 移位寄存器不仅具有数码存储功能,还具有移位的 功能,即在移位脉冲的作用下,依次左移或右移。故移 位寄存器除了寄存代码外,还可以实现数据的串行-并 行转换、数值运算以及数据处理等。 1.由D触发器构成的4位移位寄存器(右移): 电路如图6.3.3所示。 6 电子科学与应用物理学院 School of Electronic Science & Applied Physics 1.由D触发器构成的4位移位寄存器(右移) 其中DI为串行输入端,DO为串行输出端,Q3~Q0为 并行输出端,CLK为移位脉冲输入端 因为触发器由传输延迟时间tpd,所以在CLK↑到达 时,各触发器按前一级触发器原来的状态翻转

② 电子科学与应用物理学院 1.由D触发器构成的4位移位寄存器(右移) e 矊 图6.3.3 其状态表为: ck的魔序输入DrQQ1Q2Q3 0 Q000 0 2 5 0 6 0 0 0 合肥工营大举 电子科学与应用物理学院 1.由D触发器构成的4位移位寄存器(右移) 波形图 ◆ck 功能: 风凡风风风→ 代码的串行-并行转换 宜地體 数据的并行-串行转换 仑肥工营大举 4

4 7 电子科学与应用物理学院 School of Electronic Science & Applied Physics 1.由D触发器构成的4位移位寄存器(右移) 其状态表为: 8 电子科学与应用物理学院 School of Electronic Science & Applied Physics 1.由D触发器构成的4位移位寄存器(右移) 波形图 功能: 代码的串行‐并行转换 数据的并行‐串行转换

电子科学与应用物理学院 2.由丁K触发器构成的移位寄存器 电路如图6.3.4所示,其分析原理同上,不同的 是JK触发器的寄存是在移位脉冲的下降沿发生的。 并行输出 LSB 02 O3 MSB DI Do 串行输 串行输 出 CLK 移位 脉冲 图6.3.4用 成的移位寄存器 丁、K反向连接在一起,是D触发器 合肥工营大举 电子科学与应用物理学院 3.双向移位寄存器74LS194A (1)逻辑图形符号及功能表: 如图6.3.5所示。 DR一数据右移串行输入端 R'DS1S0工作状态 0x x 置零 DIR DO DI D:D3 DIL 74LS194A 保持 D一数据左移串行输入端 右移 0o 01 02 03 1 左移 D~D3一数据并行输入端 1 1并行输入 (a)逻辑图形符号 (b)功能表 51、S0一工作状态控制端 图6.3.5双向移位寄存器741S194的逻辑符号及功能表 Q0~Q3一数据并行输出端 10 合肥工营大举 5

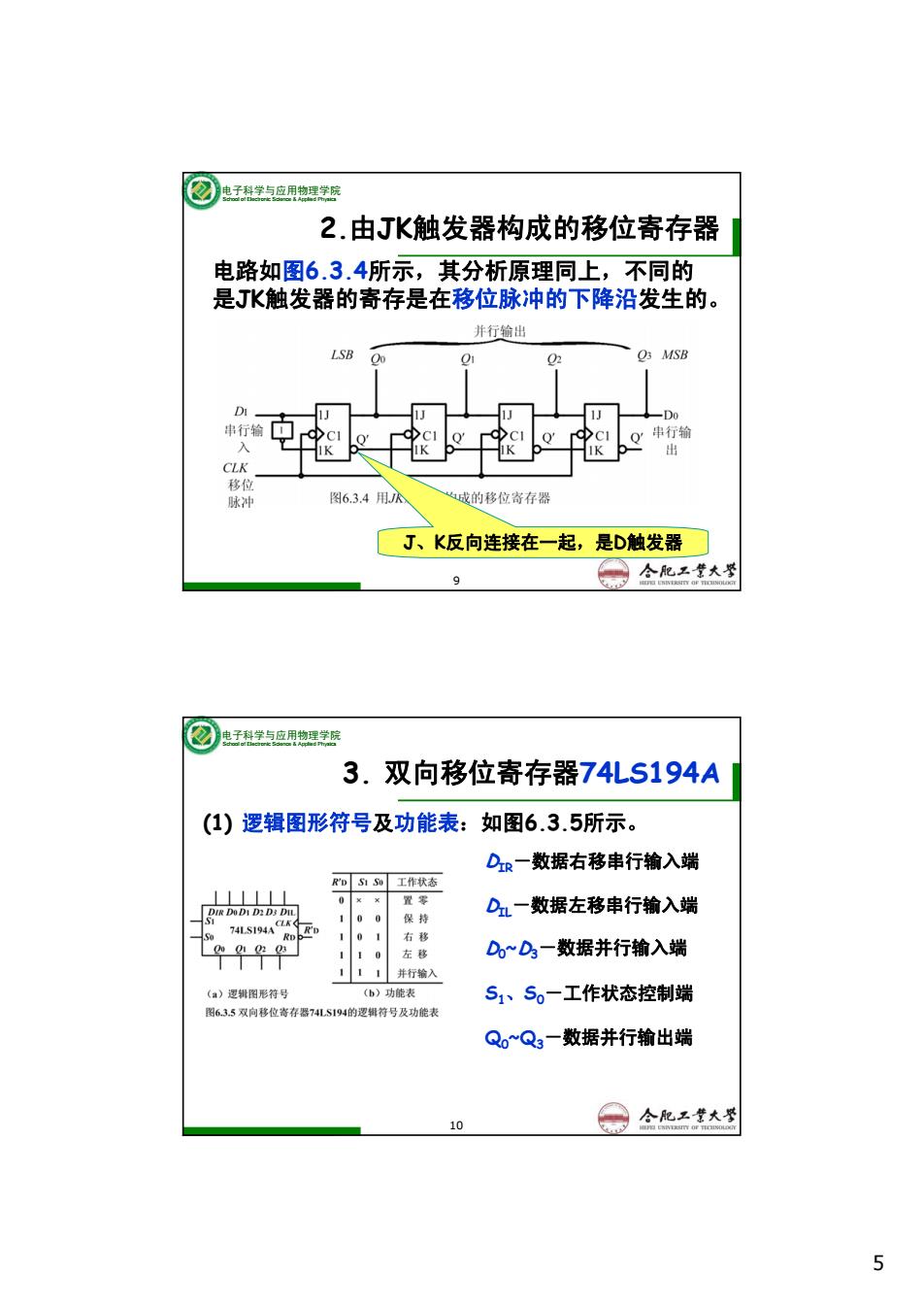

5 9 电子科学与应用物理学院 School of Electronic Science & Applied Physics 2.由JK触发器构成的移位寄存器 电路如图6.3.4所示,其分析原理同上,不同的 是JK触发器的寄存是在移位脉冲的下降沿发生的。 J、K反向连接在一起,是D触发器 10 电子科学与应用物理学院 School of Electronic Science & Applied Physics 3. 双向移位寄存器74LS194A (1) 逻辑图形符号及功能表:如图6.3.5所示。 DIR-数据右移串行输入端 DIL-数据左移串行输入端 D0~D3-数据并行输入端 Q0~Q3-数据并行输出端 S1、S0-工作状态控制端

电子科学与应用物理学院 器件实例:74L5194A, 左/右移,并行输入,保持,异步置零等功能 并行输入 00660066666006 R'D 工作状态 0 置零 CLK- 0 保 R后 0 右 左移 井行输出 1 并行输入 合肥工营大举 11 电子科学与应用物理学院 通过控制SS。 D S 就可以选择194的工作状态 Se1=SS621+SS。·2+SS622+S,SD Ron =Sou 2,*=Se U R S1 So 工作状态 D ORR 0X X 置零 Dik Do DID2 D:Dn 1 00 保持 S1 74LS194ACLK 1 01 右移 Q。QQ2Q1 1 10 左移 11 1 并行输入 12 仑肥工营大坚 6

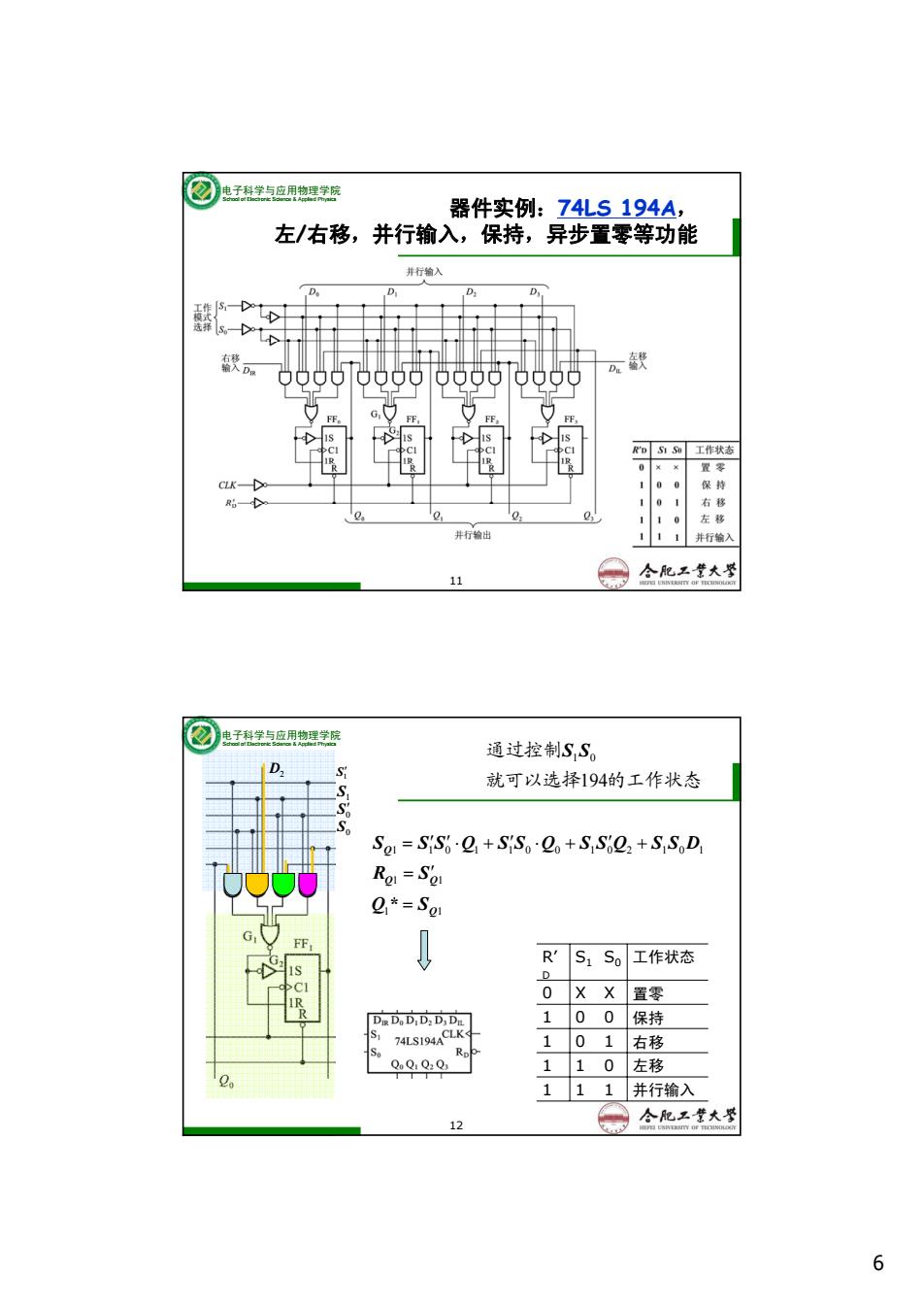

6 11 电子科学与应用物理学院 School of Electronic Science & Applied Physics 器件实例:74LS 194A, 左/右移,并行输入,保持,异步置零等功能 12 电子科学与应用物理学院 School of Electronic Science & Applied Physics S1 S0 S1 ′ S0 ′ 1 1 1 1 1 1 0 1 1 0 0 1 0 2 1 0 1 Q Q Q Q Q S R S S S S Q S S Q S S Q S S D = = ′ = ′ ′ ⋅ + ′ ⋅ + ′ + * 就可以选择 的工作状态 通过控制 194 S1S0 1 1 1 并行输入 1 1 0 左移 1 0 1 右移 1 0 0 保持 0 X X 置零 R’ S1 S0 工作状态 D D2