例:用四位二进制并行加法器设计一个用余3 码表示的一位十进制数加法器。 解:余3码相加时无进位,结果要减3;有进 位,结果要加3。减3(0011)可以变为加 13(1101)

例: 用四位二进制并行加法器设计一个用余3 码表示的一位十进制数加法器。 解: 余3码相加时无进位,结果要减3;有进 位,结果要加3。减3(0011)可以变为加 13(1101)

和数余3码 F4 F3 F2 F1 FC4 Co A4 A3 A2 A B4 B3 B2 B 1 F4 F3 F2 F1 FC4 I C0进位输入 A4 A3 A2 A Ba B3 B2 B1 被加数余3码 加数余3码

A4 A3 A2 A1 B4 B3 B2 B1 F4 F3 F2 F1 和数余3码 FC4 C0 “ 1” A4 A3 A2 A1 B4 B3 B2 B1 F4 F3 F2 F1 FC4 C0 被加数余3码 加数余3码 1 进位输入 I II

例:用四位二进制并行加法器设计一位 8421BCD码十进制数加法器。 解:8421BCD码相加时有进位或出现冗余码 时,结果要加6调整

例: 用四位二进制并行加法器设计一位 8421BCD码十进制数加法器。 解: 8421BCD码相加时有进位或出现冗余码 时,结果要加6调整

和数8421BCD码 F4 F3 F2 F1 FC4 A4 A3 A2 A B4 B3 B2 B F4 F3 F2 F1 FC4 进位输入 1 A4 A3 A2 A B4 B3 B2 B 被加数8421BCD码 加数8421BCD码

A4 A3 A2 A1 B4 B3 B2 B1 F4 F3 F2 F1 和数8421BCD码 FC4 C0 “1” A4 A3 A2 A1 B4 B3 B2 B1 F4 F3 F2 F1 FC4 C0 被加数8421BCD码 加数8421BCD码 进位输入 I II & & & &

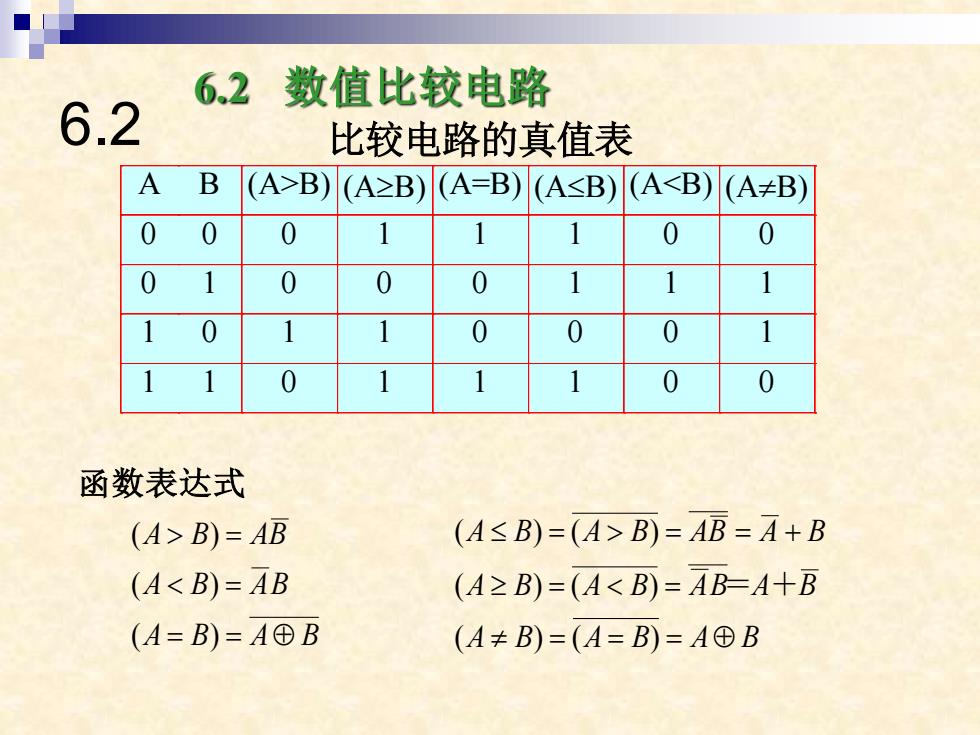

6.2数值比较电路 6.2 比较电路的真值表 A B (A>B)(A≥B)(A=B)(A≤B) (A<B)(A+B) 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 0 0 1 0 0 函数表达式 (A>B)=AB (A≤B)=(A>B)=AB=A+B (A<B)=AB (A≥B)=(A<B)=AB=A十B (A=B)=A①B (A≠B)=(A=B)=A⊕B

比较电路的真值表 A B (A>B) (AB) (A=B) (AB) (A<B) (AB) 0 0 0 1 1 1 0 0 0 1 0 0 0 1 1 1 1 0 1 1 0 0 0 1 1 1 0 1 1 1 0 0 A B A B A B AB A B AB = = = = ( ) ( ) ( ) 函数表达式 A B A B A B A B A B AB A B A B A B AB A B = = = = = = = = + ( ) ( ) ( ) ( ) ( ) ( ) = + 6.2 数值比较电路 6.2