第五章异步时序 逻辑电路

第五章 异步时序 逻辑电路

⑤1异步时序逻辑电路的特点及模型 1.同步时序逻辑电路的特点 •各触发器的时钟端全部连接在一起,并接在系 统时钟端; •只有当时钟脉冲到来时,电路的状态才能改变, •改变后的状态将一直保持到下一个时钟脉冲 的到来,此时无论外部输入x有无变化; •状态表中的每个状态都是稳定的

5.1 异步时序逻辑电路的特点及模型 1. 同步时序逻辑电路的特点 •各触发器的时钟端全部连接在一起,并接在系 统时钟端; •只有当时钟脉冲到来时,电路的状态才能改变; •改变后的状态将一直保持到下一个时钟脉冲 的到来,此时无论外部输入x有无变化; •状态表中的每个状态都是稳定的。 5.1

2.异步时序逻辑电路的特点 ·电路中除可以使用带时钟的触发器外,还可以 使用不带时钟的触发器和延迟元件作为存储元 件; •电路中没有统一的时钟; 电路状态的改变由外部输入的变化直接引起

2. 异步时序逻辑电路的特点 • 电路中除可以使用带时钟的触发器外,还可以 使用不带时钟的触发器和延迟元件作为存储元 件; •电路中没有统一的时钟; •电路状态的改变由外部输入的变化直接引起

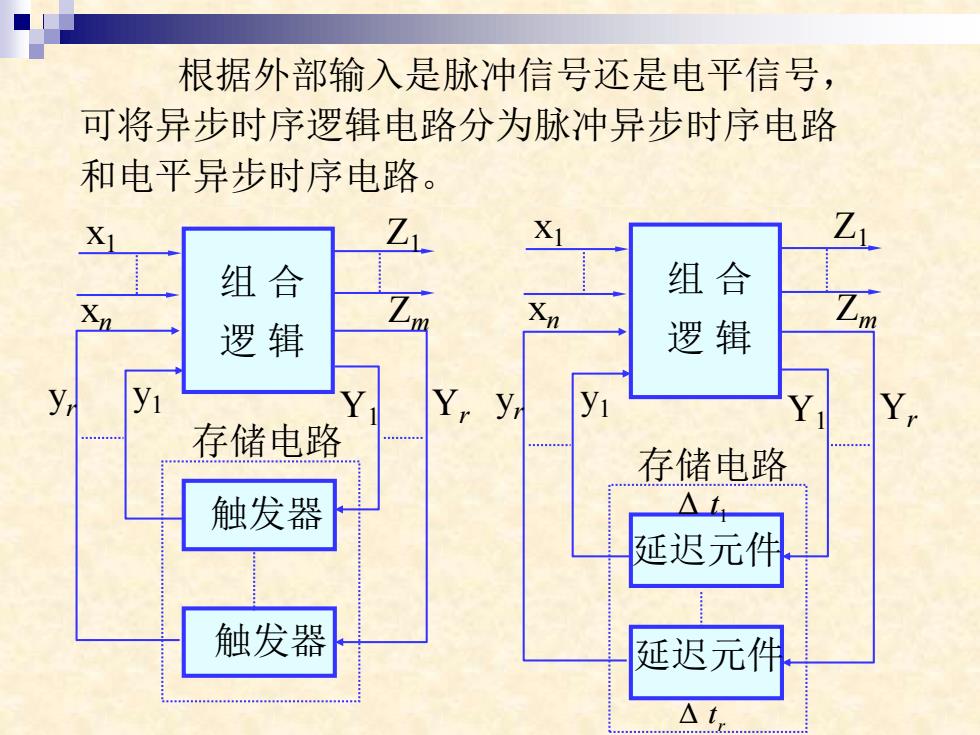

根据外部输入是脉冲信号还是电平信号, 可将异步时序逻辑电路分为脉冲异步时序电路 和电平异步时序电路。 X Z X Z 组合 组合 逻辑 m 逻辑 Y Y 存储电路 存储电路 触发器 △t4 延迟元件 触发器 延迟元件 △t

组 合 逻 辑 触发器 触发器 x1 Z1 y1 Y1 Yr yr xn Zm 存储电路 组 合 逻 辑 延迟元件 x1 Z1 y1 Y1 Yr yr xn Zm 存储电路 延迟元件 Δ 1 t r Δ t 根据外部输入是脉冲信号还是电平信号, 可将异步时序逻辑电路分为脉冲异步时序电路 和电平异步时序电路

5,2脉冲异步时序逻辑电路 对输入脉冲信号的两点限制: ·在两个或两个以上的输入线上不允许同时出现 脉冲信号; ·第二个输入脉冲的到达,必须在第一个输入脉 冲所引起的整个电路响应结束之后

5.2 脉冲异步时序逻辑电路 对输入脉冲信号的两点限制: • 在两个或两个以上的输入线上不允许同时出现 脉冲信号; • 第二个输入脉冲的到达,必须在第一个输入脉 冲所引起的整个电路响应结束之后。 5.2