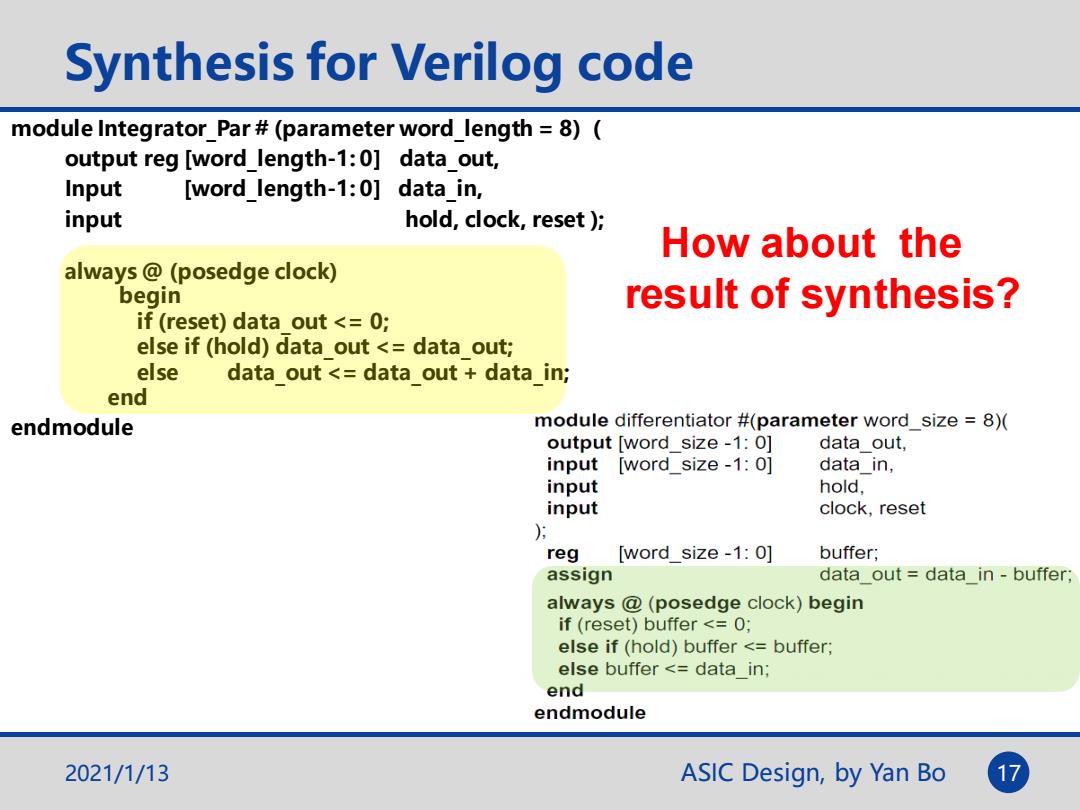

Synthesis for Verilog code module Integrator Par #(parameter word length =8)( output reg [word_length-1:0]data_out, Input [word_length-1:0]data in, input hold,clock,reset ) How about the always @(posedge clock) begin result of synthesis? if (reset)data out <=0; else if (hold)data out <data out; else data out <=data out data in; end endmodule module differentiator #(parameter word_size =8)( output [word size-1:0] data out. input [word_size-1:0] data in, input hold. input clock,reset ) reg [word_size-1:0] buffer; assign data out data in-buffer; always @(posedge clock)begin if(reset)buffer <=0; else if(hold)buffer <buffer; else buffer <data_in; end endmodule 2021/1/13 ASIC Design,by Yan Bo

ASIC Design, by Yan Bo Synthesis for Verilog code 2021/1/13 17 module Integrator_Par # (parameter word_length = 8) ( output reg [word_length-1: 0] data_out, Input [word_length-1: 0] data_in, input hold, clock, reset ); always @ (posedge clock) begin if (reset) data_out <= 0; else if (hold) data_out <= data_out; else data_out <= data_out + data_in; end endmodule How about the result of synthesis?

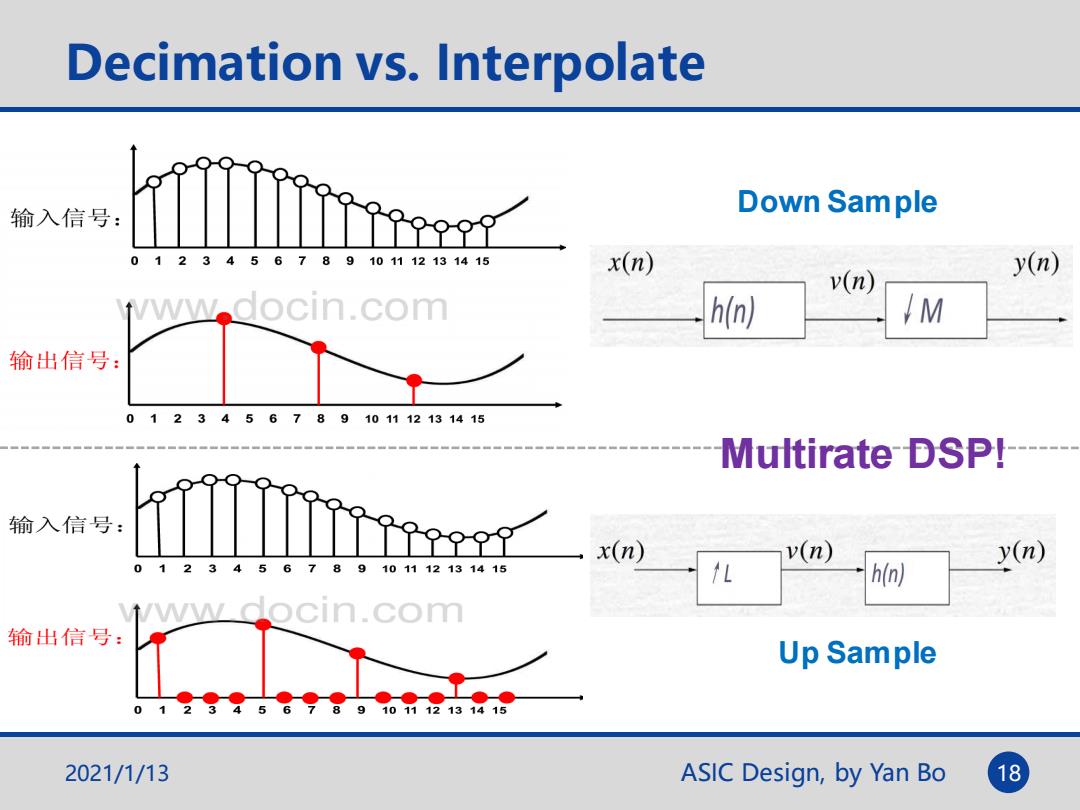

Decimation vs.Interpolate ● 输入信号: Down Sample 23456789101112131415 x(n) y(n) v(n) www.docin.com h(n) IM 输出信号: 0 123 5 6789101112131415 Multirate DSP! 输入信号: 久之 x(n) v(n) 0123456789101112131415 L h(n) y(n) wwwdocin.com 输出信号: Up Sample 01 2021/1/13 ASIC Design,by Yan Bo 18

ASIC Design, by Yan Bo Decimation vs. Interpolate 2021/1/13 18 Down Sample Up Sample Multirate DSP!

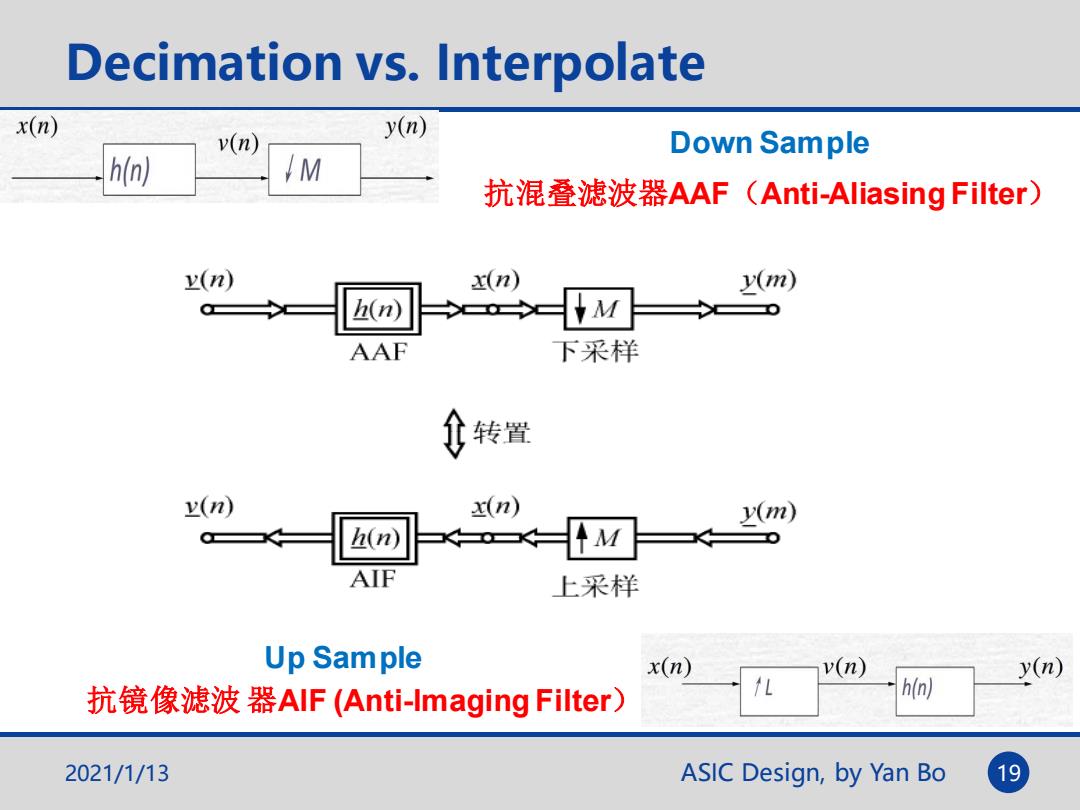

Decimation vs.Interpolate x(n) y(n) v(n) Down Sample h(n) /M 抗混叠滤波器AAF(Anti-Aliasing Filter) v(n x(n) h(n) M m) AAF 下采样 转置 (n) x(n) y(m) h(n) -=M AIF 上采样 Up Sample x(n) v(n) h(n) y(n) 抗镜像滤波器AIF(Anti-maging Filter). L 2021/1/13 ASIC Design,by Yan Bo 19

ASIC Design, by Yan Bo Decimation vs. Interpolate 2021/1/13 19 Down Sample Up Sample 抗镜像滤波 器AIF (Anti-Imaging Filter) 抗混叠滤波器AAF(Anti-Aliasing Filter)

Decimation module Decimator_1#(parameter word_length =8)( output reg [word_length-1:0 data_out, input [word_length-1:0 data_in, input hold,clock,reset); always @(posedge clock) if (reset)data_out <=0; else if (hold)data_out <data_out; 抽取因子M=? else data_out <data_in; 145 155 165 175 185t endmodule reset clock hold data_in70] 494a46404d4起405051525☒545565758595a5b5c data_ou] 28 58 2021/1/13 ASIC Design,by Yan Bo 20

ASIC Design, by Yan Bo Decimation 20 module Decimator_1 # (parameter word_length = 8)( output reg [word_length-1: 0 ] data_out, input [word_length-1: 0 ] data_in, input hold, clock, reset); always @ (posedge clock) if (reset) data_out <= 0; else if (hold) data_out <= data_out; else data_out <= data_in; endmodule 抽取因子M =? 2021/1/13

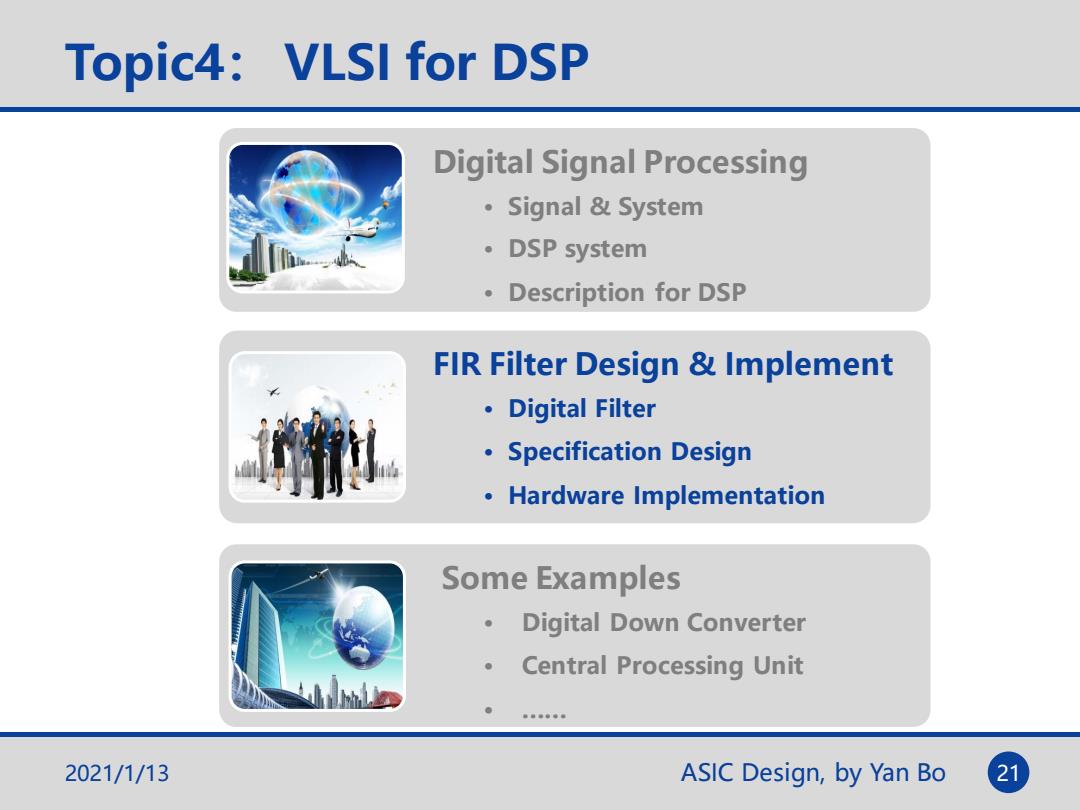

Topic4:VLSI for DSP Digital Signal Processing ·Signal&System 。DSP system ·Description for DSP FIR Filter Design Implement ·Digital Filter Specification Design Hardware Implementation Some Examples Digital Down Converter 。 Central Processing Unit h国 2021/1/13 ASIC Design,by Yan Bo 21

ASIC Design, by Yan Bo Topic4: VLSI for DSP Digital Signal Processing • Signal & System • DSP system • Description for DSP FIR Filter Design & Implement • Digital Filter • Specification Design • Hardware Implementation Some Examples • Digital Down Converter • Central Processing Unit • …… 2021/1/13 21