Causal LTI DSP System by LCCDE A general Nth-order Linear Constant-Coefficient Difference/ Differential Equation: M ∑a,[n-k]=∑b,xn-k] k=0 k=0 Recursive equation for LCCDE: avyIn-N]+av-1yIn-(N-1)]+..+ayIn-1]+aoy[n] =bwx[n-M]+bM-[n-(M-1)]+…+bx[n-1]+bx[n] Solution for LCCDE: xIn-k] Nonrecursive equation (N=0) k=0a0 系统函数h(n) M nl=∑b[n-k]-∑a[n-k] Recursive equation (N>=1) k=0 k= 2021/1/13 ASIC Design,by Yan Bo 12

ASIC Design, by Yan Bo Causal LTI DSP System by LCCDE 2021/1/13 12 = = − = − M k k N k k a y n k b x n k 0 0 [ ] [ ] A general Nth-order Linear Constant-Coefficient Difference/ Differential Equation: [ ] [ ( 1) ] [ 1] [ ] [ ] [ ( 1) ] [ 1] [ ] 1 1 0 1 1 0 b x n M b x n M b x n b x n a y n N a y n N a y n a y n M M N N = − + − − + + − + − + − − + + − + − − Recursive equation for LCCDE: Solution for LCCDE: = = − M k k x n k a b y n 0 0 [ ] [ ] Nonrecursive equation (N=0) = = = − − − N k k M k k y n b x n k a y n k 0 1 [ ] [ ] [ ] Recursive equation (N>=1) 系统函数h(n)

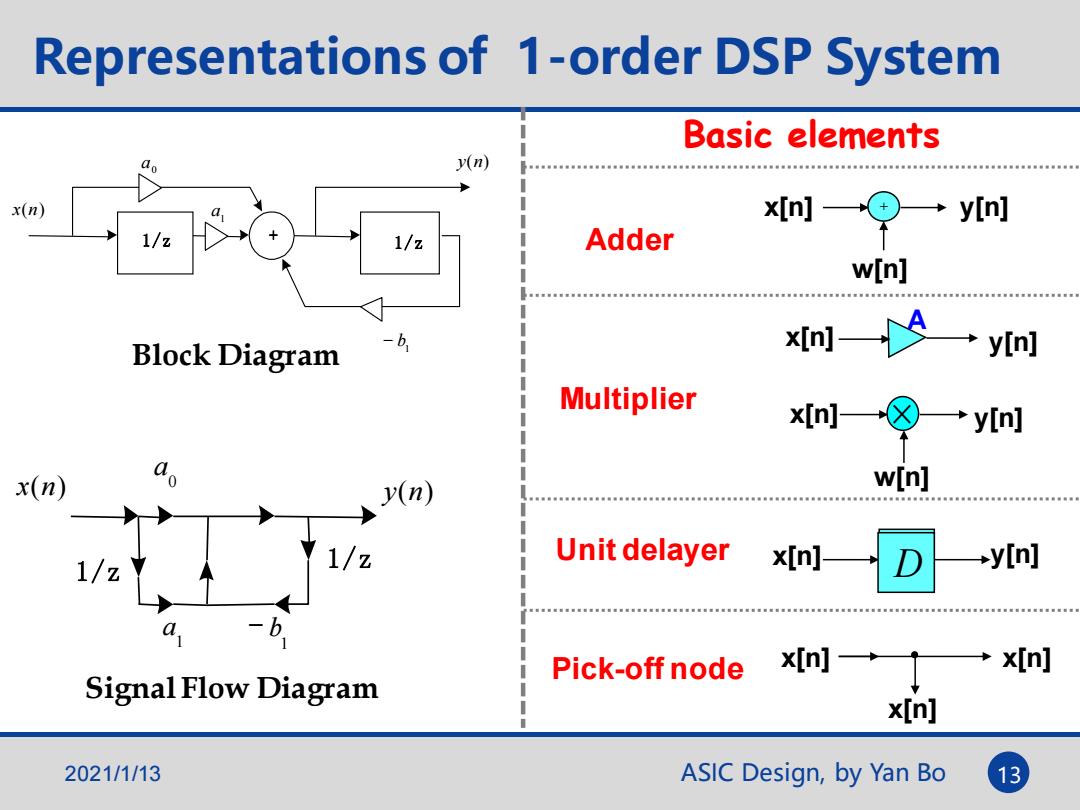

Representations of 1-order DSP System Basic elements y(n) x(n) x[n] y[n] 1/z 1/z Adder w[n] Block Diagram y[n] Multiplier xn&一→yn x(n) w[n] (n) 1 1/z Unit delayer x[n] D +y[n] Pick-off node x[n] →xn Signal Flow Diagram x[n] 2021/1/13 ASIC Design,by Yan Bo 13

2021/1/13 ASIC Design, by Yan Bo Representations of 1-order DSP System + 1/z 1/z x(n) 0 a 1 − b y(n) Block Diagram 1 a x(n) y(n) 1/z 1/z 0 a 1 a 1 − b Signal Flow Diagram Basic elements Adder Unit delayer A x[n] y[n] x[n] x[n] x[n] Multiplier Pick-off node x[n] y[n] w[n] + x[n] y[n] w[n] −1 z x[n] y[n] 13 D

Basic Blocks for Signal Processors Datapath Integrator (Accumulator) Digital integrator is used in a popular type of analog-to-digital converter,called a sigma-delta modulator(∑-△调制器). Differentiation(Difference) A differentiator provides a measure of the sample-to-sample change in a signal. Decimation and Interpolation Decimation filters decrease the sample rate Interpolation filters increase the sample rate 2021/1/13 ASIC Design,by Yan Bo 14

ASIC Design, by Yan Bo Basic Blocks for Signal Processors Datapath Integrator (Accumulator) – Digital integrator is used in a popular type of analog-to-digital converter, called a sigma-delta modulator( ∑- △调制器). Differentiation(Difference) – A differentiator provides a measure of the sample-to-sample change in a signal. Decimation and Interpolation – Decimation filters decrease the sample rate – Interpolation filters increase the sample rate 2021/1/13 14

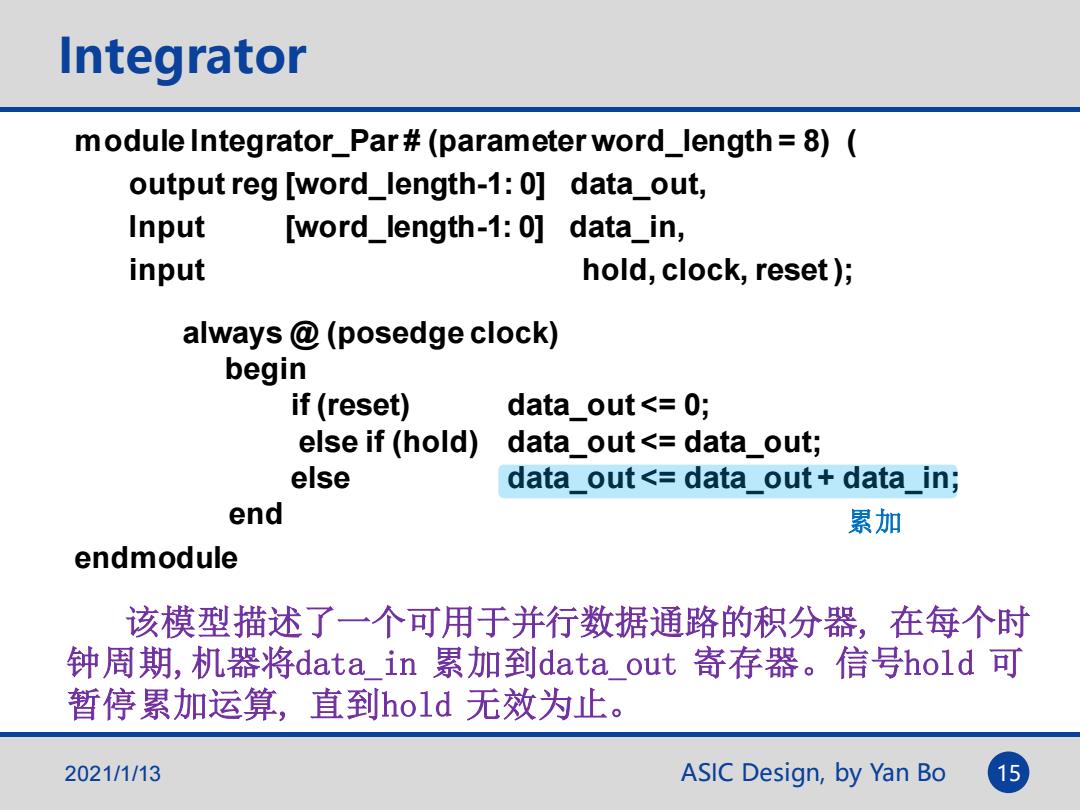

Integrator module Integrator_Par#(parameter word_length=8)( output reg [word_length-1:0]data_out, Input [word_length-1:0]data_in, input hold,clock,reset) always @(posedge clock) begin if (reset) data_out<=0; else if (hold) data_out<=data_out; else data_out<=data_out+data_in; end 累加 endmodule 该模型描述了一个可用于并行数据通路的积分器,在每个时 钟周期,机器将data in累加到data out寄存器。信号hold可 暂停累加运算,直到hold无效为止。 2021/1/13 ASIC Design,by Yan Bo 15

ASIC Design, by Yan Bo Integrator 15 该模型描述了一个可用于并行数据通路的积分器, 在每个时 钟周期,机器将data_in 累加到data_out 寄存器。信号hold 可 暂停累加运算, 直到hold 无效为止。 module Integrator_Par # (parameter word_length = 8) ( output reg [word_length-1: 0] data_out, Input [word_length-1: 0] data_in, input hold, clock, reset ); always @ (posedge clock) begin if (reset) data_out <= 0; else if (hold) data_out <= data_out; else data_out <= data_out + data_in; end endmodule 2021/1/13 累加

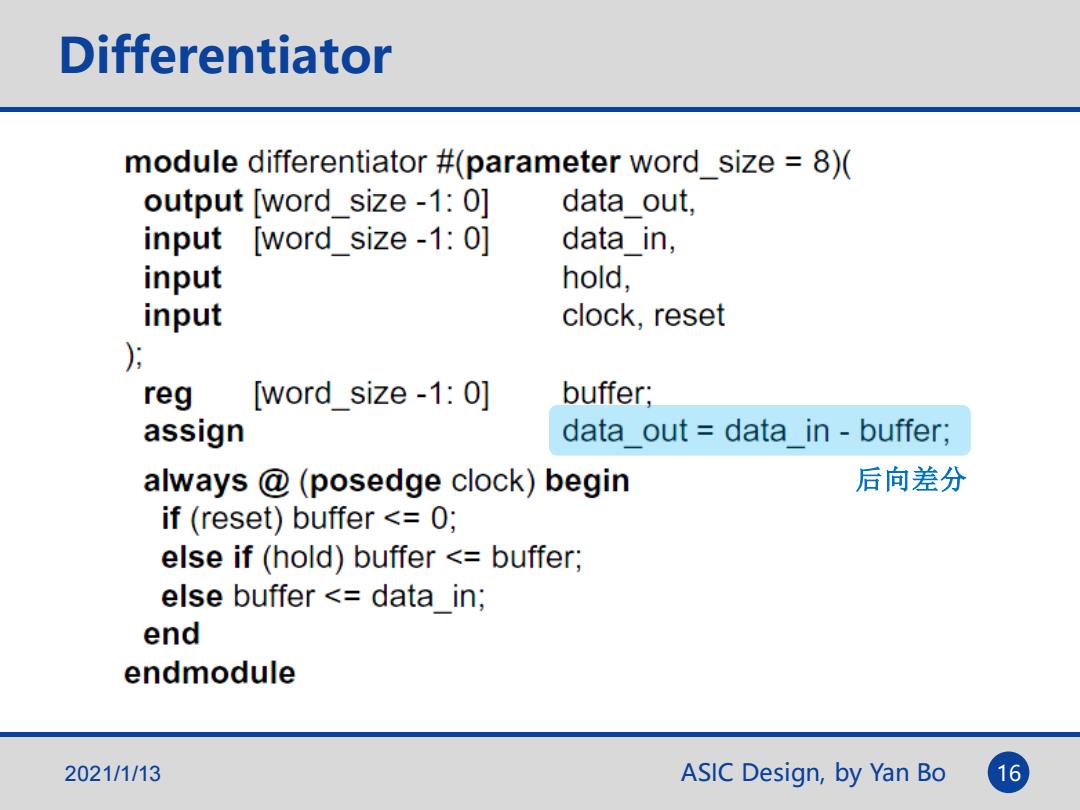

Differentiator module differentiator #(parameter word size =8)( output [word size-1:0] data out, input [word size-1:0] data in, input hold, input clock,reset ) reg [word_size-1:0] buffer; assign data out data in-buffer; always @(posedge clock)begin 后向差分 if (reset)buffer <=0; else if (hold)buffer <buffer; else buffer <data in; end endmodule 2021/1/13 ASIC Design,by Yan Bo 16

ASIC Design, by Yan Bo Differentiator 16 后向差分 2021/1/13