TIADC系统实现一一难,点分析 /95 。多个并行ADC高速采样数据如何 同步存储 ●TIADC系统误差会降低采样性能 高速数据采集及处理技术

高速数据采集及处理技术 多个并行ADC高速采样数据如何 同步存储 TIADC系统误差会降低采样性能 TIADC系统实现——难点分析

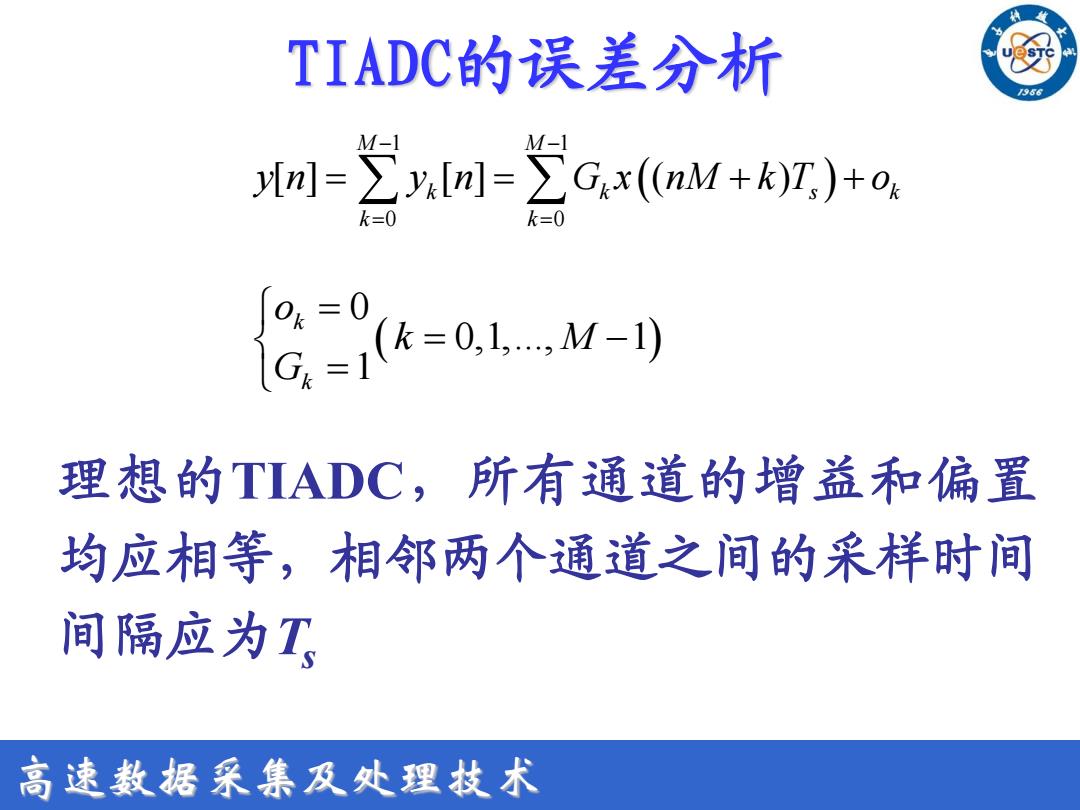

TIADC的误差分析 95 m=岁[m=2GxM+k)r))+o k=0 k=0 894=ali-刂 理想的TIADC,所有通道的增益和偏置 均应相等,相邻两个通道之间的采样时间 间隔应为T 高速数据采集及处理技术

高速数据采集及处理技术 TIADC的误差分析 1 1 0 0 [ ] [ ] ( ) M M k k s k k k y n y n G x nM k T o 0 0,1,..., 1 1 k k o k M G 理想的TIADC,所有通道的增益和偏置 均应相等,相邻两个通道之间的采样时间 间隔应为Ts

时间交替采样中的误差 实际系统中,由于芯片制造工艺及PCB制 板等原因,每个通道的增益及偏置并不完 全相等,相邻通道间的采样时间间隔不严 格等于T。我们分别将之称为增益误差 Gain Error)、 偏置误差(Offset Error)及时间误差(Timing Skew Error)。 高速数据采集及处理技术

高速数据采集及处理技术 时间交替采样中的误差 实际系统中,由于芯片制造工艺及PCB制 板等原因,每个通道的增益及偏置并不完 全相等,相邻通道间的采样时间间隔不严 格等于Ts。我们分别将之称为增益误差 ( Gain Error ) 、 偏 置 误 差 ( Offset Error ) 及 时 间 误 差 ( Timing Skew Error)

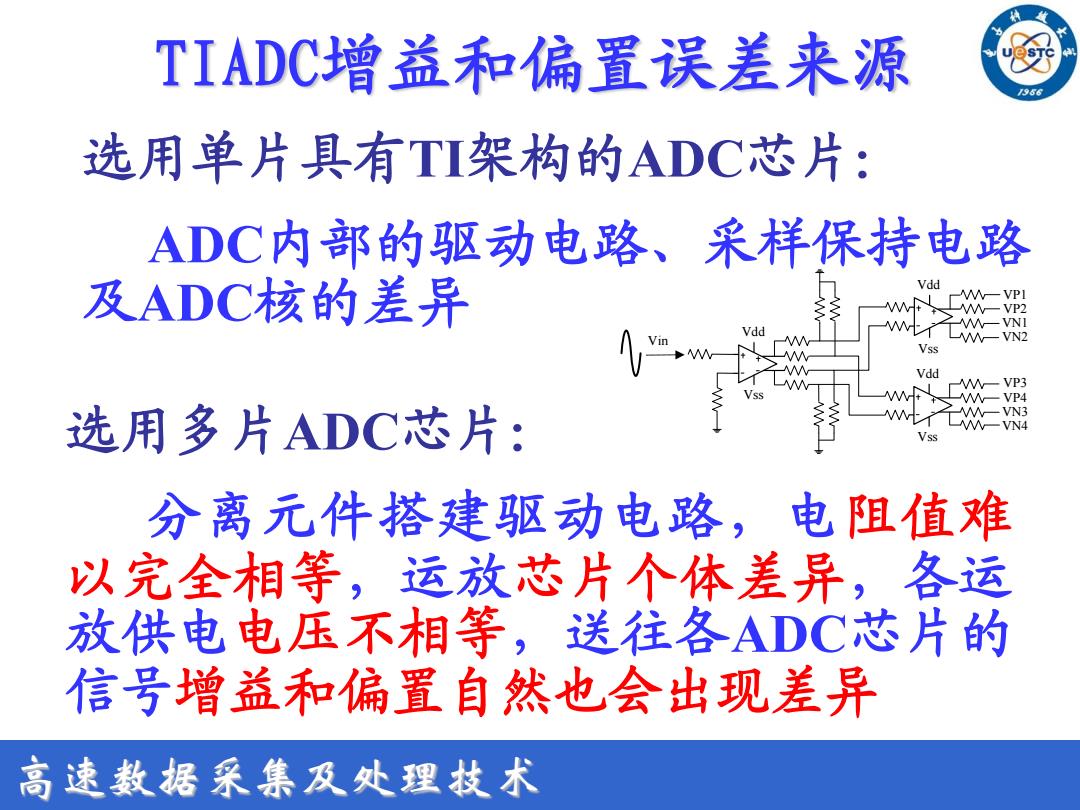

TIADC:增益和偏置误差来源 选用单片具有TI架构的ADC芯片: ADC内部的驱动电路、采样保持电路 及ADC核的差异 VP W-VP2 -VNI dd Vss Vdd VP3 VP4 选用多片ADC芯片: VN3 VN4 分离元件搭建驱动电路,电阻值难 以完全相等,运放芯片个体差异,各运 放供电电压不相等,送往各ADC芯片的 信号增益和偏置自然也会出现差异 高速数据采集及处理技术

高速数据采集及处理技术 TIADC增益和偏置误差来源 Vdd Vss Vdd Vss Vdd Vss VP1 VP2 VN1 VN2 VP3 VP4 VN3 VN4 Vin 选用单片具有TI架构的ADC芯片: ADC内部的驱动电路、采样保持电路 及ADC核的差异 选用多片ADC芯片: 分离元件搭建驱动电路,电阻值难 以完全相等,运放芯片个体差异,各运 放供电电压不相等,送往各ADC芯片的 信号增益和偏置自然也会出现差异

TIADC时间误差来源 1、相邻通道采样时钟之间的相位差不 完全相等: 具有产生多路分相时钟功能的锁相环 的相位调节存在一定的误差 多个ADC的采样时钟走线难以完全等 长 高速数据采集及处理技术

高速数据采集及处理技术 TIADC时间误差来源 1、相邻通道采样时钟之间的相位差不 完全相等: 具有产生多路分相时钟功能的锁相环 的相位调节存在一定的误差 多个ADC的采样时钟走线难以完全等 长