地址码:数据,指令 ·指定源操作数、目的操作数、下一条指令地址 一地址:寄存器、主存、O端口 ·地址码域格式 -4地址指令:Oprs1,rs2,rd,ni -3地址指令:oprs1,rs2,rd;ni在PC中 -2地址指令:Oprs1,rs2; rd=rs1 or ACC -1地址指令:oprs2; rs1=ACC,rd=ACC -0地址指令:op; 堆栈操作 llxx@ustc.edu.cn 11/41

llxx@ustc.edu.cn 11/41 地址码:数据,指令 • 指定源操作数、目的操作数、下一条指令地址 – 地址:寄存器、主存、I/O端口 • 地址码域格式 – 4地址指令:op rs1, rs2, rd, ni – 3地址指令:op rs1, rs2, rd; ni在PC中 – 2地址指令:op rs1, rs2; rd=rs1 or ACC – 1地址指令:op rs2; rs1=ACC,rd=ACC – 0地址指令:op; 堆栈操作

寻址方式:指令的地址码 ·寻址方式:指令字和操作数的存储地址计算方式 ·指令寻址:现代CPU利用PC -顺序执行:每执行一条指令,PC自动1 一跳转:更新PC,转移到目的地址执行 操作数寻址 一指令中给出“形式地址” 一有效地址:操作数在寄存器/内存中的物理地址 ·EA=寻址方式+形式地址 Control Arithmetic Internal Unit Logic Unit data bus Registers 操作码 Instruction 形式地址 Decoder llxx@ustc.edu.cn 12/41

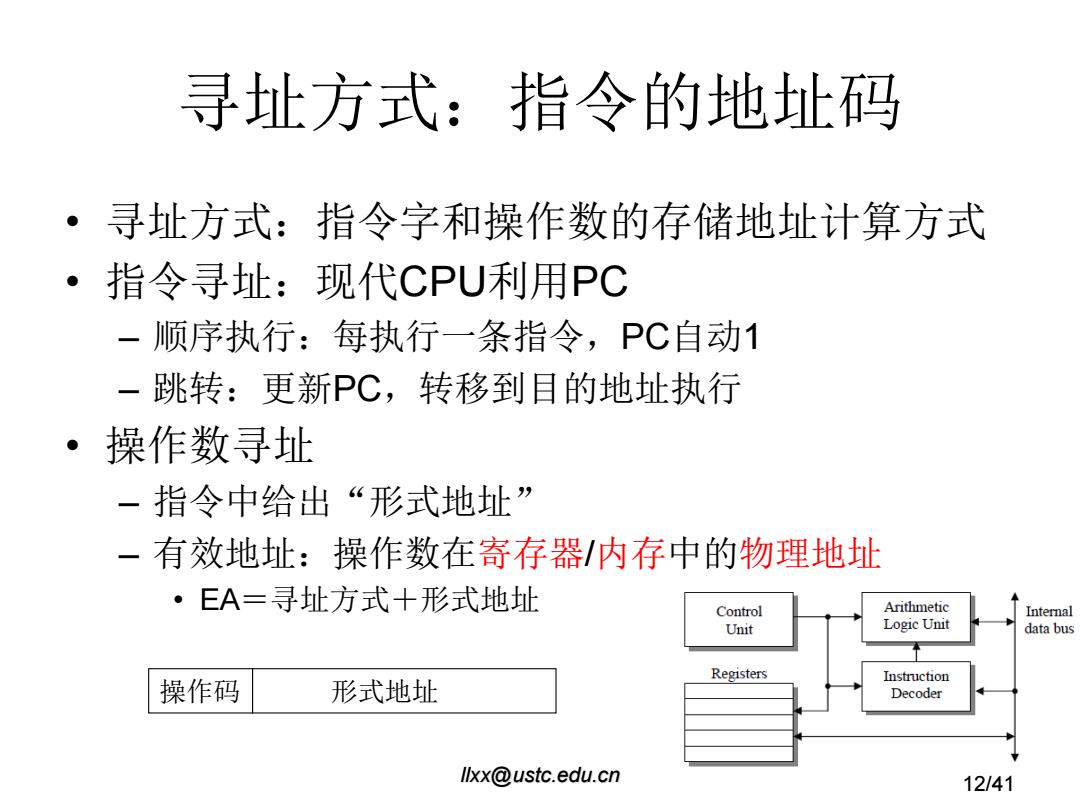

llxx@ustc.edu.cn 12/41 寻址方式:指令的地址码 • 寻址方式:指令字和操作数的存储地址计算方式 • 指令寻址:现代CPU利用PC – 顺序执行:每执行一条指令,PC自动1 – 跳转:更新PC,转移到目的地址执行 • 操作数寻址 – 指令中给出“形式地址” – 有效地址:操作数在寄存器/内存中的物理地址 • EA=寻址方式+形式地址 操作码 形式地址

操作数寻址方式 常见约10种 Instruction Instruction Instruction Operand A A 立即寻址(a) Memory Memory 直接寻址(b) Operand -间接寻址(c) Operand - 寄存器寻址(d) (a)Immediate (b)Direct (c)Indirect 一寄存器间接寻址 (e) Instruction Instruction Instruction R R 基址寻址(f) Memory Memory ·BP+offset ◆Operand -PC相对寻址(f) Operand Operand Registers Registers Registers ·PC+offsset (d)Register (e)Register indirect (f)Displacement -堆栈寻址(g) Instruction 变址寻址(d+f) Implicit 有效地址计算步骤? ·Index:x86的si/di 最少必须哪几种? Top of stack -隐含寻址(如g) register 指令寻址有哪些方式? (g)Stack 13/41

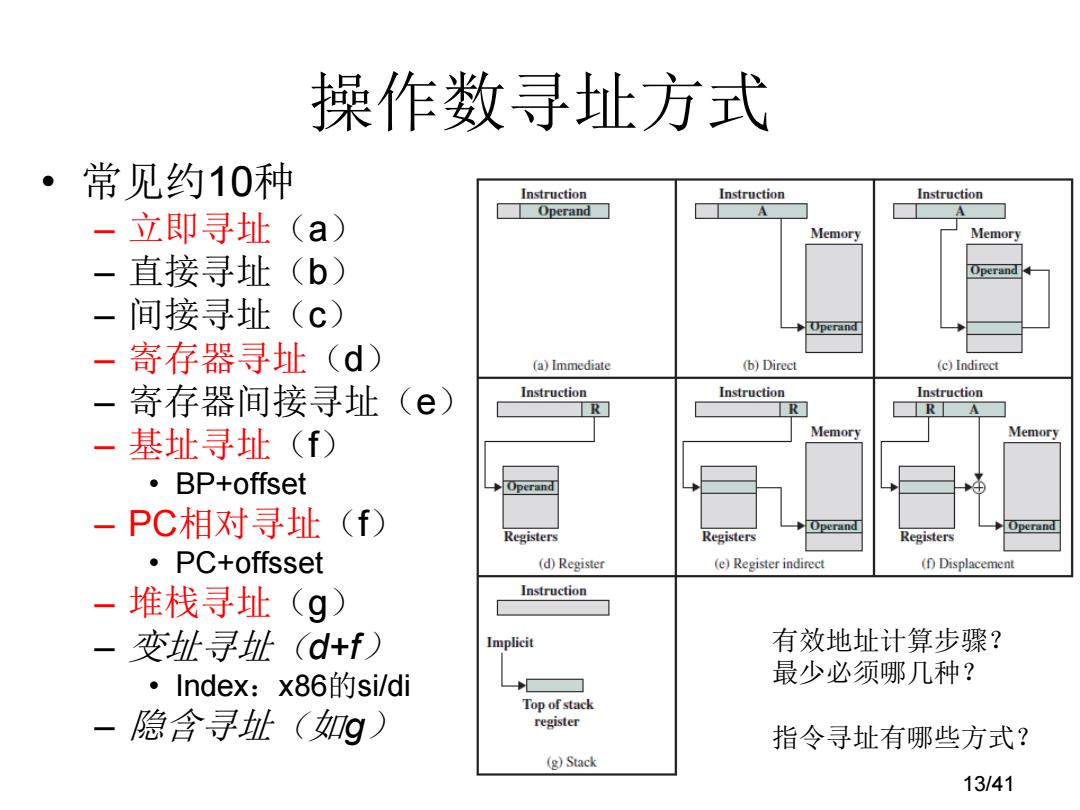

13/41 操作数寻址方式 • 常见约10种 – 立即寻址(a) – 直接寻址(b) – 间接寻址(c) – 寄存器寻址(d) – 寄存器间接寻址(e) – 基址寻址(f) • BP+offset – PC相对寻址(f) • PC+offsset – 堆栈寻址(g) – 变址寻址(d+f) • Index:x86的si/di – 隐含寻址(如g) 有效地址计算步骤? 最少必须哪几种? 指令寻址有哪些方式?

RISC-VISA的特点 David Potterson 模块化:51+133+13=197条 Andrew waterman -RV32I指令集:支持完整软件栈,永远不变 ·共51条:图2-1(37条,重点关注)+图2-37(14条) RV32IMFD指令集:RV32I的基本扩展,图2-38,133条 -特殊指令:同步,CSR操作,异常。图5-47,13条 约束 Mnemonic Description Insn.Count 成本: 芯片面积 Base architecture 51 M Integer multiply/divide 13 简洁 A Atomic operations 22 -性能: F 时间,功耗 Single-precision floating point 30 D Double-precision floating point 32 一架构与实现分离 Compressed instructions 36 一扩展性:操作码域空间 程序大小 一易于编程/编译/链接 RISC-I RISC-II RISC-II (SOAR)RISC-TV (SPUR) RISC-V 1981 1983 1984 1988 2013 David Patterson,Andrew Waterman,The RISC-V Reader:An Open Architecture Atlas,2017

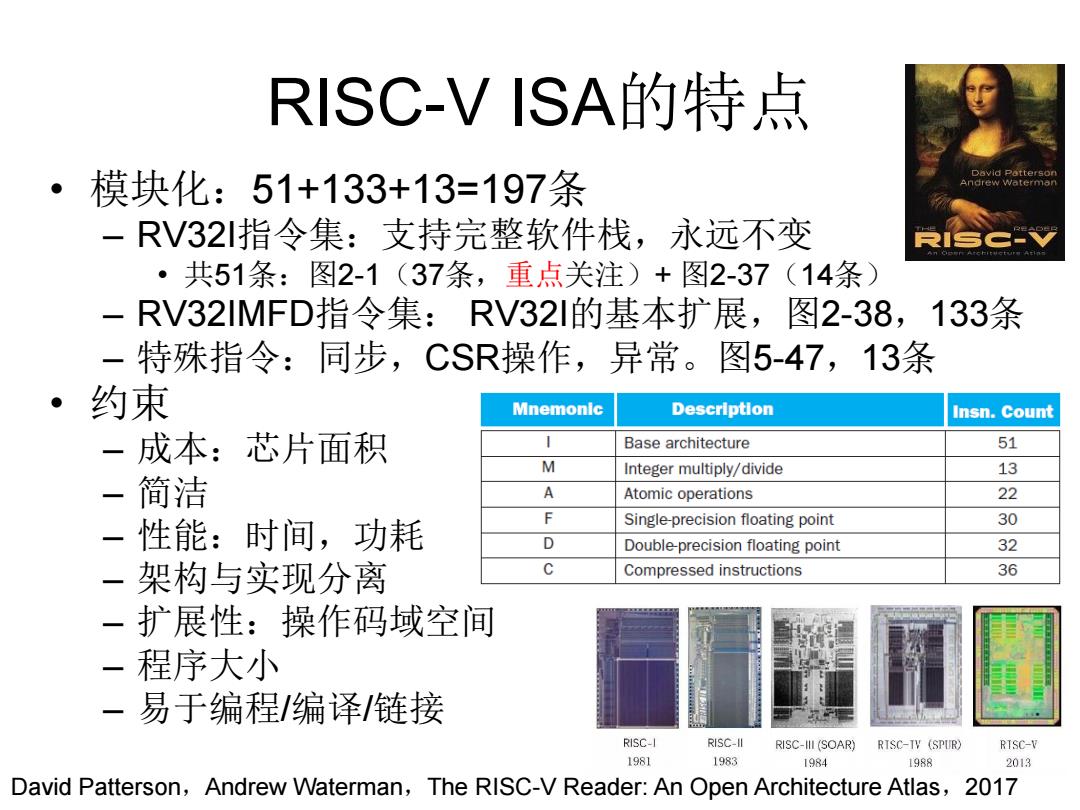

RISC-V ISA的特点 • 模块化:51+133+13=197条 – RV32I指令集:支持完整软件栈,永远不变 • 共51条:图2-1(37条,重点关注)+ 图2-37(14条) – RV32IMFD指令集: RV32I的基本扩展,图2-38,133条 – 特殊指令:同步,CSR操作,异常。图5-47,13条 • 约束 – 成本:芯片面积 – 简洁 – 性能:时间,功耗 – 架构与实现分离 – 扩展性:操作码域空间 – 程序大小 – 易于编程/编译/链接 David Patterson,Andrew Waterman,The RISC-V Reader: An Open Architecture Atlas,2017

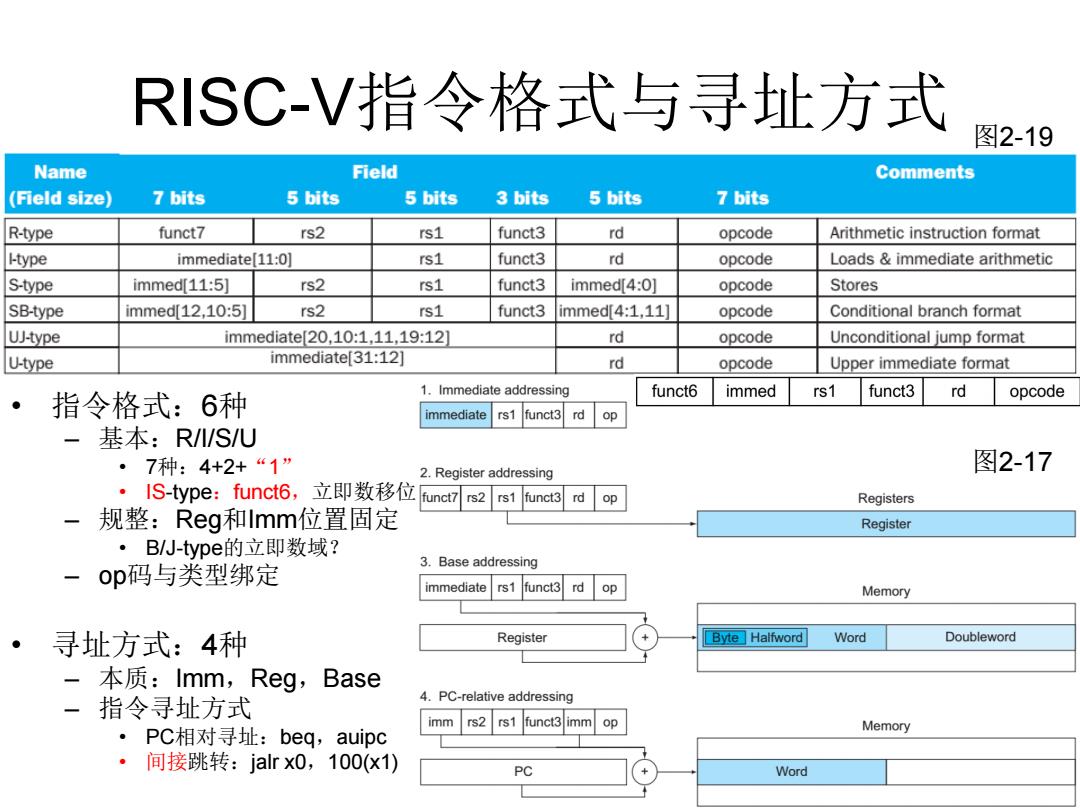

RISC-V指令格式与寻址方式 图2-19 Name Field Comments (Field size】 7 bits 5 bits 5 bits 3 bits 5 bits 7 bits R-type funct7 rs2 rs1 funct3 rd opcode Arithmetic instruction format I-type immediate[11:0] rs1 funct3 rd opcode Loads immediate arithmetic S-type immed[11:5] rs2 rs1 funct3 immed[4:0] opcode Stores SB-type immed12,10:5] rs2 rs1 funct3 immed[4:1,11] opcode Conditional branch format UJ-type immediate[20,10:1,11,19:12] rd opcode Unconditional jump format U-type immediate[31:12] rd opcode Upper immediate format 1.Immediate addressing 指令格式:6种 funct6 immed rs1 funct3 rd opcode immediate rs1 funct3 rd op - 基本:RI/S/U ·7种:4+2+“1” 2.Register addressing 图2-17 ·lS-type:functe6,立即数移位 funct7 rs2 rs1 funct3 rd op Registers 规整:Reg和lmm位置固定 Register ·BJ-type的立即数域? op码与类型绑定 3.Base addressing immediate rs1 funct3rd op Memory 寻址方式:4种 Register Byte Halfword Word Doubleword - 本质:lmm,Reg,Base 指令寻址方式 4.PC-relative addressing imm rs2 rs1 funct3 imm op ·PC相对寻址:beq,auipc Memory ·间接跳转:jalr x0,100(x1) PC Word

RISC-V指令格式与寻址方式 • 指令格式:6种 – 基本:R/I/S/U • 7种:4+2+“1” • IS-type:funct6,立即数移位 – 规整:Reg和Imm位置固定 • B/J-type的立即数域? – op码与类型绑定 • 寻址方式:4种 – 本质:Imm,Reg,Base – 指令寻址方式 • PC相对寻址:beq,auipc • 间接跳转:jalr x0,100(x1) 图2-17 图2-19