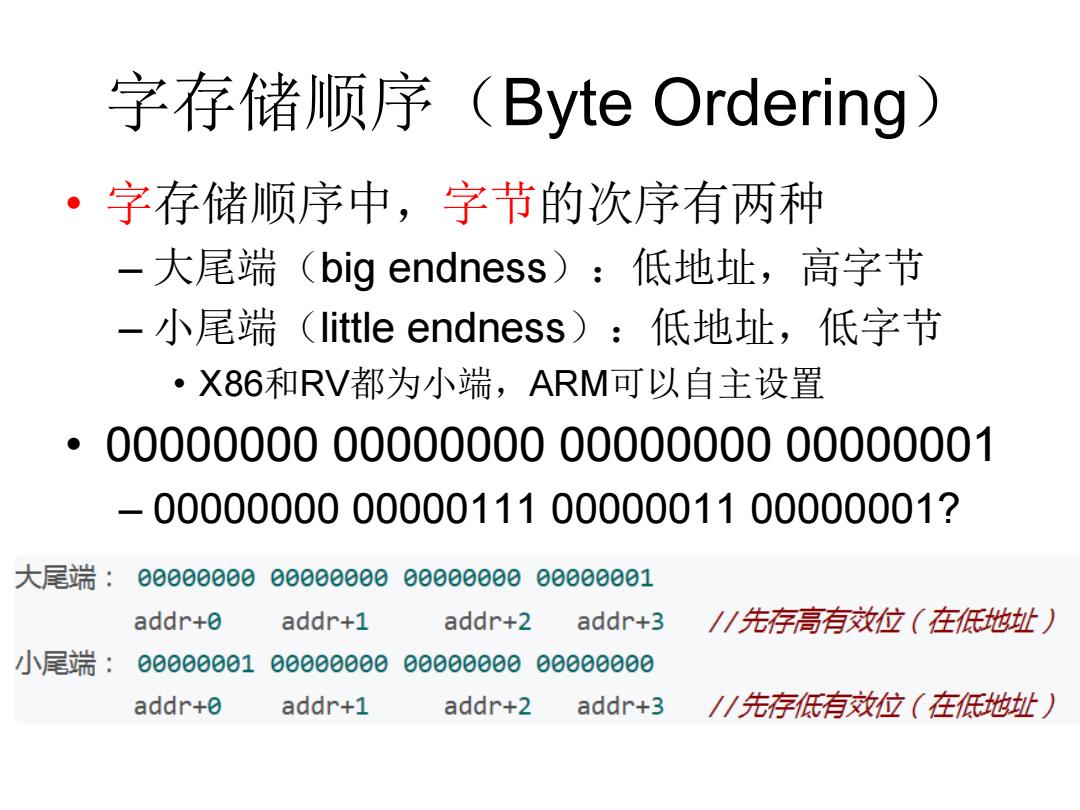

字存储顺序(Byte Ordering) ·字存储顺序中,字节的次序有两种 -大尾端(big endness):低地址,高字节 -小尾端(little endness):低地址,低字节 ·X86和RV都为小端,ARM可以自主设置 00000000000000000000000000000001 00000000000001110000001100000001? 大尾端: 0000000000000000 8000000000000001 addr+0 addr+1 addr+2 addr+3 /1先存高有效位(在低地址) 小尾端:08000001 000000000000000000000000 addr+0 addr+1 addr+2 addr+3 /1先存低有效位(在低地址)

字存储顺序(Byte Ordering) • 字存储顺序中,字节的次序有两种 – 大尾端(big endness):低地址,高字节 – 小尾端(little endness):低地址,低字节 • X86和RV都为小端,ARM可以自主设置 • 00000000 00000000 00000000 00000001 – 00000000 00000111 00000011 00000001?

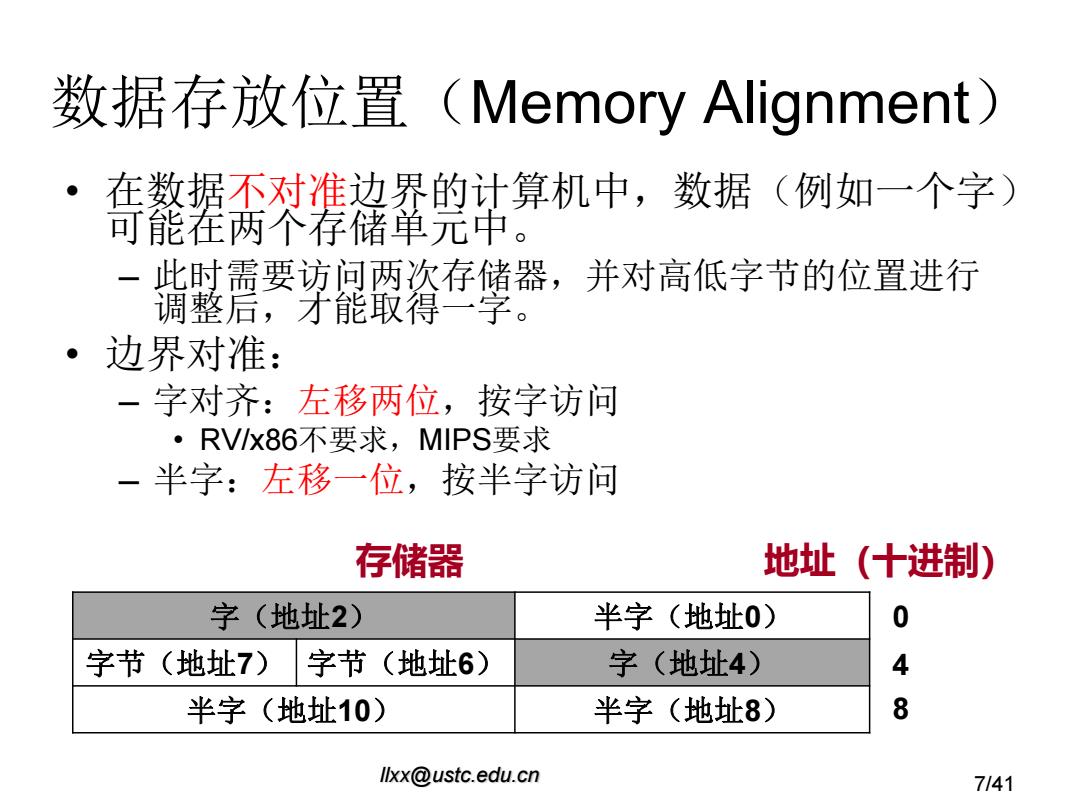

数据存放位置(Memory Alignment) 在数据不对准边界的计算机中,数据(例如一个字) 可能在两个存储单元中。 此时需要访问两次存储器,并对高低字节的位置进行 调整后,才能取得一字。 边界对准: 一字对齐:左移两位,按字访问 ·RVIX86不要求,MIPS要求 一半字:左移一位,按半字访问 存储器 地址(十进制) 字(地址2) 半字(地址0) 0 字节(地址7) 字节(地址6) 字(地址4) 4 半字(地址10) 半字(地址8) 8 llxx@ustc.edu.cn 7/41

llxx@ustc.edu.cn 7/41 数据存放位置(Memory Alignment) • 在数据不对准边界的计算机中,数据(例如一个字) 可能在两个存储单元中。 – 此时需要访问两次存储器,并对高低字节的位置进行 调整后,才能取得一字。 • 边界对准: – 字对齐:左移两位,按字访问 • RV/x86不要求,MIPS要求 – 半字:左移一位,按半字访问 字(地址2) 半字(地址0) 0 4 8 字节(地址7) 字节(地址6) 字(地址4) 半字(地址10) 半字(地址8) 存储器 地址(十进制)

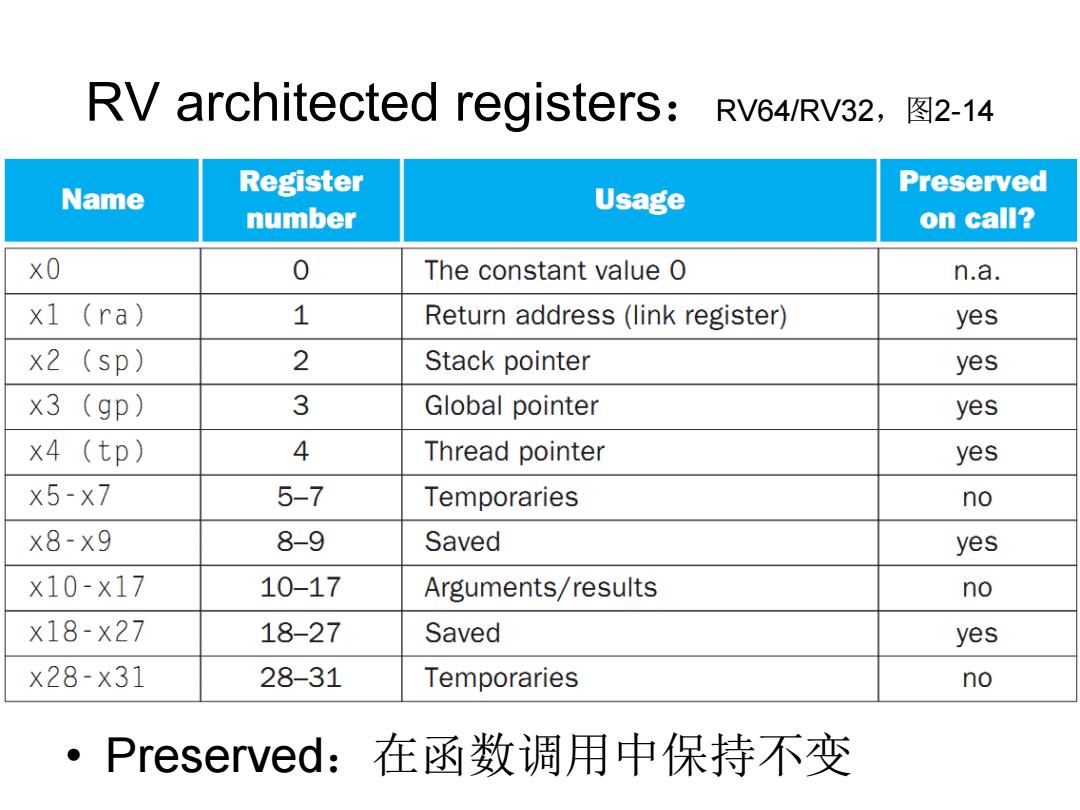

RV architected registers:RV64RV32.2-14 Preserved Name Register Usage number on call? x0 0 The constant value 0 n.a. x1 (ra) 1 Return address(link register) yes x2 (sp) 2 Stack pointer yes x3 (gp) 3 Global pointer yes x4 (tp) 4 Thread pointer yes x5-x7 5-7 Temporaries no x8-x9 8-9 Saved yes ×10-×17 10-17 Arguments/results no x18-×27 18-27 Saved yes ×28-×31 28-31 Temporaries no ·Preserved:在函数调用中保持不变

RV architected registers:RV64/RV32,图2-14 • Preserved:在函数调用中保持不变

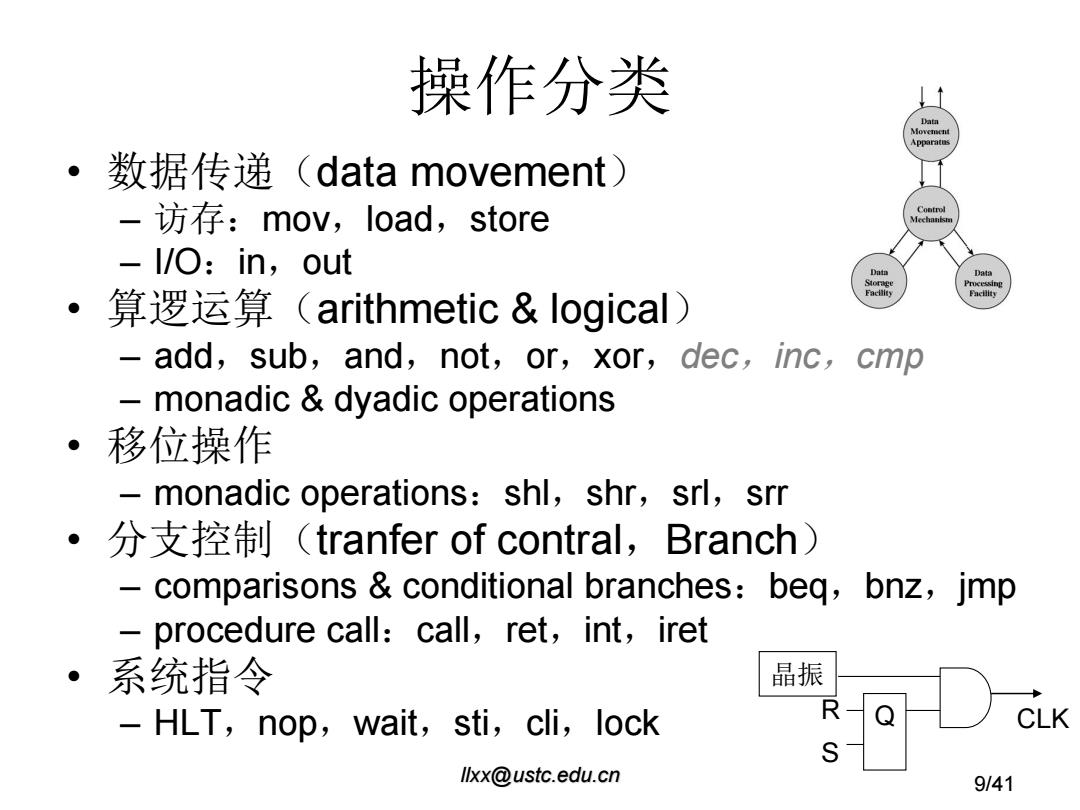

操作分类 Data Movement ·数据传递 (data movement) -访存:mov,load,store 1/O:in,out Data Data 。1 算逻运算(arithmetic&logical) - add,sub,and,not,or,xor,dec,inc,cmp monadic dyadic operations 移位操作 monadic operations:shl,shr,srl,srr ·分支控制(tranfer of contral,Branch) comparisons conditional branches:beq,bnz,jmp procedure call:call,ret,int,iret 系统指令 晶振 -HLT,nop,wait,sti,cli,lock R Q CLK S llxx@ustc.edu.cn 9/41

llxx@ustc.edu.cn 9/41 操作分类 • 数据传递(data movement) – 访存:mov,load,store – I/O:in,out • 算逻运算(arithmetic & logical) – add,sub,and,not,or,xor,dec,inc,cmp – monadic & dyadic operations • 移位操作 – monadic operations:shl,shr,srl,srr • 分支控制(tranfer of contral,Branch) – comparisons & conditional branches:beq,bnz,jmp – procedure call:call,ret,int,iret • 系统指令 – HLT,nop,wait,sti,cli,lock 晶振 R S Q CLK

指令字格式Machine Instruction Layout von Neumann:“指令由操作码和地址码构成” ·操作码:操作的性质 地址码:指令和操作数(operand)的存储位置 操作码域(op) 地址码域(addr) ·指令字长度固定Vs.可变:RISC(RV/MIPS/ARM)一般32位 ·固定:规则,浪费空间 操作码长度固定VS.可变 ·固定:译码简单,指令条数有限,RISC C (RV/MIPS/ARM ·可变:指令条数和格式按需调整,CISC(x86) ·“扩展操作码技术”:调整op与addr域 ·如果指令字长固定,则操作码长度增加,地址码长度缩短 llxx@ustc.edu.cn 10/41

llxx@ustc.edu.cn 10/41 指令字格式Machine Instruction Layout • von Neumann: “指令由操作码和地址码构成” • 操作码:操作的性质 • 地址码:指令和操作数(operand)的存储位置 • 指令字长度固定vs.可变:RISC(RV/MIPS/ARM)一般32位 • 固定:规则,浪费空间 • 操作码长度固定vs.可变 • 固定:译码简单,指令条数有限,RISC(RV/MIPS/ARM) • 可变:指令条数和格式按需调整,CISC(x86) • “扩展操作码技术”:调整op与addr域 • 如果指令字长固定,则操作码长度增加,地址码长度缩短 操作码域(op) 地址码域(addr)