冈I 3)用T型触发器构成的逻辑电路图 J0=K0=1 J1=K1=20 J2=K2=2120 FF FF2 串行进位 触发器 负载均匀 D FF FF 并行进位 低位触发 器负载重 D

J0= K0 =1 J1= K1 = Q0 J2= K2 = Q1Q0 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & & C Q0 Q1 Q2 Q0 Q1 Q2 串行进位 触发器 负载均匀 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & & C Q0 Q1 Q2 Q0 Q1 Q2 并行进位 低位触发 器负载重 (3) 用T 型触发器构成的逻辑电路图

(④)用T型触发器构成的逻辑电路图 22 CP (⑤)n位二进制同步加法计数器级联规律: T=g%02.g0-1 i=0

(5) n 位二进制同步加法计数器级联规律: -1 0 1 2 1 0 = = − − = i j n j n n n i n Ti Qi Q Q Q Q (4) 用T ’型触发器构成的逻辑电路图 CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF2 & C Q0 Q1 Q2 Q0 Q1 Q2 1 & 1 &

>K H 2.3位二进制同步减法计数器 C Q2Q1Qo B FF2、FF1、FFo 22、21、20 0 0 0 0 1 级联规律: 1 1 1 1 0 1 1 0 0 7=0%0200-1g 3 1 0 1 0 1 0 0 T0=1 T=2o" T2=21"夏" 5 0 1 1 0 67 0 1 0 0 0 0 1 0 FF FF CP ●

B = Q2 n Q1 n Q0 n Borrow 若用T 触发器: 2. 3 位二进制同步减法计数器 C P Q2Q1Q0 B 0 1 2 3 4 5 6 7 0 0 0 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 0 0 0 0 0 0 0 FF2 、FF1 、FF0 Q2 、Q1 、Q0 — 向高位发出的借位信号 T0 = 1 T1=Q0 n T2= Q1 n Q0 n 级联规律: -1 0 1 2 1 0 = = − − = i j n j n n n i n Ti Qi Q Q Q Q CP 1J 1K C1 FF0 1 1J 1K C1 FF1 1J 1K C1 FF1 & & B Q0 Q1 Q2 Q0 Q1 Q2

3.3位二进制同步可逆计数器 ()单时钟输入二进制同步可逆计数器 加/减 & 控制端 UID 1J 1 1K FFo Co FF FF2 U/D=0 加计数 T0=1、T1=2om、T2=21"2” C1B=221"26 U/D=1 减计数 To=1、T1=2"、T2=21"2 C/B=25212

3. 3 位二进制同步可逆计数器 (1) 单时钟输入二进制同步可逆计数器 加/减 控制端 U / D = 0 加计数 T0 = 1、T1= Q0 n 、T2= Q1 nQ0 n / 2 1 0 n n n C B = Q Q Q U / D = 1 减计数 T0 = 1、T1= Q0 n 、T2= Q1 nQ0 n n n n C B Q2 Q1 Q0 / = CP Q0 1J 1K C1 FF0 1 Q0 Q2 1J 1K C1 FF2 Q2 Q1 1J 1K C1 FF1 Q1 U /D 1 & 1 & 1 & 1 C/B

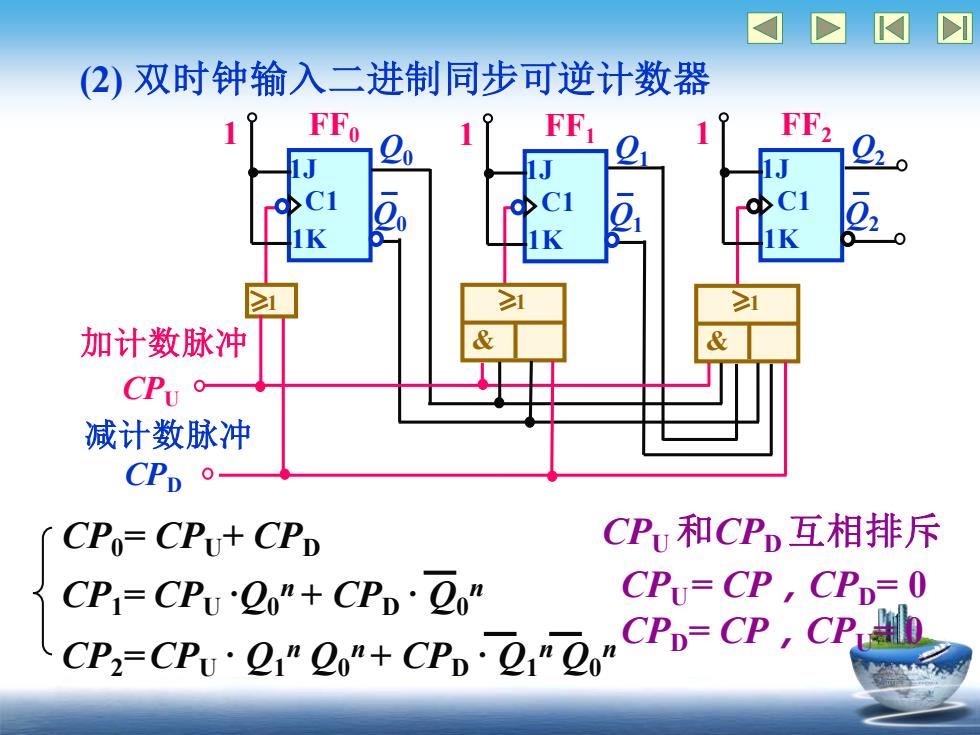

(2)双时钟输入二进制同步可逆计数器 FFo FF 加计数脉冲 CPU 减计数脉冲 CPD CPo=CPU+CPD CPu和CPD互相排斥 CP=CPu2"+CPD·2" CPU=CP,CPD=0 CP2=CPu·21"2o+CPD·21"Qn CPD=CP,CPL

(2) 双时钟输入二进制同步可逆计数器 加计数脉冲 减计数脉冲 CP0= CPU+ CPD CP1= CPU ·Q0 n + CPD · Q0 n CP2=CPU · Q1 n Q0 n+ CPD · Q1 n Q0 n CPU 和CPD 互相排斥 CPU= CP,CPD= 0 CPD= CP,CPU= 0 CPU Q0 1J 1K C1 1 FF0 Q0 Q2 1J 1K C1 1 FF2 Q2 Q1 1J 1K C1 1 FF1 Q1 1 & 1 & 1 CPD