主要技术指标 USTC 速度指标:存取时间和存储周期、存储器的带宽。 存取时间(MEM Access Time).,:指从启动一次存储器 操作到完成该操作所需的全部时间。 读出时间:,从存储器接收到有效地址开始,到产生有 效输出所需的全部时间。 写入时间:从存储器接收到有效地址开始,到数据写 入被选中单元所需的全部时间。 存储周期(Mem Cycle Time):指连续启动两次独立的 操作(如两次读操作)所需的最小间隔的时间。 通常大于存取时间。 存储器的带宽:单位时间里存储器所存取的最大信息量。 单位:以位秒、字节秒 例:存取周期为500ns, 每个存取周期可访问16位,则它的 带宽为 1 16位× =32×10位/秒=32M位/秒 500×10-9秒

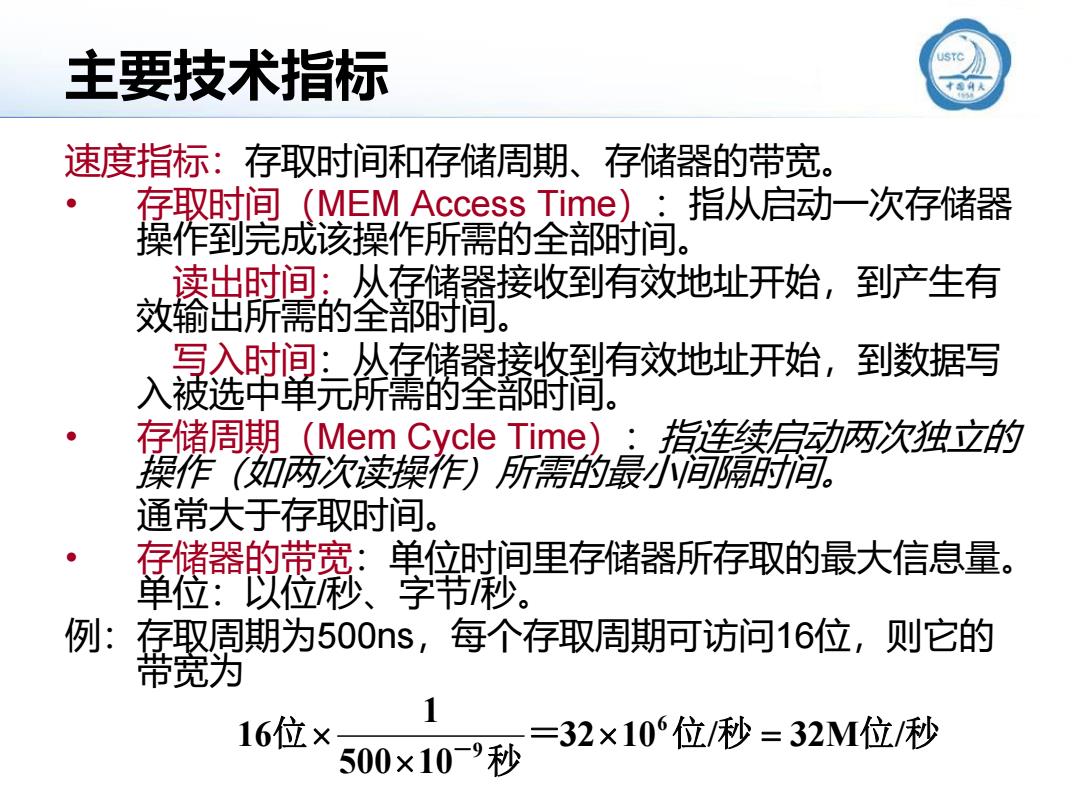

主要技术指标 速度指标:存取时间和存储周期、存储器的带宽。 • 存取时间(MEM Access Time):指从启动一次存储器 操作到完成该操作所需的全部时间。 读出时间:从存储器接收到有效地址开始,到产生有 效输出所需的全部时间。 写入时间:从存储器接收到有效地址开始,到数据写 入被选中单元所需的全部时间。 • 存储周期(Mem Cycle Time):指连续启动两次独立的 操作(如两次读操作)所需的最小间隔时间。 通常大于存取时间。 • 存储器的带宽:单位时间里存储器所存取的最大信息量。 单位:以位/秒、字节/秒。 例:存取周期为500ns,每个存取周期可访问16位,则它的 带宽为 = 位 秒 位 秒 秒 位 - 32 10 / 32M / 500 10 1 16 6 9 =

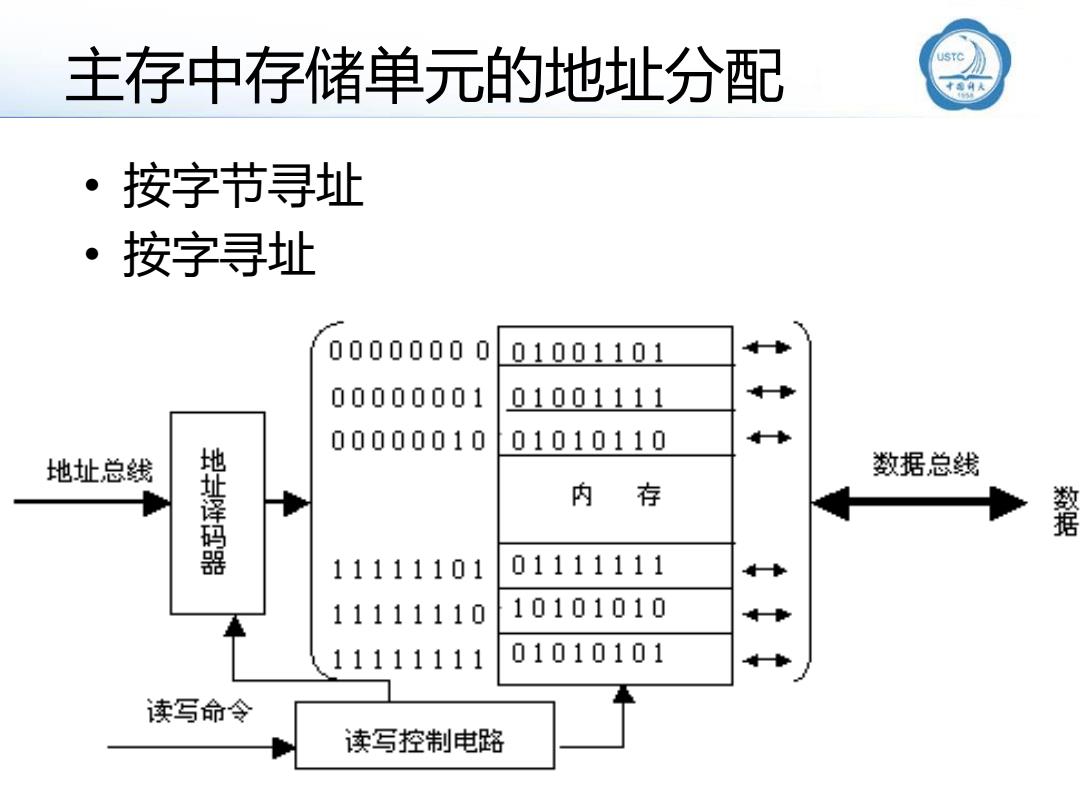

主存中存储单元的地址分配 ·按字节寻址 按字寻址 00000000 01001101 00000001 01001111 00000010 01010110 地址总线 地址译码器 数据总线 内 存 11111101 01111111 11111110 10101010 11111111 01010101 读写命令 读写控制电路

主存中存储单元的地址分配 • 按字节寻址 • 按字寻址

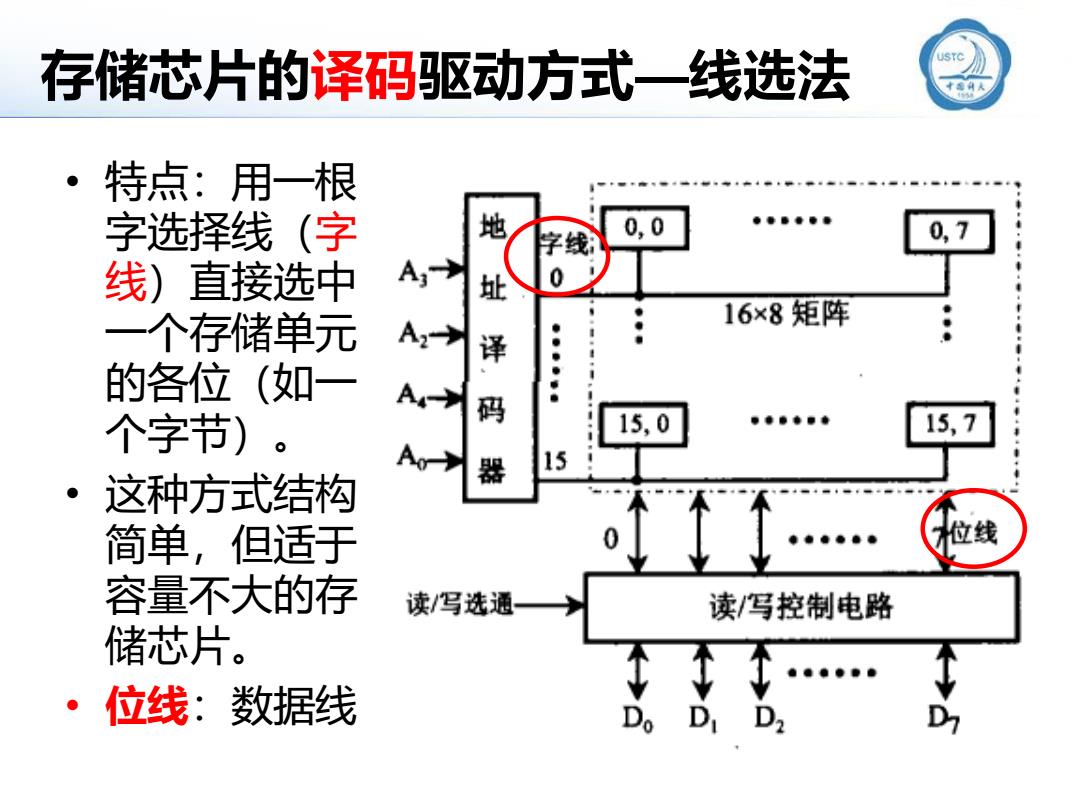

存储芯片的译码驱动方式一线选法 STC 特点:用一根 字选择线(字 地 字线 0,0 线)直接选中 址 一个存储单元 16×8矩阵 的各位(如一 译码 个字节)。 15,0 年●●非甲 这种方式结构 器 15 简单,但适于 位线 容量不大的存 读/写选通 读/写控制电路 储芯片。 位线:数据线 Do D D

存储芯片的译码驱动方式—线选法 • 特点:用一根 字选择线(字 线)直接选中 一个存储单元 的各位(如一 个字节)。 • 这种方式结构 简单,但适于 容量不大的存 储芯片。 • 位线:数据线

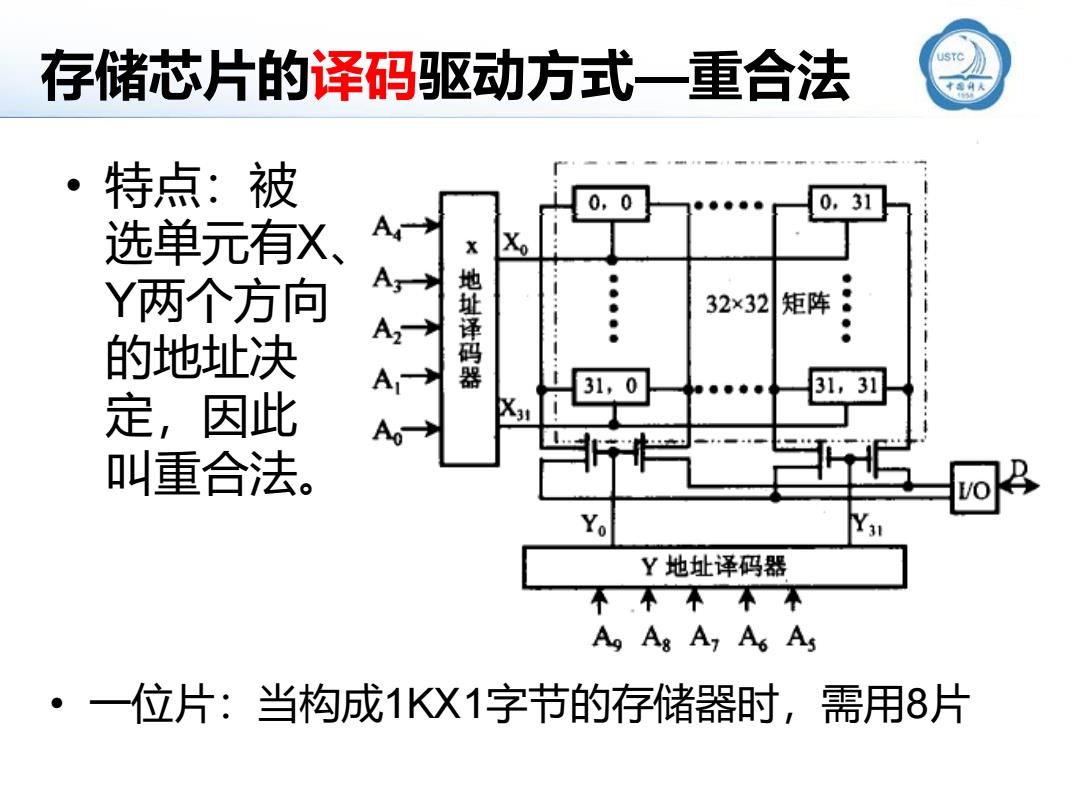

存储芯片的译码驱动方式一重合法 特点:被 选单元有X、 Y两个方向 地址译码器 32×32矩阵 的地址决 31, 31,31 定,因此 A。 叫重合法。 Yo Y地址译码器 不不不 Ag A8 A7 As As ·一位片:当构成1KX1字节的存储器时,需用8片

存储芯片的译码驱动方式—重合法 • 特点:被 选单元有X、 Y两个方向 的地址决 定,因此 叫重合法。 • 一位片:当构成1KX1字节的存储器时,需用8片

静态RAM(SRAM) 基本存储电路由6个MOS管构成: T~T4组成双稳态触发器 T1,T2为放大管, ā T3,T4为负载管, T5,T6为开关控制管 X地址 译码线 Vcc 读出:选通T5,T6 A点与引/O连通 B点与引/O连通 写入:j 选通T5,T6 A点与/O连通 B点与/O连通 (I/O) 接Y地址译码线

静态RAM (SRAM) 基本存储电路由6个MOS管构成: T1~T4组成双稳态触发器 T1 ,T2为放大管, T3 ,T4为负载管, T5 ,T6为开关控制管 读出:选通T5 ,T6 A点与I/O连通 B点与I/O连通 写入:选通T5 ,T6 A点与I/O连通 B点与I/O连通 T6 T7 T8 T5 T3 T4 T1 T2 Vcc A B D0 X地址 译码线 (I/O) 接Y地址译码线 (I/O) D0