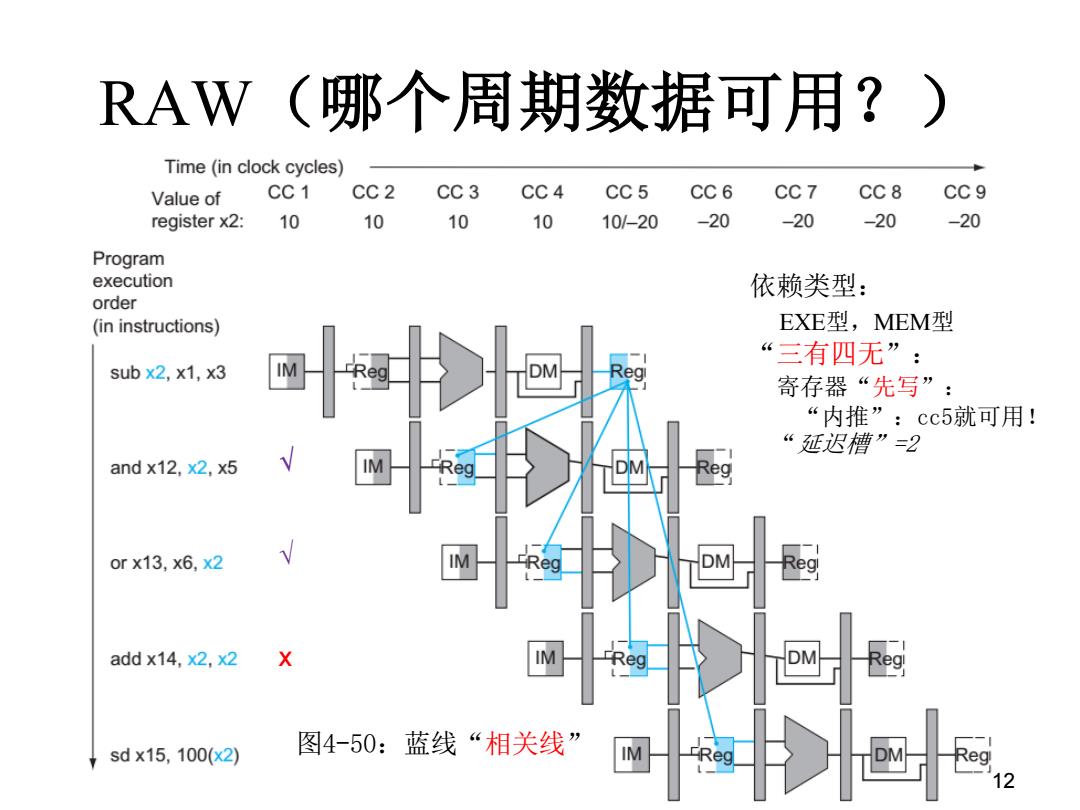

RAW(哪个周期数据可用?) Time(in clock cycles) Value of CC1 CC 2 CC3 CC4 CC5 CC6 CC7 CC8 CC 9 register x2: 10 10 10 10 10/-20 -20 -20 -20 -20 Program execution 依赖类型: order (in instructions) EXE型,MEM型 “三有四无”: sub x2,x1,x3 寄存器“先写”: “内推”:cc5就可用! “延迟槽”=2 and x12,x2,x5 Reg eg 0rX13,X6,x2 add x14,x2,x2 X sd×15,100(x2) 图4-50:蓝线“相关线” 12

12 RAW(哪个周期数据可用?) 依赖类型: EXE型,MEM型 “三有四无”: 寄存器“先写”: “内推”:cc5就可用! “延迟槽”=2 图4-50:蓝线“相关线” x √ √

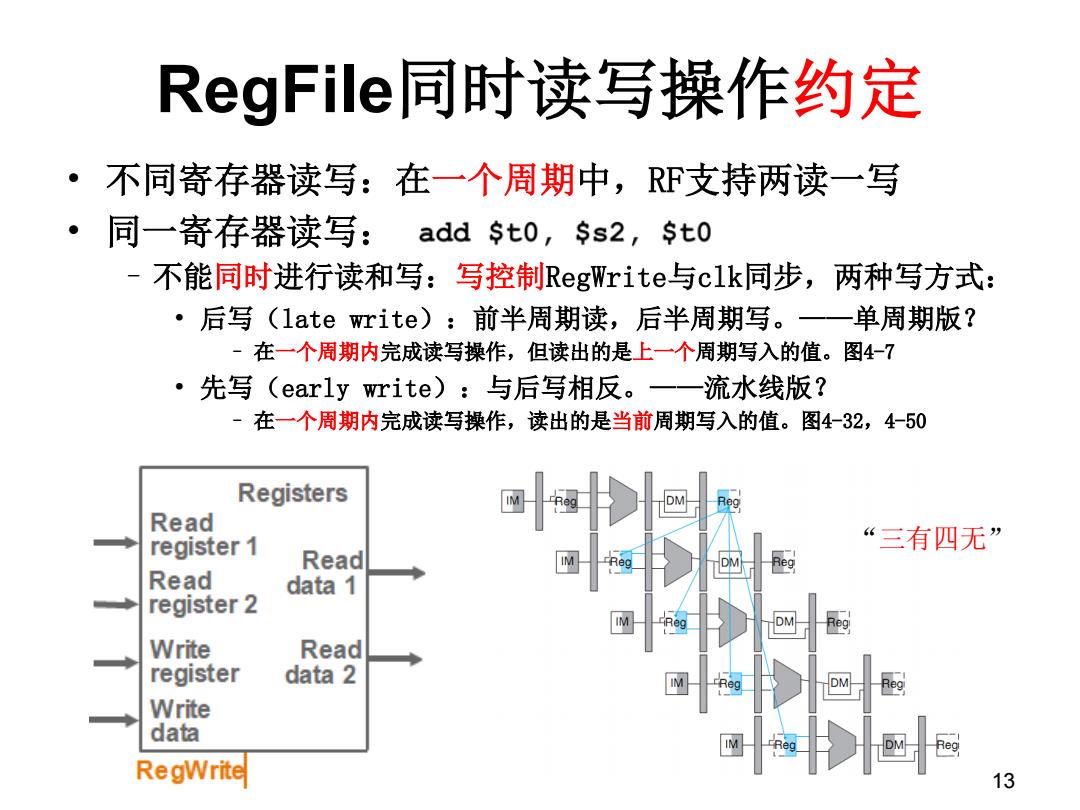

RegFile同时读写操作约定 ·不同寄存器读写:在一个周期中,RF支持两读一写 。 同一寄存器读写:add$t0,$s2,$t0 不能同时进行读和写:写控制RegWrite.与clk同步,两种写方式: ·后写(late write):前半周期读,后半周期写。一一单周期版? -在一个周期内完成读写操作,但读出的是上一个周期写入的值。图4-7 ·先写(early write):与后写相反。一一流水线版? -在一个周期内完成读写操作,读出的是当前周期写入的值。图4-32,4-50 Registers Read register 1 “三有四无” Read Read data 1 register 2 Write Read register data 2 Write data RegWrite 13

RegFile同时读写操作约定 • 不同寄存器读写:在一个周期中,RF支持两读一写 • 同一寄存器读写: –不能同时进行读和写:写控制RegWrite与clk同步,两种写方式: • 后写(late write):前半周期读,后半周期写。——单周期版? – 在一个周期内完成读写操作,但读出的是上一个周期写入的值。图4-7 • 先写(early write):与后写相反。——流水线版? – 在一个周期内完成读写操作,读出的是当前周期写入的值。图4-32,4-50 13 “三有四无

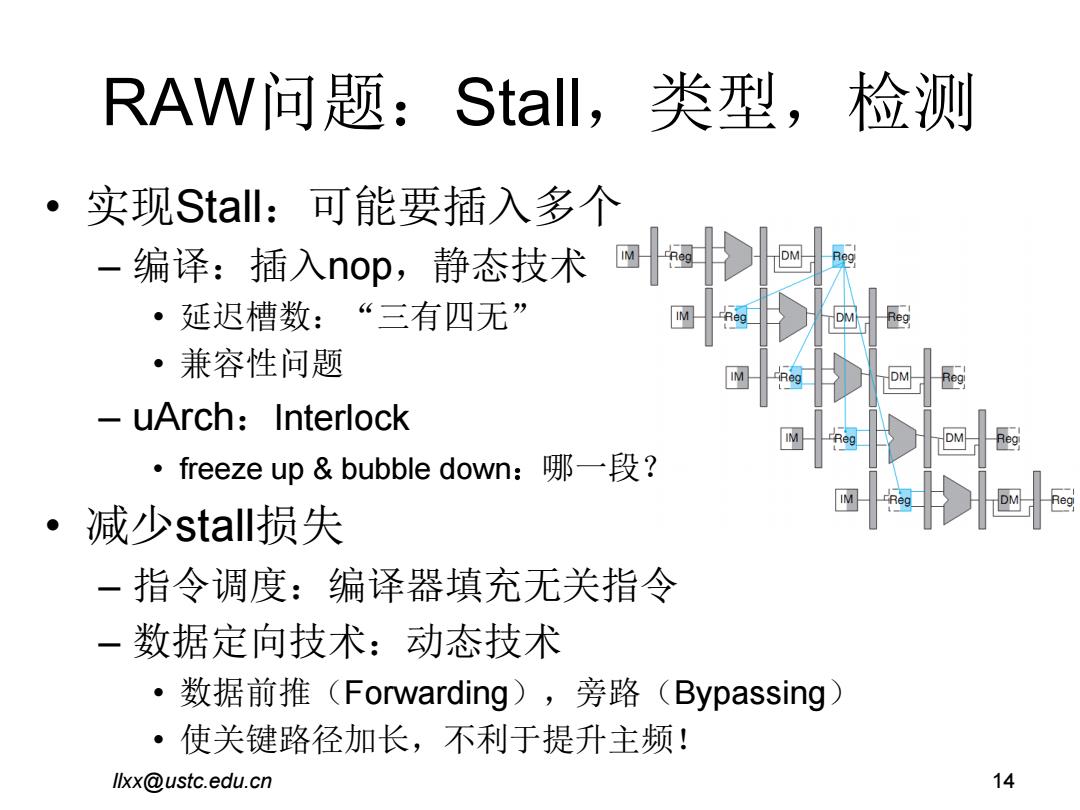

RAW问题:Stall,.类型,检测 实现Stall:可能要插入多个 -纟 编译:插入nop,静态技术 ·延迟槽数:“三有四无” ·兼容性问题 -uArch:Interlock ·freeze up&bubble down:哪一段? ·减少stall损失 一指令调度:编译器填充无关指令 一数据定向技术:动态技术 数据前推(Forwarding),旁路(Bypassing) 。 使关键路径加长,不利于提升主频! llxx@ustc.edu.cn 14

llxx@ustc.edu.cn 14 RAW问题:Stall,类型,检测 • 实现Stall:可能要插入多个 – 编译:插入nop,静态技术 • 延迟槽数:“三有四无” • 兼容性问题 – uArch:Interlock • freeze up & bubble down:哪一段? • 减少stall损失 – 指令调度:编译器填充无关指令 – 数据定向技术:动态技术 • 数据前推(Forwarding),旁路(Bypassing) • 使关键路径加长,不利于提升主频!