1.执行部件(EU) 执行部件主要由寄存器组、算术逻辑部件(ALU)、● 标志寄存器组成,主要负责程序指令的执行。 (1)寄存器组共有8个16位寄存器,这些寄存器均属 于CPU专用存储器,存在于CPU内部,是CPU内部 临时存放数据的部件,它的存取速度比内存更快。 (2)算术逻辑部件(ALU)是用来进行算术和逻辑运 算的。 (3)标志寄存器又称程序状态寄存器,用于存放当 前指令执行的状态和运算结果的特征

1.执行部件(EU) 执行部件主要由寄存器组 执行部件主要由寄存器组、算术逻辑部件(ALU)、 标志寄存器组成,主要负责程序指令的执行。 ⑴ 寄存器组共有8个16位寄存器,这些寄存器均属 这些寄存器均属 于CPU专用存储器,存在于CPU内部,是CPU内部 临时存放数据的部件,它的存取速度比内存更快。 ⑵ 算术逻辑部件(ALU)是用来进行算术和逻辑运 算的。 ⑶ 标志寄存器又称程序状态寄存器,用于存放当 前指令执行的状态和运算结果的特征。 6

2.总线接口部件(BIU) 总线接口部件用来执行所有的总线操作。BIU由地址加法 器、段寄存器、指令指针IP、指令队列和总线控制逻 辑组成,负责CPU与存储器或外部设备之间交换数据。 (1)地址加法器是将指令指针IP和段寄存器CS,或将U送 来的偏移量与段寄存器DS形成一个20位的物理地址, 用以从存储器中取出指令或数据。 (2)指令队列是一个6字节的寄存器(8086),最多可存 放6个字节的指令。指令队列是一个先进先出的栈, 当空闲2个指令字节时,BIU自动从存储器中取出指令 存入指令队列中,供U部件使用。 (3)总线控制逻辑是用来控制BIU中各部件的协同操作

2.总线接口部件(BIU) 总线接口部件用来执行所有的总线操作 。BIU由地址加法 器、段寄存器、指令指针IP、指令队列和总线控制逻 辑组成,负责CPU与存储器或外部设备之间交换数据。 ⑴ 地址加法器是将指令指针 地址加法器是将指令指针IP和段寄存器CS,或将EU 送 来的偏移量与段寄存器DS形成一个20位的物理地址, 用以从存储器中取出指令或数据 。 ⑵ 指令队列是一个6字节的寄存器(8086),最多可存 放6个字节的指令。指令队列是一个先进先出的栈, 当空闲 2个指令字节时,BIU自动从存储器中取出指令 自动从存储器中取出指令 存入指令队列中,供EU部件使用。 ⑶ 总线控制逻辑是用来控制BIU中各部件的协同操作 。 7

3.EU与BIU的关系: 执行部件(BU)和总线接口部件(BIU)的操 作是独立进行的,因此可以并行工作。在 EU执行指令过程中,BIU就可以取出指令存 放在指令队列,而当U执行完一条指令后 就可以立刻到指令队列中去取下一条将要 执行的指令。从而节省了CPU因等待到内存 取指令所需要的时间,提高了CPU的利用率, 加快了系统运行速度

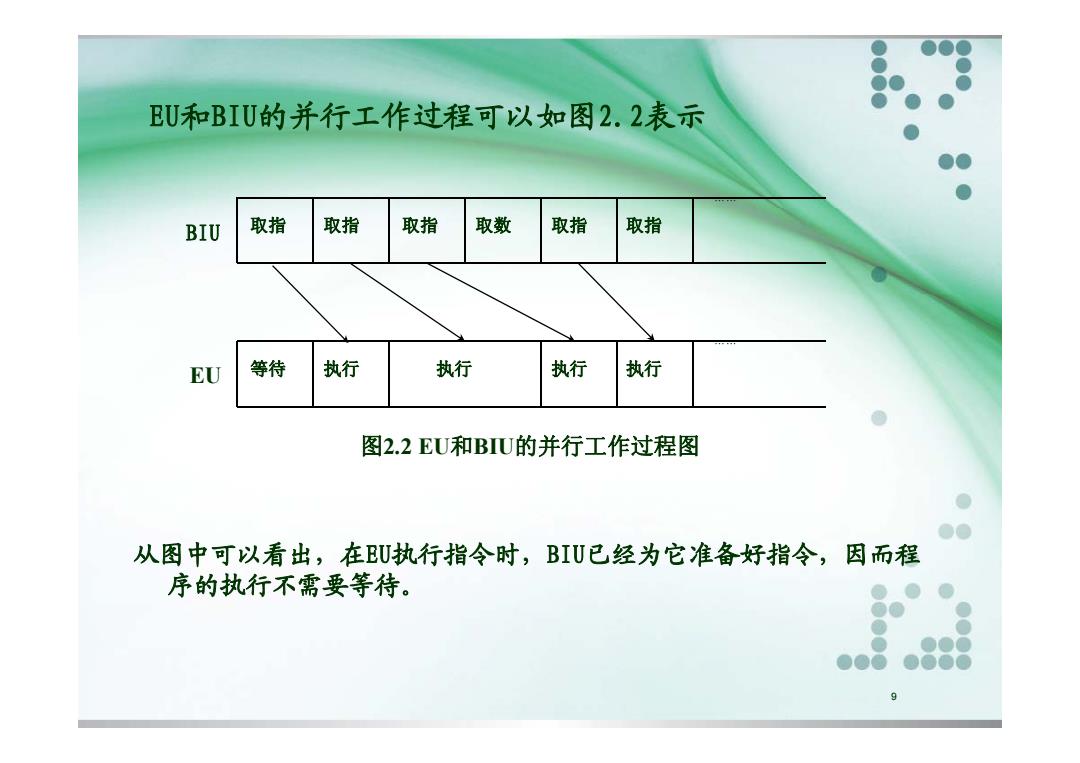

3 .EU与BIU的关系: 执行部件(EU)和总线接口部件(BIU)的操 作是独立进行的,因此可以并行工作。在 EU执行指令过程中,BIU就可以取出指令存 放在指令队列,而当EU执行完一条指令后 就可以立刻到指令队列中去取下一条将要 执行的指令。从而节省了CPU因等待到内存 取指令所需要的时间,提高了CPU的利用率, 加快了系统运行速度。 8

EU和BIU的并行工作过程可以如图2.2表示 BIU 取指 取指 取指 取数 取指 取指 EU 等待 执行 执行 执行 执行 图2.2EU和BU的并行工作过程图 ● 从图中可以看出,在U执行指令时,BIU已经为它准备好指令,因而程 序的执行不需要等待。 9

EU和BIU的并行工作过程可以如图 的并行工作过程可以如图2.2表示 …… 取指 取指 取指 取数 取指 取指 BIU 等待 执行 执行 执行 执行 …… EU 图2.2 EU和BIU的并行工作过程图 从图中可以看出 从图中可以看出,在EU执行指令时,BIU已经为它准备好指令 已经为它准备好指令,因而程 序的执行不需要等待。 9

2.1.2程序执行过程 为了提高CPU的运行速度,8086系统设计为并 行工作方式,即指令和数据的存取电路与 指令的执行电路是并行工作的。假设程序 的指令代码预先已存放在存储器中,为了 执行程序,CPU依据时钟的节拍,产生一系 列控制信号,有规则地重复执行下面的过 程: 80 10

2.1.2程序执行过程 为了提高CPU的运行速度,8086系统设计为并 行工作方式,即指令和数据的存取电路与 指令的执行电路是并行工作的。假设程序 的指令代码预先已存放在存储器中,为了 执行程序,CPU依据时钟的节拍,产生一系 列控制信号,有规则地重复执行下面的过 程: 10