8086/8088CPU的一个基本总线周期由4个时钟周期(T1,T2, T3,T4)组成,时钟周期也称为时钟状态,即T1状态、T2状态、,T3 状态和T4厌态。每一个时钟周期(时钟获态)内完成一些基本操作。 例如: 在T1状态,CPU往数据地址多路复用总线上发出访问存储器或 1/O端口的地址信息。 在T2状态,CPU从总线上撤销地址,若为读周期发出“RD”控制 信号,使数据地址多路复用总线的低8位处于高阻抗状态,以便CPU 足够的时间从输出地址方式转变为输入数据方式,接着在T3二T4 期间,CPU从总线上接收数据。若为写周期发出WR控制信号,由 于输出数据和输出地址都是写总线过程,因而不需要缓冲时间,CPU 在T2T4期间把数据放到总线上。 在T3状态,数据/地址分时复用线的低8位上出现由CPU输出的数 据或为CPU从存储器或I/O端口读入的数据。 在T4状态,8088完成数据传送,是控制信号变为无效,结束总 线周期。 清算和缺 退出 5.1.1

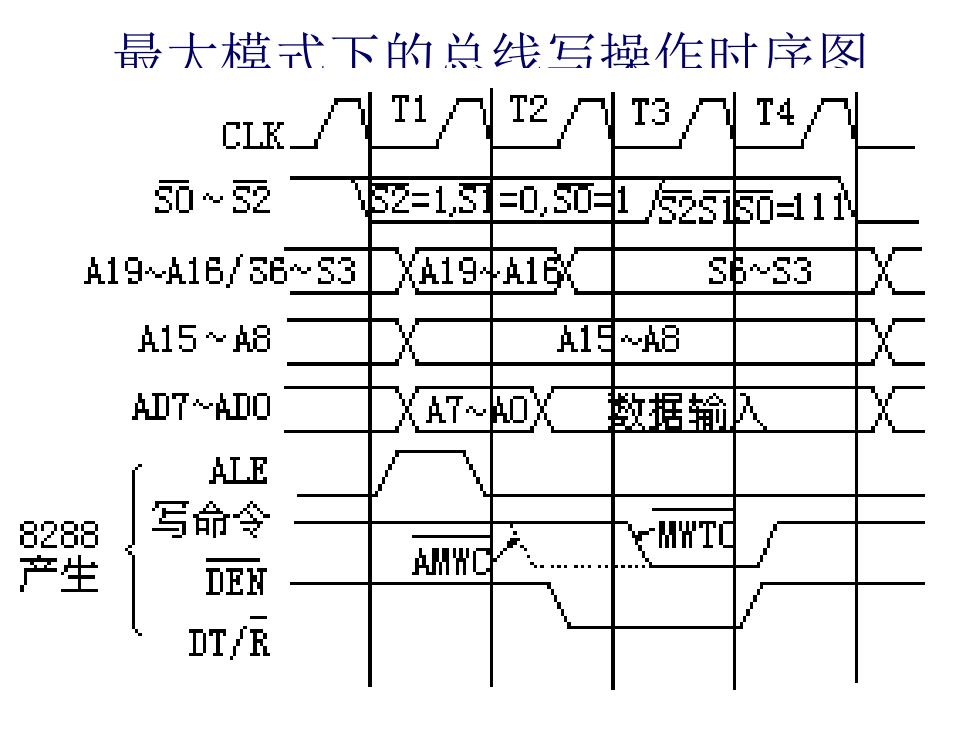

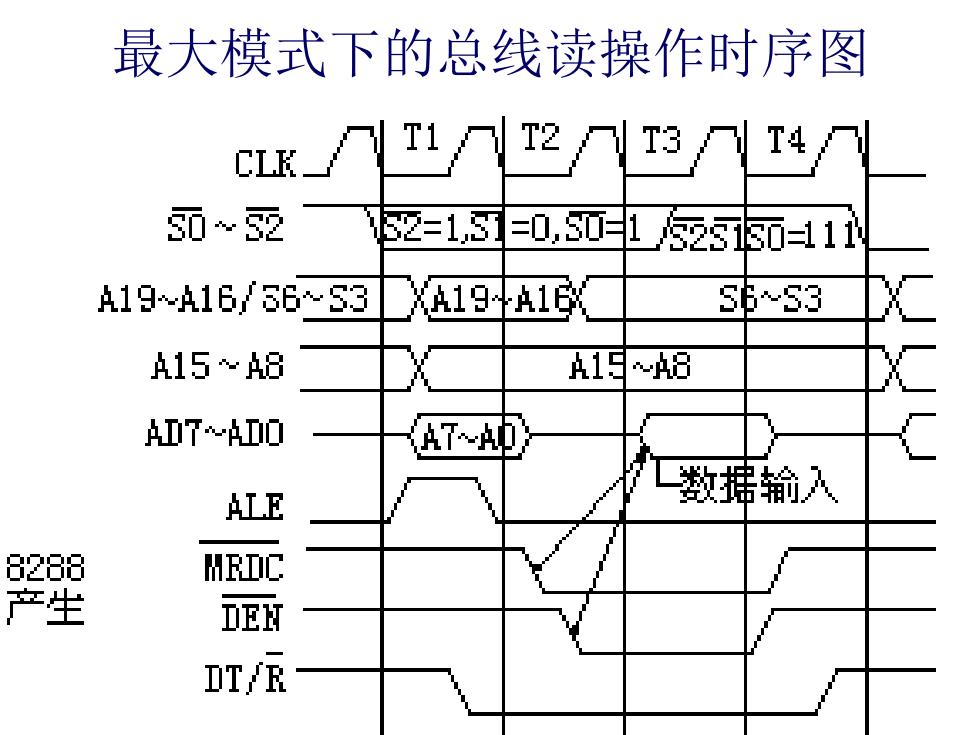

5.1.1 8086/8088CPU的一个基本总线周期由4个时钟周期(T1,T2, T3,T4)组成,时钟周期也称为时钟状态,即T1状态、T2状态、T3 状态和T4状态。每一个时钟周期(时钟状态)内完成一些基本操作。 例如: 在T1状态,CPU往数据/地址多路复用总线上发出访问存储器或 I/O端口的地址信息。 在T2状态,CPU从总线上撤销地址,若为读周期发出“RD”控制 信号,使数据/地址多路复用总线的低8位处于高阻抗状态,以便CPU 有足够的时间从输出地址方式转变为输入数据方式,接着在T3~T4 期间,CPU从总线上接收数据。若为写周期发出“WR”控制信号,由 于输出数据和输出地址都是写总线过程,因而不需要缓冲时间,CPU 在T2~T4期间把数据放到总线上。 在T3状态,数据/地址分时复用线的低8位上出现由CPU输出的数 据或为CPU从存储器或I/O端口读入的数据。 在T4状态,8088完成数据传送,是控制信号变为无效,结束总 线周期。 退 出

最大植式下的总线写操作什序 而2 2=13=0,30123s0-111 A19h16时3633 A194A1正 56w33 A15~A8 A19A8 ADT~ADO XAT~如X数据输 A缸E 8288 写命令 YMWTC 产生 Dek AMWC Dt/R

最大模式下的总线写操作时序图

最大模式下的总线读操作时序图 cKT123列T4 而2 2=13 =0,S012330-111 A19-h16时B653 XA19斗A1 5653 h15h8 A1写h8 ADT~ADO AA ALE 数埽输入 8288 MRDC 产生 DEk DT/R

最大模式下的总线读操作时序图

5.1.2 8088的地址和数据线 AD7~AD0:8位地址/数据总线,分时复用、双向、 三态。 A15A8:地址线,三态输出。 A19/S6~A16/S3:地址/状态线,分时复用、输出、 三态。在总线周期的T1状态作地址线用,A19~A16输出 高4位地址。在总线周期的T2~T4状态作状态线用,S6~ S3输出状态信息,其中:S6恒为0。S5指示中断允许标志 F的当前状态,S5=1,表示当前允许可屏蔽中断请求, S5=0,则禁止一切可屏蔽中断。S4和S3用以指示是哪一 个段寄存器正在使用,其编码和使用的段寄存器如下:00 为ES,01为SS,10为CS,11为DS。 染计算来 退出

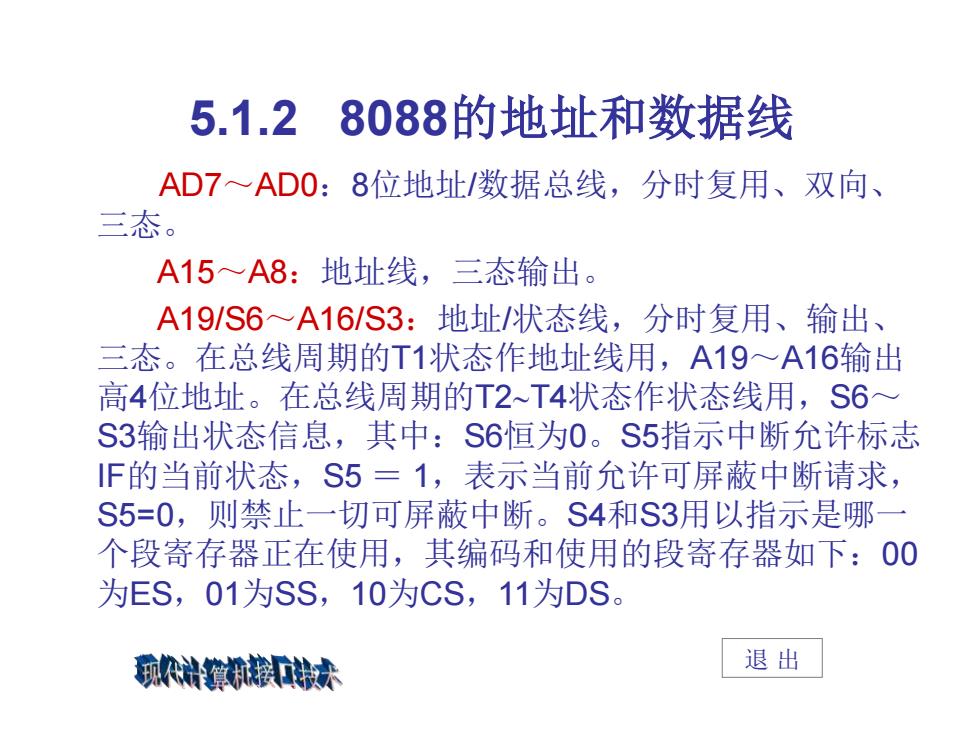

5.1.2 8088的地址和数据线 AD7~AD0:8位地址/数据总线,分时复用、双向、 三态。 A15~A8:地址线,三态输出。 A19/S6~A16/S3:地址/状态线,分时复用、输出、 三态。在总线周期的T1状态作地址线用,A19~A16输出 高4位地址。在总线周期的T2T4状态作状态线用,S6~ S3输出状态信息,其中:S6恒为0。S5指示中断允许标志 IF的当前状态,S5 = 1,表示当前允许可屏蔽中断请求, S5=0,则禁止一切可屏蔽中断。S4和S3用以指示是哪一 个段寄存器正在使用,其编码和使用的段寄存器如下:00 为ES,01为SS,10为CS,11为DS。 退 出

5.1.3微型计算机的基本工作方法 NM:,不可屏蔽中断申请信号,输入,上升沿有效。 不可屏蔽中断申请不受中断允许标志F的影响,.一旦从 NM川引脚收到一个正跳变触发信号,CPU在当前指令执行 完成,便自动引起一个类型码为2的中断,并转入执行与 中断类型码相对应的不可屏蔽中断服务程序。 ITR:可屏蔽中断申请信号,输入、高电平有效。 受CPU内部中断允许标志位的控制。CPU用STI指令可 使中断允许标志F置1,用CL指令可使F清0,从而可实 现中断允许或屏蔽。 RESET:复位信号,输入、高电平有效。 染计算接款 退出

5.1.3 微型计算机的基本工作方法 NMI:不可屏蔽中断申请信号,输入、上升沿有效。 不可屏蔽中断申请不受中断允许标志IF的影响,一旦从 NMI引脚收到一个正跳变触发信号,CPU在当前指令执行 完成,便自动引起一个类型码为2的中断,并转入执行与 中断类型码相对应的不可屏蔽中断服务程序。 INTR:可屏蔽中断申请信号,输入、高电平有效。 受CPU内部中断允许标志位的控制。CPU用STI指令可 使中断允许标志IF置1,用CLI指令可使IF清0,从而可实 现中断允许或屏蔽。 RESET:复位信号,输入、高电平有效。 退 出