电子秒表的设计 一、 实验目的 I、学习数字电路中基本RS触发器、时钟发生 器及计数、译码显示等单元电路的综合应用。 2、学习电子秒表的调试方法,设计60秒计时器

1、学习数字电路中基本RS触发器、时钟发生 器及计数、译码显示等单元电路的综合应用。 2、学习电子秒表的调试方法,设计60秒计时器。 一、实验目的 电子秒表的设计

二、实验仪器和设备 1数字电子实验箱 2.示波器 3.74LS192×2、555×、CC4011×2、电位器、电 阻、电容若干

二、实验仪器和设备 1.数字电子实验箱 2.示波器 3.74LS1922、5551、CC40112、电位器、电 阻、电容若干

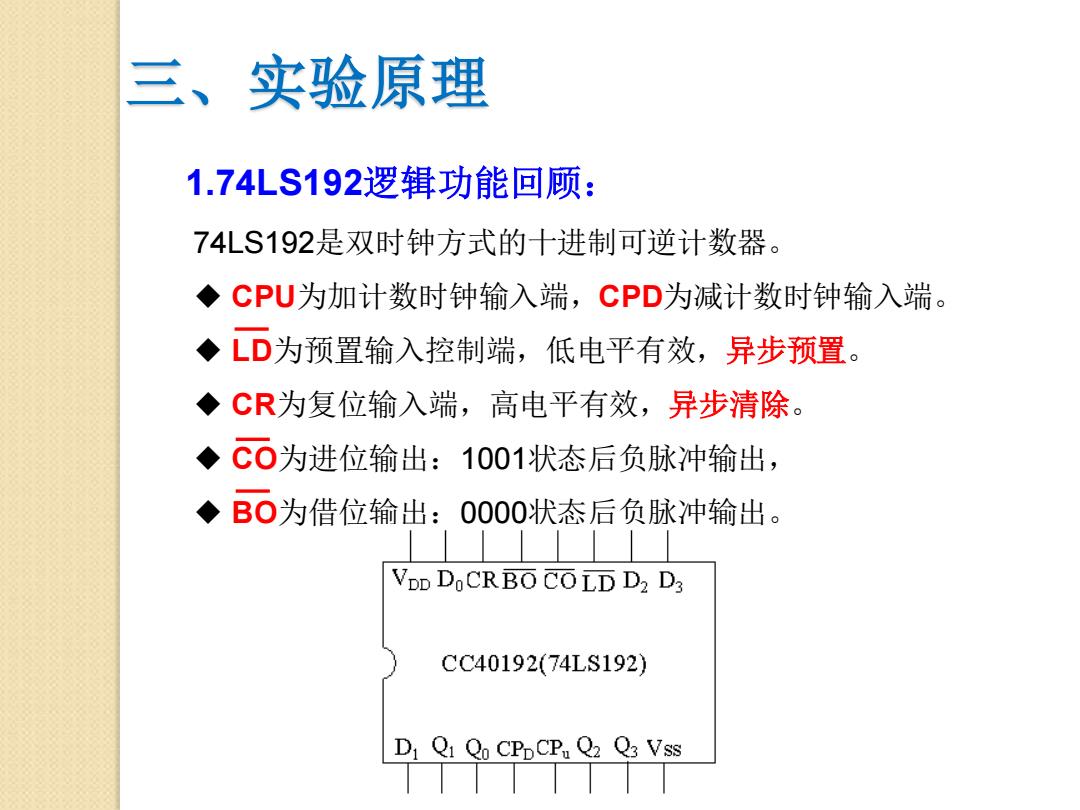

三、实验原理 1.74LS192逻辑功能回顾: 74LS192是双时钟方式的十进制可逆计数器。 ◆CPU为加计数时钟输入端,CPD为减计数时钟输入端。 ◆LD为预置输入控制端,低电平有效,异步预置。 ◆CR为复位输入端,高电平有效,异步清除。 ◆C0为进位输出:1001状态后负脉冲输出, ◆BO为借位输出:0000状态后负脉冲输出。 VDD DoCRBO COLD D2 D3 CC40192(74LS192) D1 Q1 Qo CPDCPu Q2 Q3 Vss

三、实验原理 1.74LS192逻辑功能回顾: 74LS192是双时钟方式的十进制可逆计数器。 ◆ CPU为加计数时钟输入端,CPD为减计数时钟输入端。 ◆ LD为预置输入控制端,低电平有效,异步预置。 ◆ CR为复位输入端,高电平有效,异步清除。 ◆ CO为进位输出:1001状态后负脉冲输出, ◆ BO为借位输出:0000状态后负脉冲输出

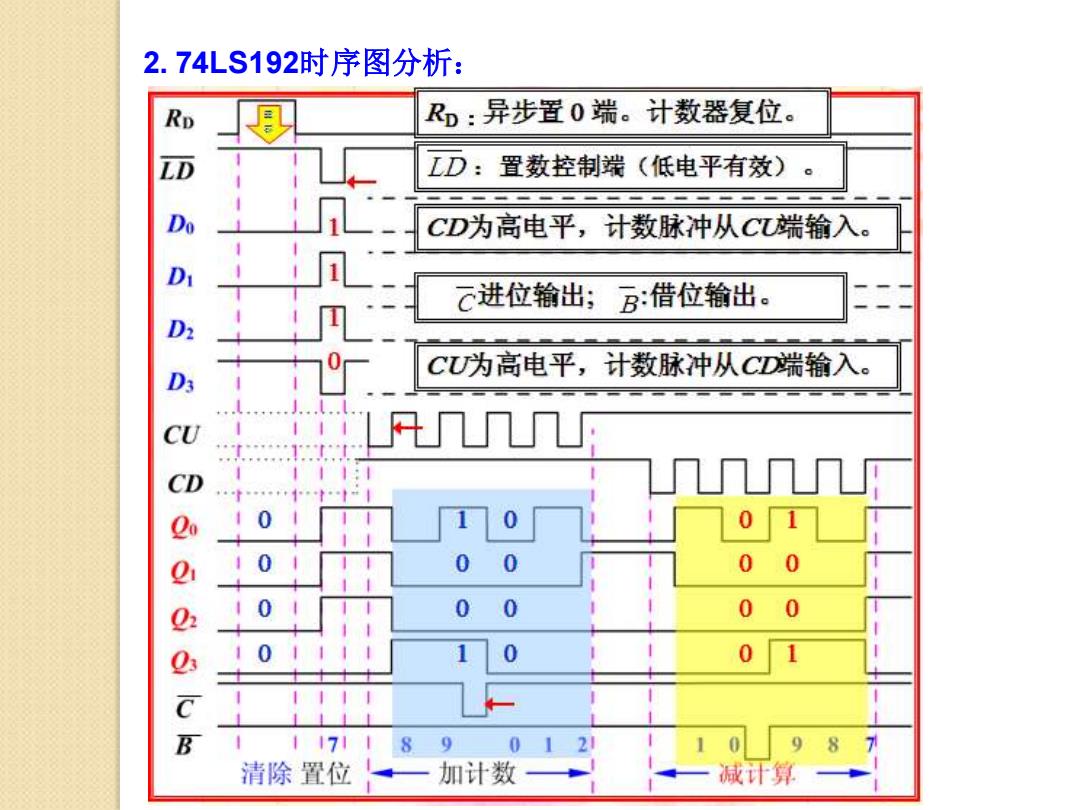

2.74LS192时序图分析: R:异步置0端。计数器复位。 D LD:置数控制端(低电平有效) CD为高电平,计数脉冲从CL端输入。 C进位输出; B:借位输出。 0 CU为高电平,计数脉冲从CD端输入。 0 0 0 0 0 0 0 0 0 0 0 0 11711 0 清除置位 加计数 减计算

2. 74LS192时序图分析:

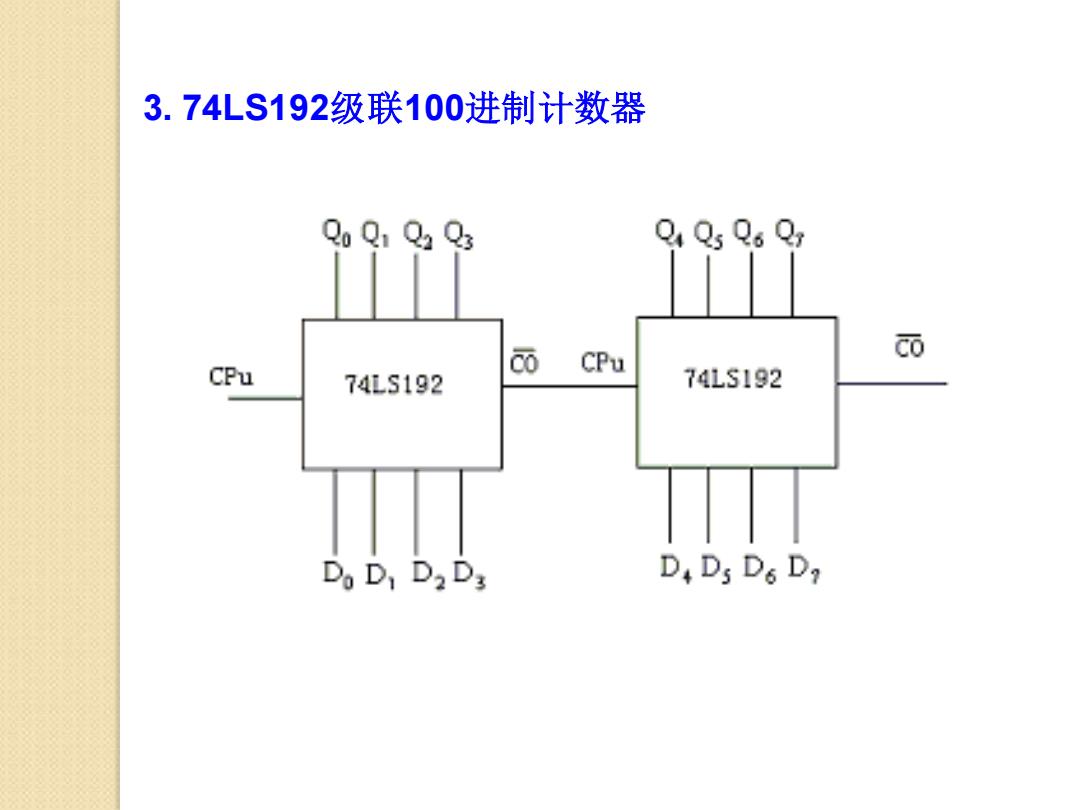

3.74LS192级联100进制计数器 Qo Q:Q2 Q3 Q Q5 Q6 Q CPu 而 CPu 741S192 741S192 Do D D2D3 D Ds D6 D2

3. 74LS192级联100进制计数器