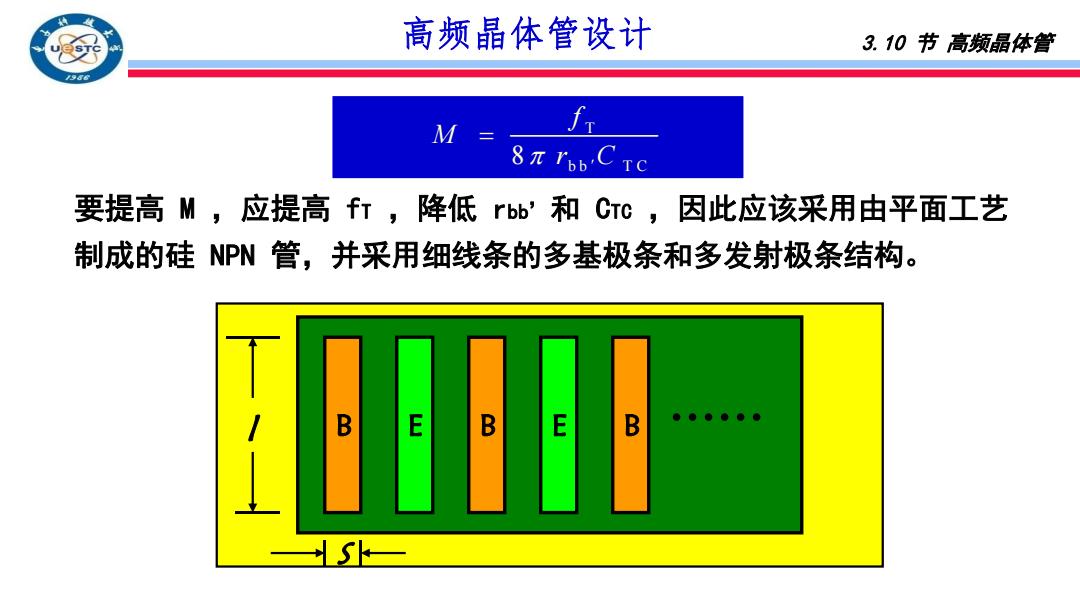

高频晶体管设计 3.10节高频晶体管 M= 8πr6bCTc 要提高M,应提高fr,降低 rbb'和Cc,因此应该采用由平面工艺 制成的硅NPN管,并采用细线条的多基极条和多发射极条结构。 B E B E B ●●●●

要提高 M ,应提高 fT ,降低 rbb’和 CTC ,因此应该采用由平面工艺 制成的硅 NPN 管,并采用细线条的多基极条和多发射极条结构。 T b b T C 8 f M r C S l B E B E B …… 高频晶体管设计 3.10 节 高频晶体管

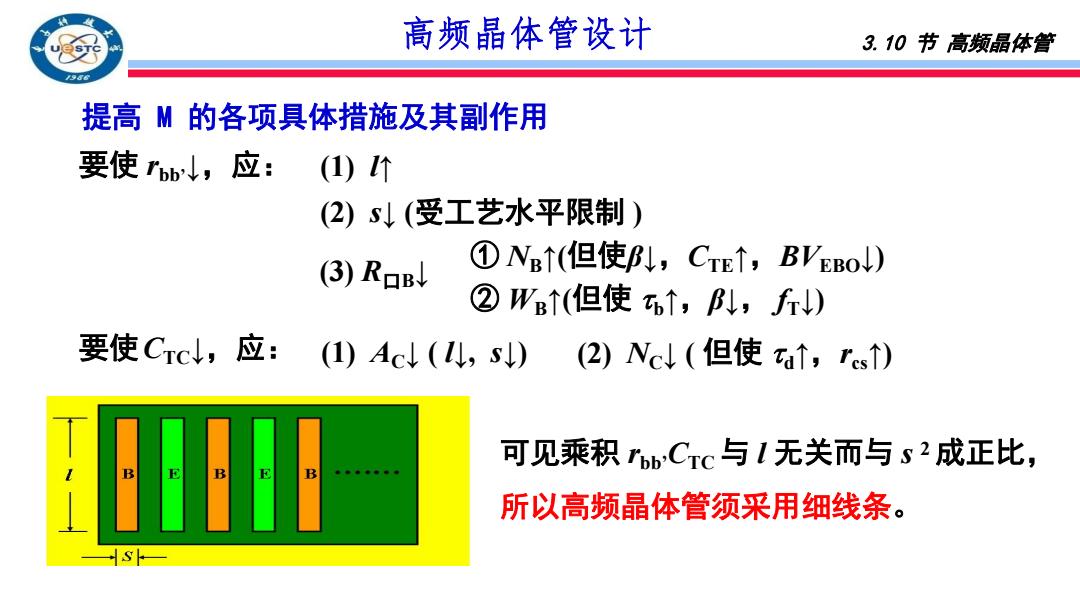

高频晶体管设计 3.10节高频晶体管 提高M的各项具体措施及其副作用 要使rb↓,应:(1)个 (2)s(受工艺水平限制) (3)RaB↓ ①NB↑(但使,CrE↑,BVEBOS) ②WB↑(但使↑,BL,f) 要使CTC,应: (1)Ac↓(,s) (2)Nc↓(但使↑,rs) 可见乘积rbb,CTC与1无关而与s2成正比, 所以高频晶体管须采用细线条

提高 M 的各项具体措施及其副作用 要使 rbb’↓,应: (1) l↑ (2) s↓ (受工艺水平限制 ) (3) R口B↓ ① NB↑(但使β↓,CTE↑,BVEBO↓) ② WB↑(但使 b↑,β↓, fT↓) 要使CTC↓,应: (1) AC↓ ( l↓, s↓) (2) NC↓ ( 但使 d↑,rcs↑) 可见乘积 rbb’CTC与 l 无关而与 s 2成正比, 所以高频晶体管须采用细线条。 高频晶体管设计 3.10 节 高频晶体管

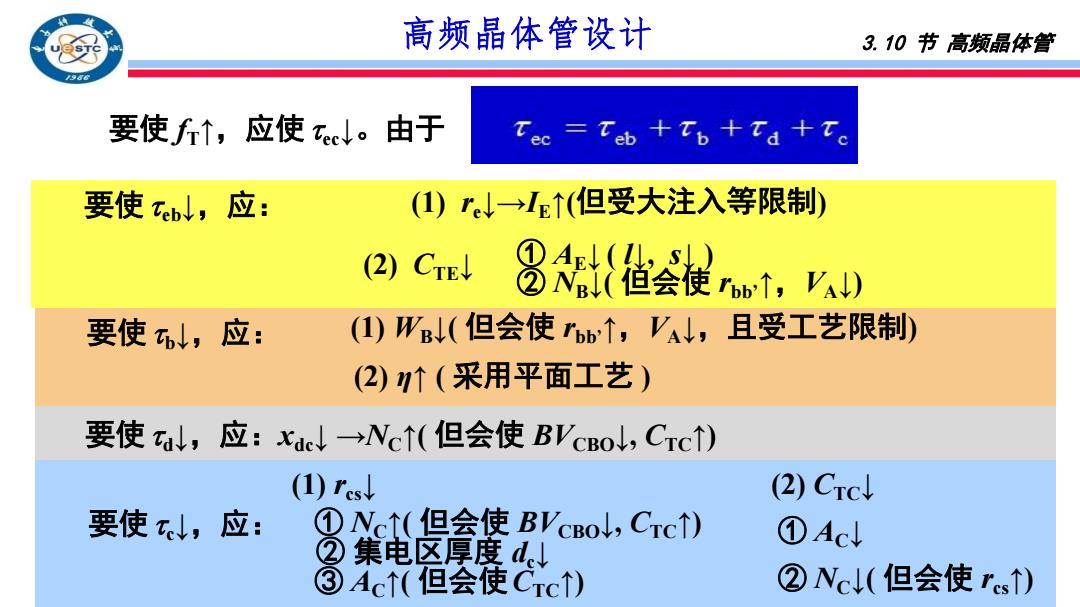

高频晶体管设计 3.10节高频晶体管 要使f个,应使ec↓。由于 Tec Teb +tb+td +tc 要使eb,应: (1)re↓→↑(但受大注入等限制) (2)CTE↓ 贯省会使,人心 要使,应: (1)WB(但会使rb↑,VAN,且受工艺限制) (2)个(采用平面工艺)》 要使al,应:xac↓→Nc↑(但会使B'cBoN,CTc) (1)rest (2)Crc↓ 要使↓,应: ①Nct(但会使BVCBO,CrC↑) ②集电区厚度d↓ ①Ac↓ ③Ac↑(但会使Crc) ②NcJ(但会使r↑)

要使c↓,应: 要使d↓,应:xdc↓ →NC↑( 但会使 BVCBO↓, CTC↑) (1) rcs↓ ① NC↑( 但会使 BVCBO↓, CTC↑) ② 集电区厚度 dc↓ ③ AC↑( 但会使CTC↑) (2) CTC↓ ① AC↓ ② NC↓( 但会使 rcs↑) 要使eb↓,应: (1) re↓→IE↑(但受大注入等限制) (2) CTE↓ ① AE↓ ( l↓, s↓ ) ② NB↓( 但会使 rbb’↑,VA↓) 要使b↓,应: (1) WB↓( 但会使 rbb’↑,VA↓,且受工艺限制) (2) η↑ ( 采用平面工艺 ) 要使 fT↑,应使ec↓。由于 高频晶体管设计 3.10 节 高频晶体管

高频晶体管设计 3.10节高频晶体管 几个主要矛盾 (1)对W的要求 一般情况下应减小WB。但当W减小到,不再是c的主要部分 时,再减小W对继续减小c已作用不大,而对b的增大作用却不 变。同时工艺上的难度也越来越大

一般情况下应减小WB 。但当WB减小到 b 不再是 ec 的主要部分 时,再减小WB 对继续减小ec 已作用不大,而对 rbb’的增大作用却不 变。同时工艺上的难度也越来越大。 几个主要矛盾 (1) 对 WB的要求 高频晶体管设计 3.10 节 高频晶体管

高频晶体管设计 3.10节高频晶体管 (2)对%的要求 减小rb'与减小b及增大B对%有相矛盾的要求。可通过采用 无源基区(非工作基区)重掺杂来缓解。这可降低R妇3,从而减小 rbb'中的on与rcb,但不会影响tob与B。 n

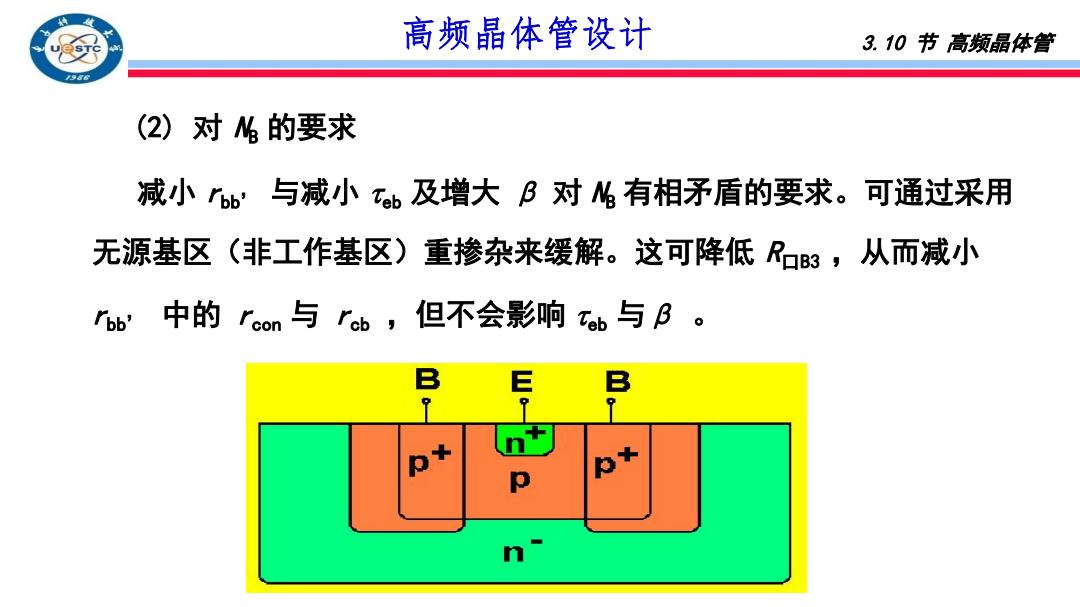

(2) 对 NB 的要求 减小 rbb’ 与减小 eb 及增大 β 对 NB 有相矛盾的要求。可通过采用 无源基区(非工作基区)重掺杂来缓解。这可降低 R口B3 ,从而减小 rbb’ 中的 rcon 与 rcb ,但不会影响 eb 与β 。 高频晶体管设计 3.10 节 高频晶体管