2.3C55x的CPU结构 2.3.1存储器接口单元(M单元) ■2.3.2指令缓冲单元(单元) ■2.3.3程序流单元(P单元) CPU的5单元: M-I-P-A-D ■2.3.4地址数据流单元(A单元) ■ 2.3.5数据计算单元(D单元) ■2.3.6内部地址总线与数据总线 ■2.3.7指令流水线 39

2.3 C55x的CPU结构 ◼ 2.3.1 存储器接口单元(M单元) ◼ 2.3.2 指令缓冲单元(I单元) ◼ 2.3.3 程序流单元(P单元) ◼ 2.3.4 地址数据流单元(A单元) ◼ 2.3.5 数据计算单元(D单元) ◼ 2.3.6 内部地址总线与数据总线 ◼ 2.3.7 指令流水线 39 CPU的5单元: M-I-P-A-D

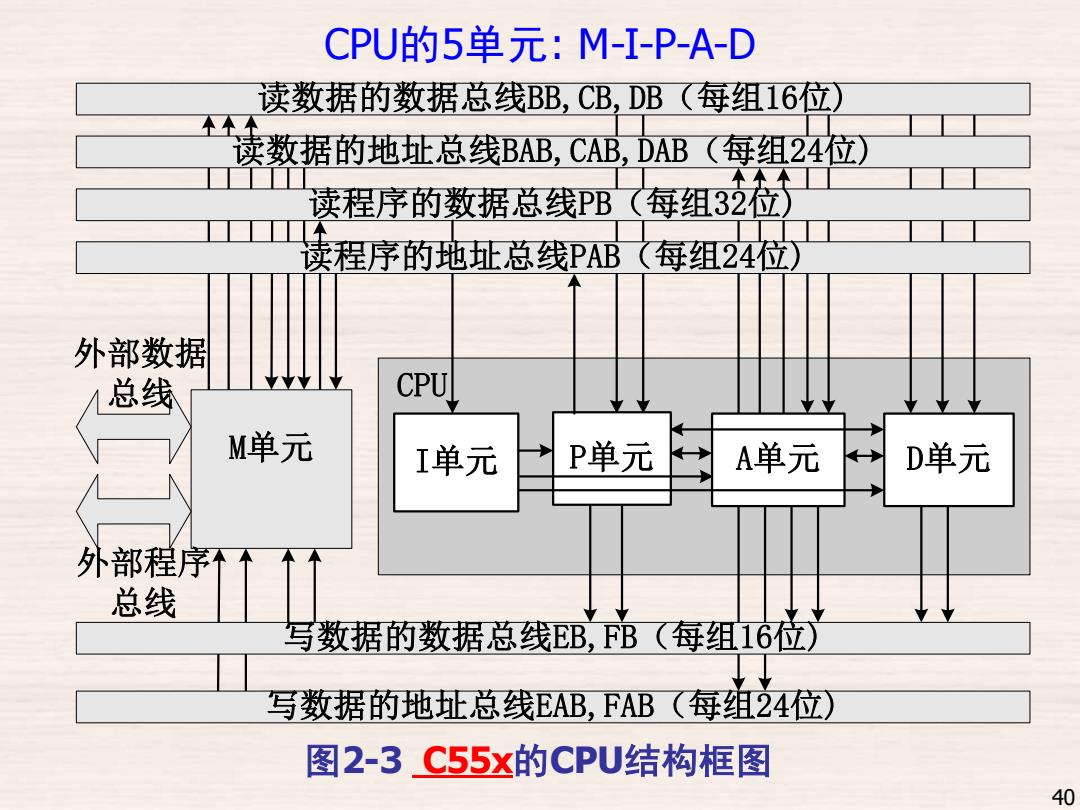

CPU的5单元:M-I-P-A-D 读数据的数据总线BB,CB,DB(每组16位) 读数据的地址总线BAB,CAB,DAB(每组24位) 读程序的数据总线PB(每组32 读程序的地址总线PAB(每组24莅 外部数据 1总线 CPUl M单元 I单元 P单元 A单元 D单元 外部程序干 总线 写数据的数据总线EB,FB(每组16位) 写数据的地址总线EAB,FAB(每组24位) 图2-3C55x的CPU结构框图 40

图2-3 C55x的CPU结构框图 读数据的数据总线BB,CB,DB(每组16位) 读程序的数据总线PB(每组32位) 读数据的地址总线BAB,CAB,DAB(每组24位) M单元 I单元 P单元 A单元 D单元 写数据的地址总线EAB,FAB(每组24位) 写数据的数据总线EB,FB(每组16位) CPU 外部数据 总线 外部程序 总线 读程序的地址总线PAB(每组24位) 40 CPU的5单元: M-I-P-A-D

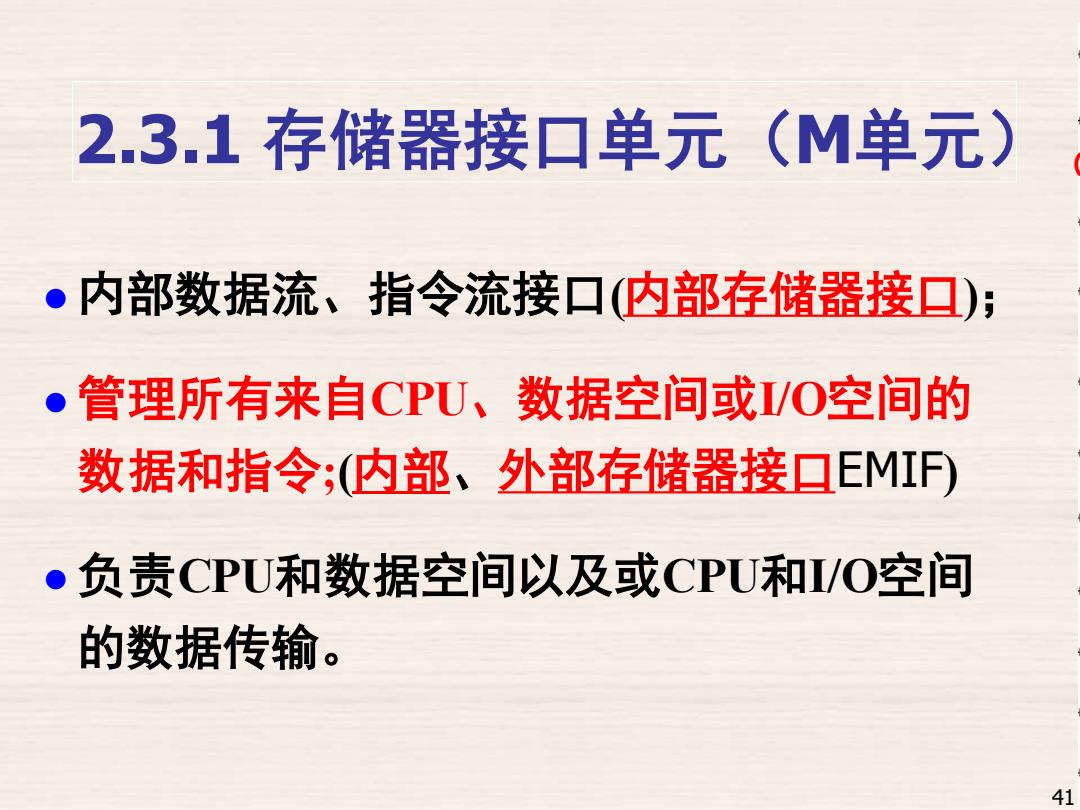

2.3.1存储器接口单元(M单元) ●内部数据流、指令流接口(内部存储器接口); 管理所有来自CPU、数据空间或/O空间的 数据和指令;(内部、外部存储器接口EMI) 负责CPU和数据空间以及或CPU和I/O空间 的数据传输。 41

2.3.1 存储器接口单元(M单元) ⚫ 内部数据流、指令流接口(内部存储器接口); ⚫ 管理所有来自CPU、数据空间或I/O空间的 数据和指令;(内部、外部存储器接口EMIF) ⚫ 负责CPU和数据空间以及或CPU和I/O空间 的数据传输。 41 (EMIF) (M (M

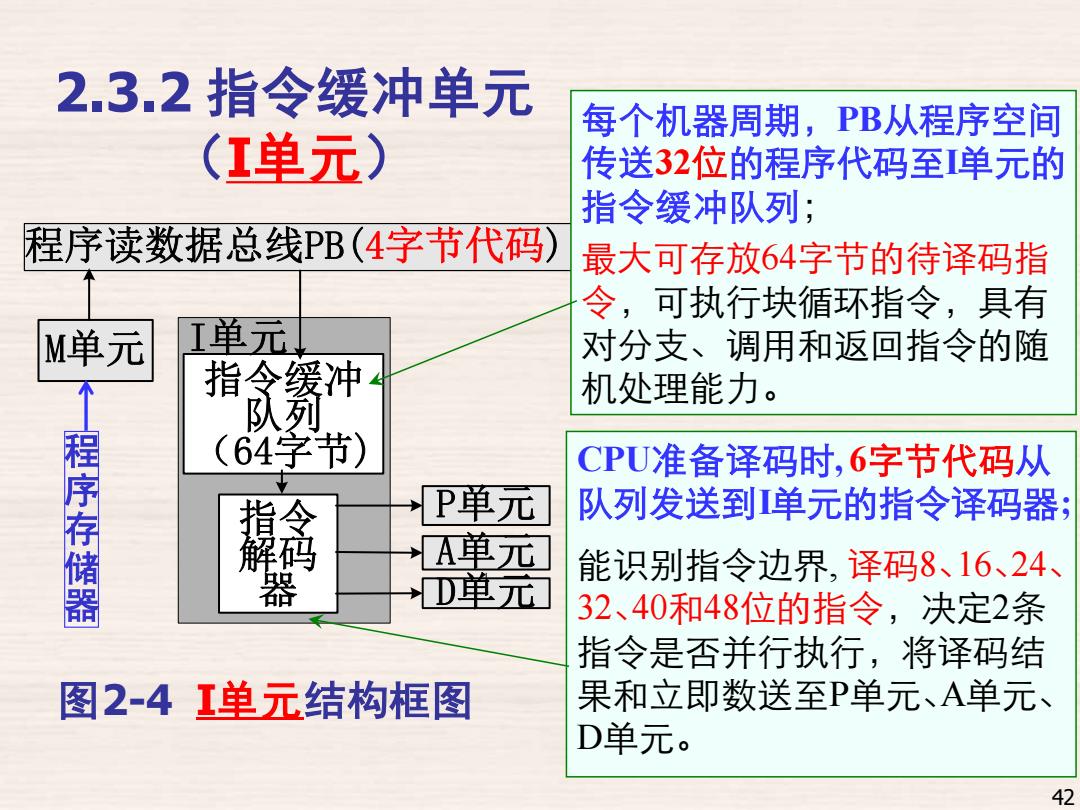

2.3.2指令缓冲单元 每个机器周期,PB从程序空间 (红单元) 传送32位的程序代码至I单元的 指令缓冲队列; 程序读数据总线PB(4字节代码) 最大可存放64字节的待译码指 令,可执行块循环指令,具有 M单元 I单元 对分支、调用和返回指令的随 指令缓冲 队列 机处理能力。 64字节) 程序存储器 CPU准备译码时,6字节代码从 指念 P单元 队列发送到单元的指令译码器; A单元 能识别指令边界,译码8、16、24、 器 D单元 32、40和48位的指令,决定2条 指令是否并行执行,将译码结 图2-4I单元结构框图 果和立即数送至P单元、A单元、 D单元。 42

2.3.2 指令缓冲单元 (I单元) 程序读数据总线PB(4字节代码) M单元 指令缓冲 队列 (64字节) 指令解码 器 P单元 A单元 D单元 I单元 图2-4 I单元结构框图 每个机器周期,PB从程序空间 传送32位的程序代码至I单元的 指令缓冲队列; 最大可存放64字节的待译码指 令,可执行块循环指令,具有 对分支、调用和返回指令的随 机处理能力。 CPU准备译码时, 6字节代码从 队列发送到I单元的指令译码器; 能识别指令边界, 译码8、16、24、 32、40和48位的指令,决定2条 指令是否并行执行,将译码结 果和立即数送至P单元、A单元、 D单元。 42 程 序 存 储 器

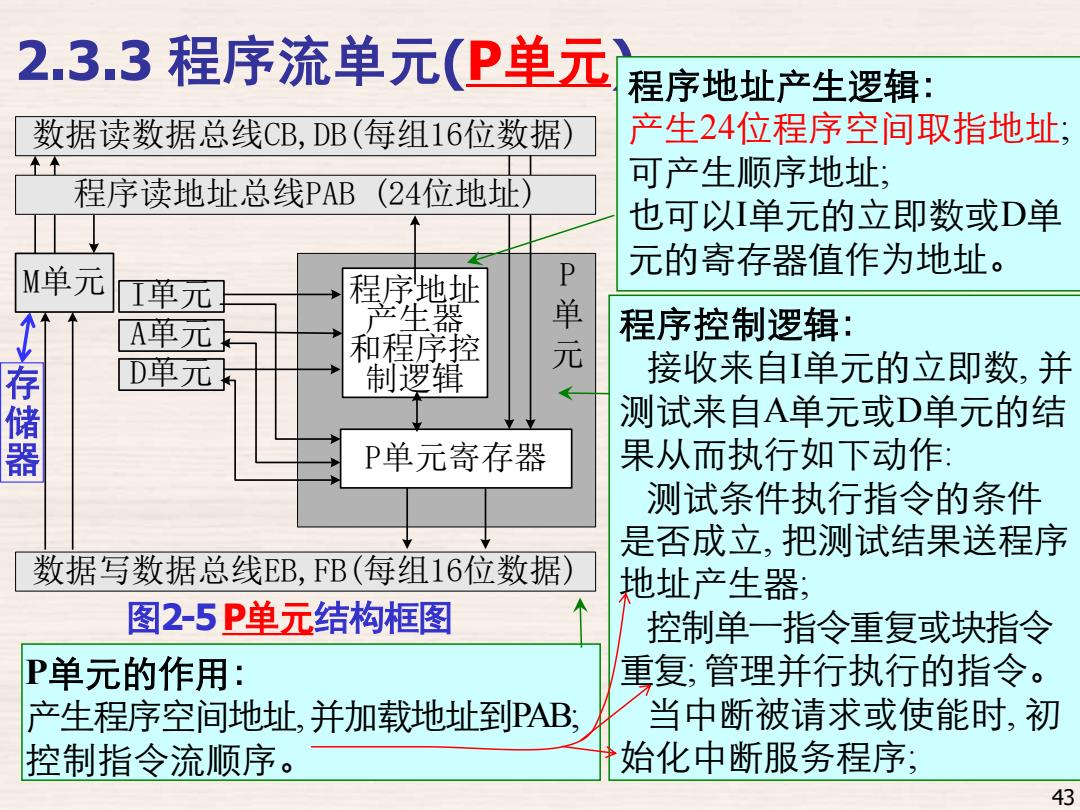

2.3.3程序流单元(P单元 程序地址产生逻辑: 数据读数据总线CB,DB(每组16位数据) 产生24位程序空间取指地址: 可产生顺序地址, 程序读地址总线PAB(24位地址】 也可以I单元的立即数或D单 M单元 P 元的寄存器值作为地址。 单元 程序地址 A单元 产生器 单 程序控制逻辑: 存储器 和程序控 D单元 元 制逻辑 接收来自I单元的立即数,并 测试来自A单元或D单元的结 P单元寄存器 果从而执行如下动作: 测试条件执行指令的条件 是否成立,把测试结果送程序 数据写数据总线EB,FB(每组16位数据) 地址产生器; 图2-5P单元结构框图 控制单一指令重复或块指令 P单元的作用: 重复;管理并行执行的指令。 产生程序空间地址,并加载地址到PAB, 当中断被请求或使能时,初 控制指令流顺序。 始化中断服务程序; 43

P单元的作用: 产生程序空间地址, 并加载地址到PAB; 控制指令流顺序。 2.3.3 程序流单元(P单元) 数据读数据总线CB,DB(每组16位数据) M单元 程序地址 产生器 和程序控 制逻辑 P单元寄存器 I单元 A单元 D单元 数据写数据总线EB,FB(每组16位数据) 程序读地址总线PAB (24位地址) P 单 元 程序地址产生逻辑: 产生24位程序空间取指地址; 可产生顺序地址; 也可以I单元的立即数或D单 元的寄存器值作为地址。 程序控制逻辑: 接收来自I单元的立即数, 并 测试来自A单元或D单元的结 果从而执行如下动作: 测试条件执行指令的条件 是否成立, 把测试结果送程序 地址产生器; 控制单一指令重复或块指令 重复; 管理并行执行的指令。 当中断被请求或使能时, 初 始化中断服务程序; 图2-5 P单元结构框图 43 存 储 器