第七章 基本逻辑电路设计

第七章 基本逻辑电路设计

主要内容 。组合逻辑电路和时序逻辑的概念; ·组合逻辑电路设计实例; ·时序逻辑电路设计实例

主要内容 • 组合逻辑电路和时序逻辑的概念; • 组合逻辑电路设计实例; • 时序逻辑电路设计实例

基本概念 数逻辑电路主要分为组合逻辑电路与时序逻辑 电路两类 ·两者都拥有一个或者多个输入信号和输出信号, 但是组合逻辑电路的输出只与当前的输入相关, 而时序逻辑电路的输出不仅与现在的输入信号相 关,而且与过去的输入信号相关: ● 两种逻辑电路都是数字电路系统的重要基本组成 部分,是数字系统电路的基本元素

基本概念 • 数字逻辑电路主要分为组合逻辑电路与时序逻辑 电路两类 ; • 两者都拥有一个或者多个输入信号和输出信号, 但是组合逻辑电路的输出只与当前的输入相关, 而时序逻辑电路的输出不仅与现在的输入信号相 关,而且与过去的输入信号相关; • 两种逻辑电路都是数字电路系统的重要基本组成 部分,是数字系统电路的基本元素

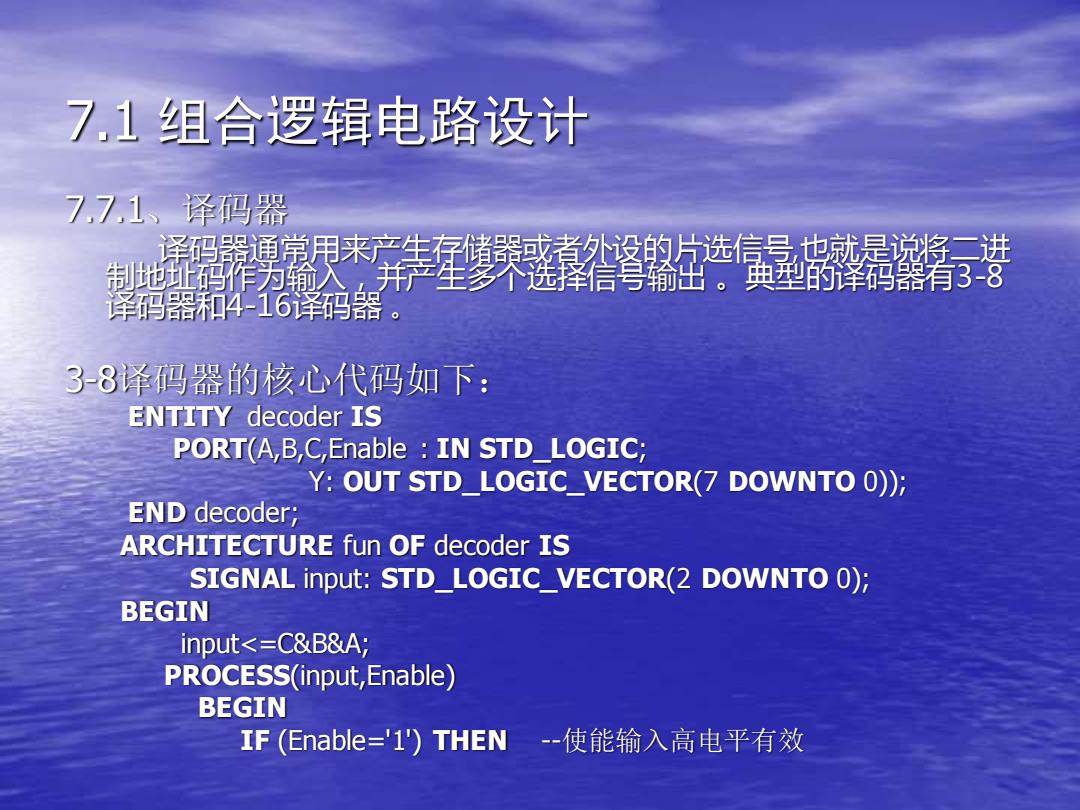

7.1组合逻辑电路设计 7,7,1、译码器 界养星靠警鲍萨鼠霸湾 制地址码作为输入」 译码需和416译码器。 3-8译码器的核心代码如下: ENTITY decoder IS PORT(A,B,C,Enable IN STD_LOGIC; Y:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder; ARCHITECTURE fun OF decoder IS SIGNAL input:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN input<=C&B&A; PROCESS(input,Enable) BEGIN IF(Enable:='1)THEN-使能输入高电平有效

7.1 组合逻辑电路设计 7.7.1、译码器 译码器通常用来产生存储器或者外设的片选信号,也就是说将二进 制地址码作为输入,并产生多个选择信号输出 。典型的译码器有3-8 译码器和4-16译码器 。 3-8译码器的核心代码如下: ENTITY decoder IS PORT(A,B,C,Enable : IN STD_LOGIC; Y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END decoder; ARCHITECTURE fun OF decoder IS SIGNAL input: STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN input<=C&B&A; PROCESS(input,Enable) BEGIN IF (Enable='1') THEN --使能输入高电平有效

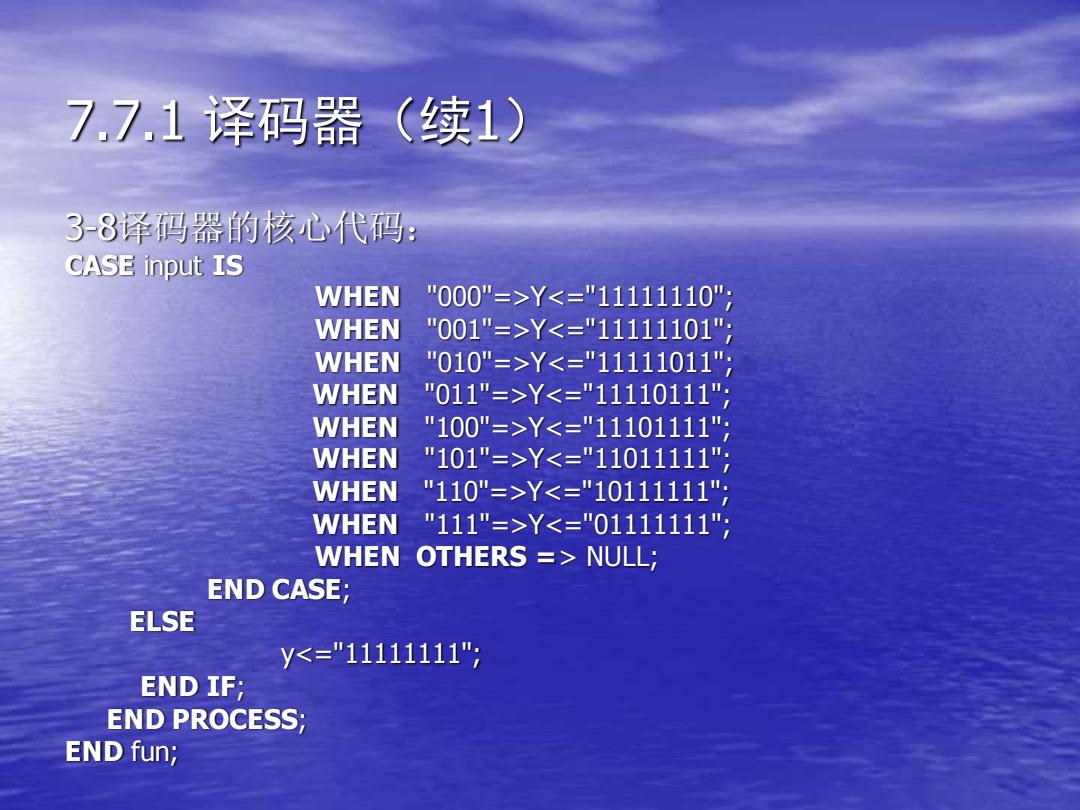

7.7.1译码器 (续1) 3-8译码器的核心代码: CASE input IS WHEN"000"=>Y<="11111110" WHEN"001"=>Y<="11111101" WHEN"010"=>Y<="11111011" WHEN"011"=>Y<="11110111", WHEN"100"=>Y<="11101111" WHEN"101"=>Y<="11011111" WHEN"110"=>Y<="10111111", WHEN"111"=>Y<="01111111" WHEN OTHERS =NULL; END CASE; ELSE y<="11111111": END IF; END PROCESS; END fun;

7.7.1 译码器(续1) 3-8译码器的核心代码: CASE input IS WHEN "000"=>Y<="11111110"; WHEN "001"=>Y<="11111101"; WHEN "010"=>Y<="11111011"; WHEN "011"=>Y<="11110111"; WHEN "100"=>Y<="11101111"; WHEN "101"=>Y<="11011111"; WHEN "110"=>Y<="10111111"; WHEN "111"=>Y<="01111111"; WHEN OTHERS => NULL; END CASE; ELSE y<="11111111"; END IF; END PROCESS; END fun;