第9章C55x的硬件扩展 9.1硬件设计概述 9.2DSP系统的基本电路设计 ■9.3外部程序存储器扩展 ■9.4外部数据存储器扩展 ■9.5C55x与A/D和D/A转换器的接▣ 13

第9章 C55x的硬件扩展 ◼9.1 硬件设计概述 ◼9.2 DSP系统的基本电路设计 ◼9.3 外部程序存储器扩展 ◼9.4 外部数据存储器扩展 ◼9.5 C55x与A/D和D/A转换器的接口 13

9.2DSP系统的基本电路设计 ■9.2.1JTAG接口 ■9.2.2电源电路 ■9.2.3复位电路 ■9.2.4时钟信号的产生 14

9.2 DSP系统的基本电路设计 ◼ 9.2.1 JTAG接口 ◼ 9.2.2 电源电路 ◼ 9.2.3 复位电路 ◼ 9.2.4 时钟信号的产生 14

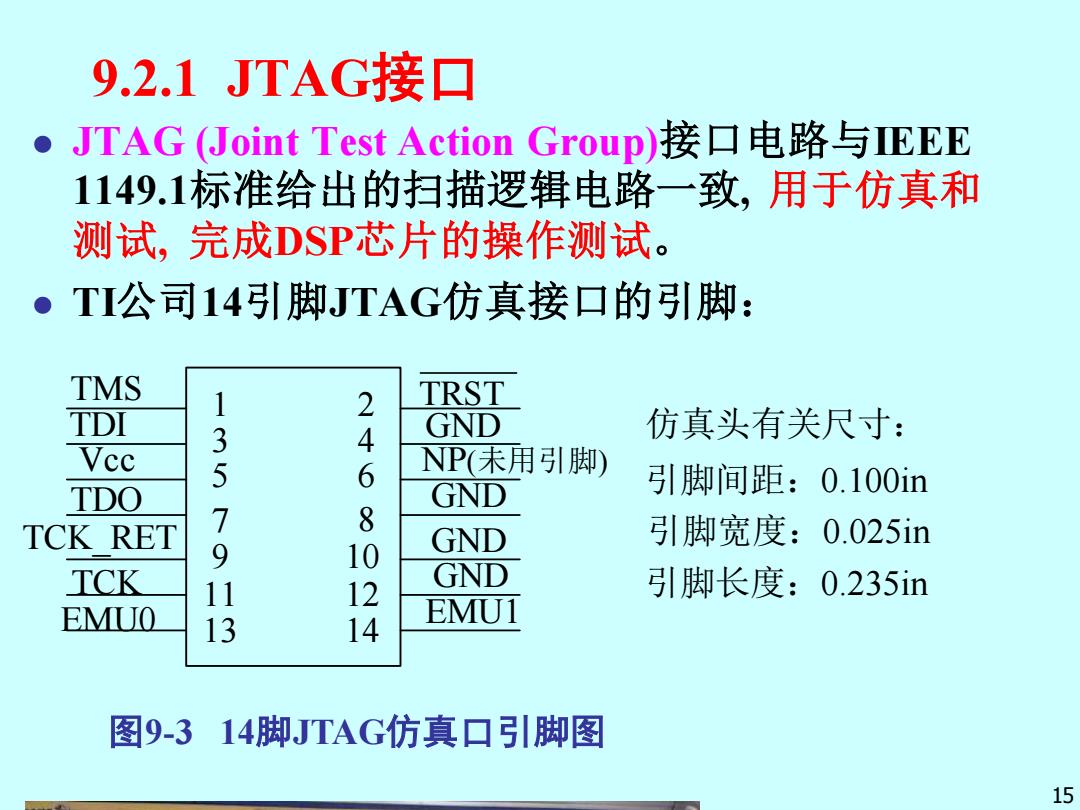

9.2.1JTAG接口 ●JTAG(Joint Test Action Group)接口电路与IEEE 1149.1标准给出的扫描逻辑电路一致,用于仿真和 测试,完成DSP芯片的操作测试。 。TI公司14引脚JTAG仿真接口的引脚: TMS 1 TRST TDI 3 24 GND 仿真头有关尺寸: Vcc 5 6 NP(未用引脚) GND 引脚间距:0.100in TDO 7 8 TCK RET 脚宽度:0.025in 9 10 GND TCK 11 1 GND 引脚长度:0.235in EMUO 13 14 EMUI 图9-314脚JTAG仿真口引脚图 15

9.2.1 JTAG接口 ⚫ JTAG (Joint Test Action Group)接口电路与IEEE 1149.1标准给出的扫描逻辑电路一致, 用于仿真和 测试, 完成DSP芯片的操作测试。 ⚫ TI公司14引脚JTAG仿真接口的引脚: TMS 1 2 3 5 4 7 9 11 13 6 8 10 12 14 TDI Vcc TDO TCK_RET TCK EMU0 EMU1 GND GND GND GND NP(未用引脚) TRST 仿真头有关尺寸: 引脚间距:0.100in 引脚宽度:0.025in 引脚长度:0.235in 图9-3 14脚JTAG仿真口引脚图 15

9.2.1JTAG接口 JTAG连接器各引脚信号的含义(补充) 信号名称 引脚 含义 仿真器 设备 序号 状态 状态 TMS 1 测试模式选择Test mode select 输出(O) 输入(① TDI 3 测试数据输入Test data input 输出(O) 输入① TDO 7 测试数据输出Test data output 输入①) 输出 (O) TCK 11 Test clock,从仿真器输出的一 输出(O) 输入() 个10.368MHz的时钟信号。 TCK RET 9 Test clock return测试时钟返回,输入①) 输出 进入仿真器的测试时钟,是 (O) TCK的缓冲版本。 16

JTAG连接器各引脚信号的含义(补充) 9.2.1 JTAG接口 信号名称 引脚 序号 含义 仿真器 状态 设备 状态 TMS 1 测试模式选择Test mode select 输出(O) 输入(I) TDI 3 测试数据输入Test data input 输出(O) 输入(I) TDO 7 测试数据输出Test data output 输入(I) 输出 (O) TCK 11 Test clock, 从仿真器输出的一 个 10.368MHz的时钟信号。 输出(O) 输入(I) TCK_RET 9 Test clock return测试时钟返回, 进入仿真器的测试时钟,是 TCK的缓冲版本。 输入(I) 输出 (O) 16

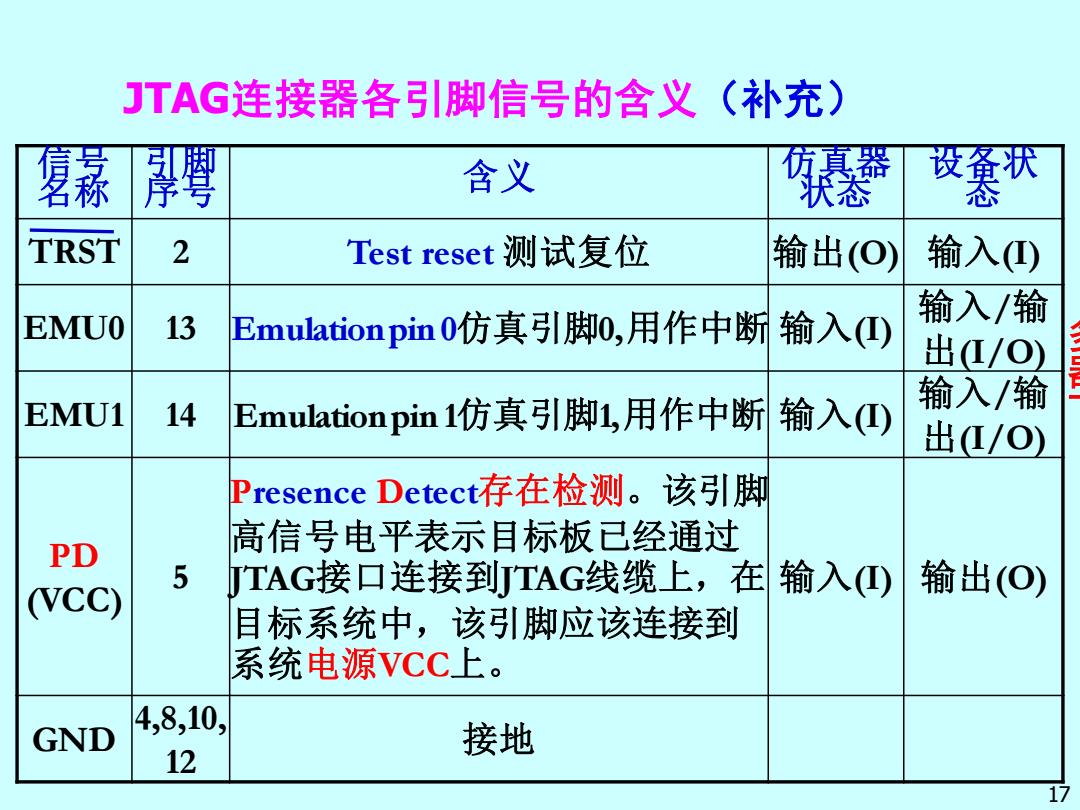

JTAG连接器各引脚信号的含义(补充) 蒜彎 含义 级琴器 设章状 态 TRST 2 Test reset测试复位 输出(O) 输入四) 输入/输 EMUO 13 Emulation pin0仿真引脚0,用作中断输入() 出/O) EMU1 14 Emulation pin1仿真引脚1,用作中断输入() 输入/输 出L/O) Presence Detect存在检测。该引脚 高信号电平表示目标板已经通过 PD 5 (vcc) TAG接口连接到TAG线缆上,在输入①) 输出(O) 目标系统中,该引脚应该连接到 系统电源VCC上。 GND 4,8,10, 12 接地 17

JTAG连接器各引脚信号的含义(补充) 信号名称 引脚序号 含义 仿真器 状态 设备状态 TRST 2 Test reset 测试复位 输出(O) 输入(I) EMU0 13 Emulation pin 0仿真引脚0, 用作中断 输入(I) 输入/输 出(I/O) EMU1 14 Emulation pin 1仿真引脚1, 用作中断 输入(I) 输入/输 出(I/O) PD (VCC) 5 Presence Detect存在检测。该引脚 高信号电平表示目标板已经通过 JTAG接口连接到JTAG线缆上,在 目标系统中,该引脚应该连接到 系统电源VCC上。 输入(I) 输出(O) GND 4,8,10, 12 接地 17 多处理 器情况 下可输 入