第七讲综合建模与仿真 西安邮电学院通信工程系 。时序逻辑电路按其工作方式可分为同步时序逻辑和异步时序逻辑。 冬同步时序电路中,全部时钟并联在一起,统一受系统时钟的控制, 各个触发器是同步动作的;异步时序电路中各级触发器的连接不是完 全相同的,状态变化也不是同步的。 。异步时序电路设计较为复杂,目前主要是人工设计;同步时序电路 设计主要有状态机和状态流程图方法。 X 组合逻辑 组合逻辑 y 存储元件 存储元件 Y : : y Y 存储元件 存储元件 时钟脉冲 同步时序逻辑电路 异步时序逻辑电路

第七讲 综合建模与仿真 西安邮电学院通信工程系 同步时序逻辑电路 异步时序逻辑电路 . . . 组合逻辑 存储元件 . X1 Xn Z1 Zm Y1 y1 yr 存储元件 Yr 时钟脉冲 . . . 组合逻辑 存储元件 . X1 Xn Z1 Zm Y1 y1 yr 存储元件 Yr . . ❖时序逻辑电路按其工作方式可分为同步时序逻辑和异步时序逻辑。 ❖ 同步时序电路中,全部时钟并联在一起,统一受系统时钟的控制, 各个触发器是同步动作的; 异步时序电路中各级触发器的连接不是完 全相同的,状态变化也不是同步的。 ❖异步时序电路设计较为复杂,目前主要是人工设计;同步时序电路 设计主要有状态机和状态流程图方法

第七讲综合建模与仿真 西安邮电学院通信工程系 1)基本的8位寄存器 输入字 输入 d CLK T玉 输出 输出字 (a) (b) (a)D触发器;(b)8位寄存器

第七讲 综合建模与仿真 西安邮电学院通信工程系 (a) D触发器; (b) 8位寄存器 输 入 CLK 输 出 Q7 d 7 Q6 d 6 Q5 d 5 Q4 d 4 Q3 d 3 Q2 d 2 Q1 d 1 Q0 d 0 输入字 输出字 (a) (b) CLK 1) 基本的8位寄存器

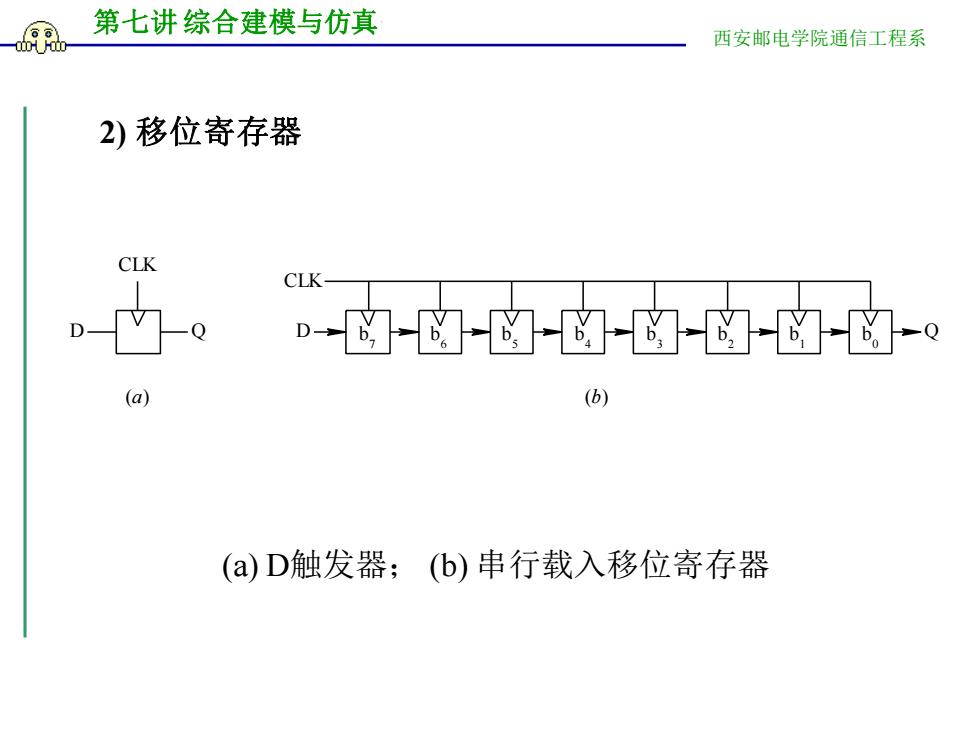

第七讲综合建模与仿真 西安邮电学院通信工程系 2)移位寄存器 CLK CLK -0 (a) (b) (a)D触发器;(b)串行载入移位寄存器

第七讲 综合建模与仿真 西安邮电学院通信工程系 (a) D触发器; (b) 串行载入移位寄存器 Q b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 CLK D CLK D Q (a) (b) 2) 移位寄存器

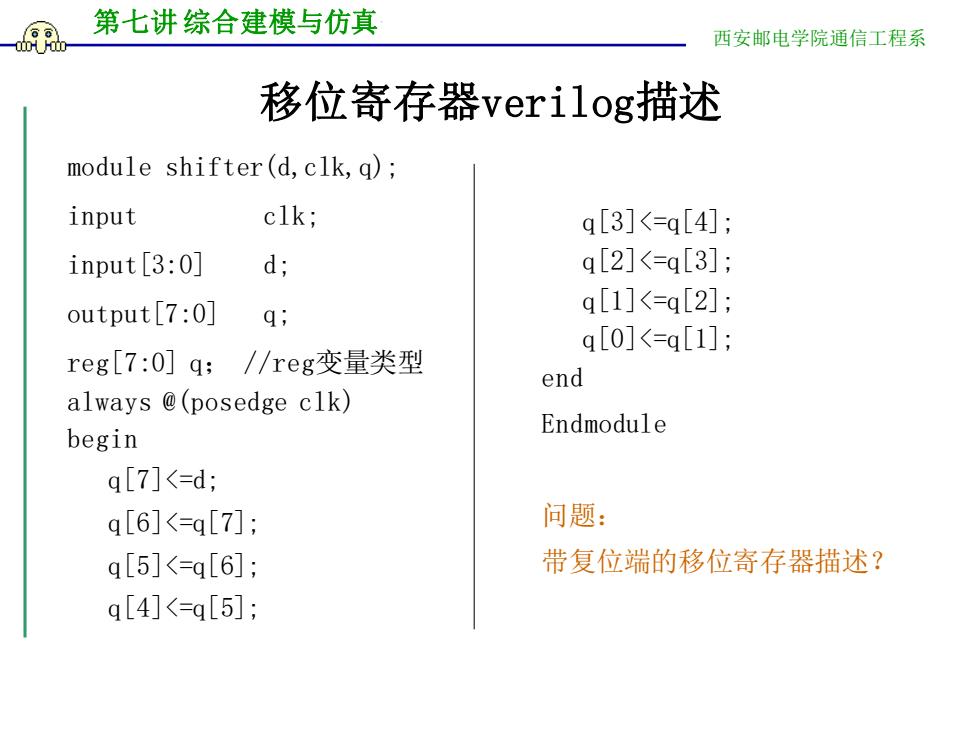

第七讲综合建模与仿真 西安邮电学院通信工程系 移位寄存器verilog描述 module shifter(d,clk,q); input clk; q[3]<=q[4]; input [3:0] d; q[2]<=q[3]; output[7:0] q; q[1]<=q[2]; q[0]<=q[1]; reg[7:0]q;/reg变量类型 end always @(posedge clk) Endmodule begin q[7]<=d; q[6]<=q[7]; 问题: q[5]<=q[6]: 带复位端的移位寄存器描述? q[4]<=q[5]:

第七讲 综合建模与仿真 西安邮电学院通信工程系 移位寄存器verilog描述 module shifter(d,clk,q); input clk; input[3:0] d; output[7:0] q; reg[7:0] q; //reg变量类型 always @(posedge clk) begin q[7]<=d; q[6]<=q[7]; q[5]<=q[6]; q[4]<=q[5]; q[3]<=q[4]; q[2]<=q[3]; q[1]<=q[2]; q[0]<=q[1]; end Endmodule 问题: 带复位端的移位寄存器描述?

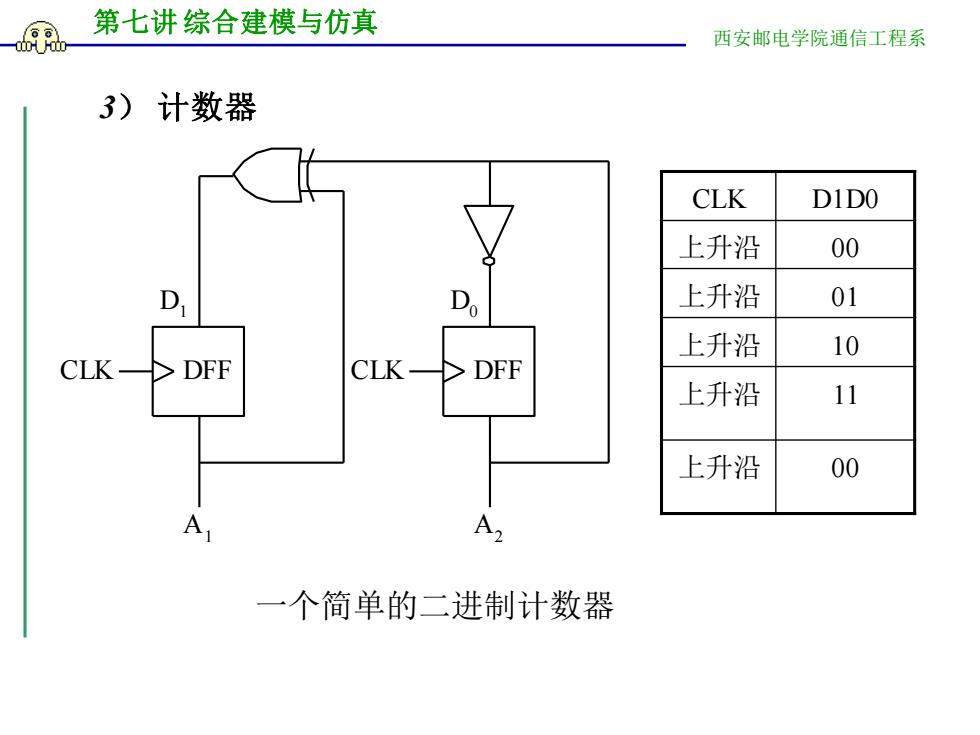

第七讲综合建模与仿真 西安邮电学院通信工程系 3)计数器 CLK DIDO 上升沿 00 D D 上升沿 01 上升沿 10 CLK- DFF CLK- DFF 上升沿 11 上升沿 00 A A2 一个简单的二进制计数器

第七讲 综合建模与仿真 西安邮电学院通信工程系 一个简单的二进制计数器 CLK D1 DFF CLK D0 DFF A1 A2 3) 计数器 CLK D1D0 上升沿 00 上升沿 01 上升沿 10 上升沿 11 上升沿 00