第七讲综合建模与仿真 西安邮电学院通信工程系 多路输出选择器的功能描述 module decode2 4(p,s,x); input [1:0]s;input x; output [3:0]p;reg[3:0]p; always@(sorx)∥电平敏感变量表 case(s) 本例中X是信号 2b00:p<={3b0,x}: /000x 2b01:p<={2b0,x,1b0};1/00x0 2b10:p<={1'b0,x,2'b0};/0x00 default:p={x,3'b0); /x000 endcase endmodule

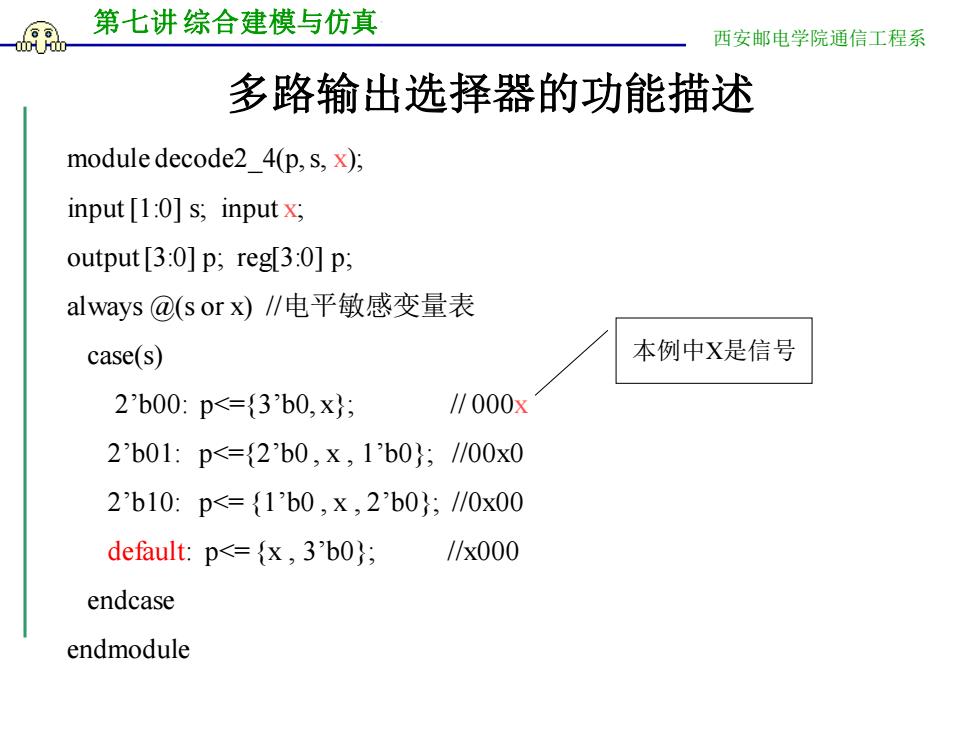

第七讲 综合建模与仿真 西安邮电学院通信工程系 多路输出选择器的功能描述 module decode2_4(p, s, x); input [1:0] s; input x; output [3:0] p; reg[3:0] p; always @(s or x) //电平敏感变量表 case(s) 2’b00: p<={3’b0, x}; // 000x 2’b01: p<={2’b0 , x , 1’b0}; //00x0 2’b10: p<= {1’b0 , x , 2’b0}; //0x00 default: p<= {x , 3’b0}; //x000 endcase endmodule 本例中X是信号

第七讲综合建模与仿真 西安邮电学院通信工程系 5)算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位,能完成两个 一位二进制数的加法运算。 输入数据 a b Sn Cntl 0 0 0 0 0 1 1 0 Cn+1 HA 进位输出 1 0 1 0 1 0 1 S,和 (a) (b)

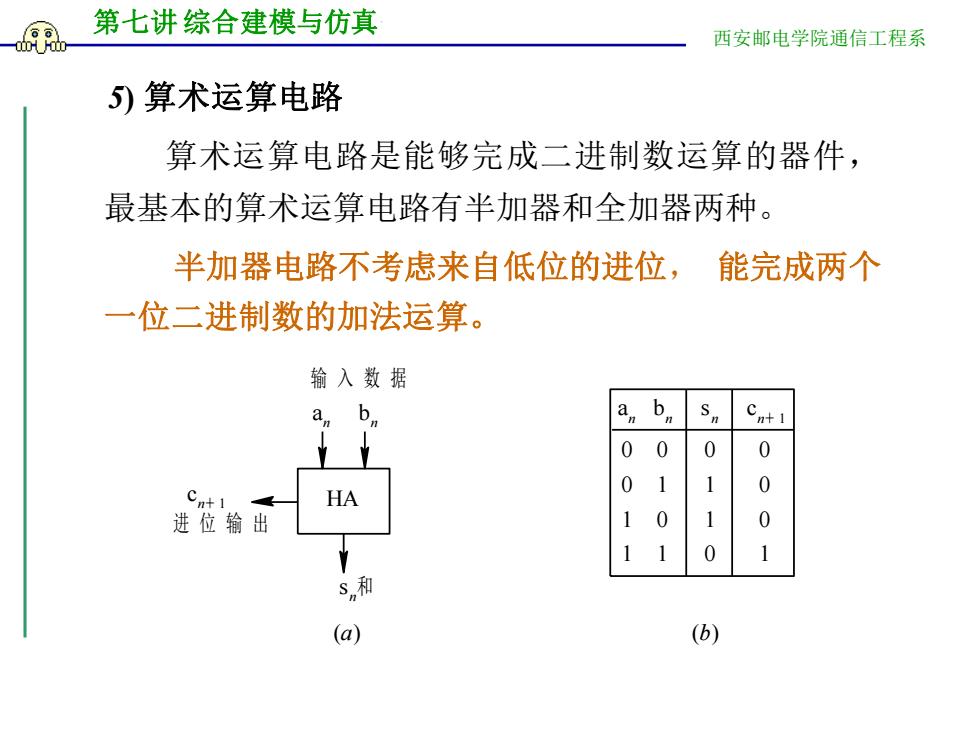

第七讲 综合建模与仿真 西安邮电学院通信工程系 5) 算术运算电路 算术运算电路是能够完成二进制数运算的器件, 最基本的算术运算电路有半加器和全加器两种。 半加器电路不考虑来自低位的进位, 能完成两个 一位二进制数的加法运算。 HA 输入数据 an bn s n 和 cn+ 1 进位输出 0 0 0 1 1 0 1 1 0 1 1 0 (a) (b) a n b n s n c n+ 1 0 0 0 1

第七讲综合建模与仿真 西安邮电学院通信工程系 全加器是一种考虑来自低位的进位的二进制加法 运算电路,它可以实现多位二进制数的加法运算。 输入数据 an bn Cn+l a, 0 0 0 0 0 0 1 0 Cn+l FA Cn 1 0 0 0 0 进位输出 进位输入 1 1 0 0 1 0 0 1 0 n和 0 1 1 1 1 1 0 1 1 1 111 1 (a) (b)

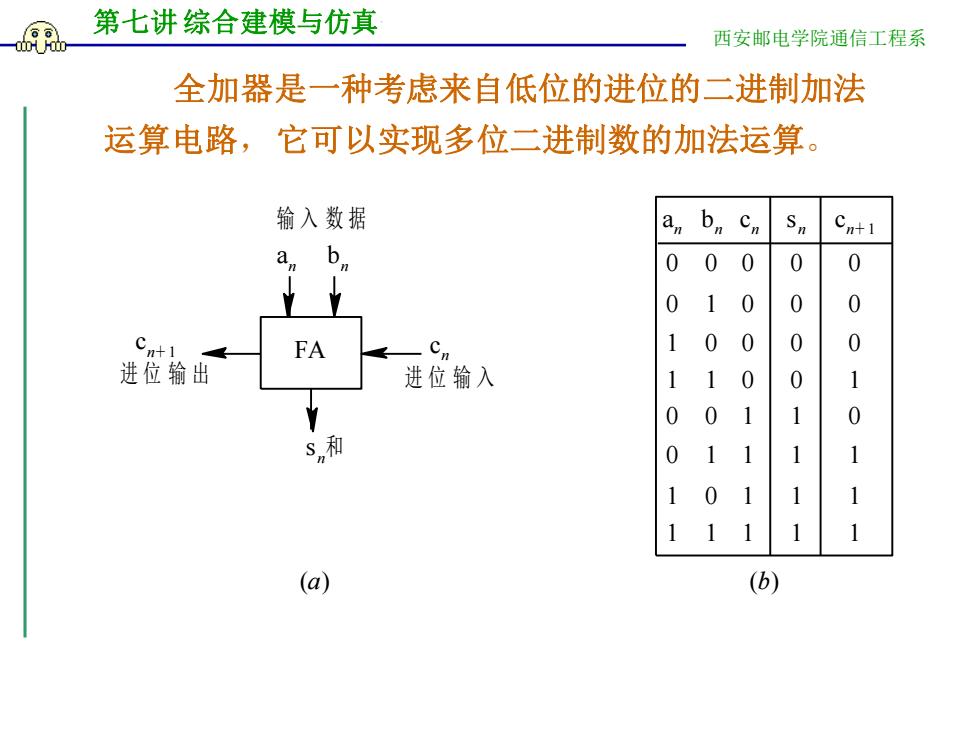

第七讲 综合建模与仿真 西安邮电学院通信工程系 全加器是一种考虑来自低位的进位的二进制加法 运算电路,它可以实现多位二进制数的加法运算。 FA 输 入 数 据 an bn s n 和 cn+1 进 位 输 出 0 0 0 1 1 0 1 1 0 0 0 0 (a) (b) an bn s n cn+1 0 0 0 1 cn 进 位 输 入 0 0 0 1 1 0 1 1 1 1 1 1 0 1 1 1 0 0 0 0 cn 1 1 1 1

第七讲综合建模与仿真 西安邮电学院通信工程系 全加器的功能描述 module adder4(cout,sum,ina,inb,cin); output [3:0]sum; output cout; input [3:0]ina,i 组合运 input cin; 算符 assign {cout,sum}=ina+inb+cin; endmodule 组合逻辑的verilog描述方法 小结: 用assign赋值语句。 用电平敏感的alwaysi语句

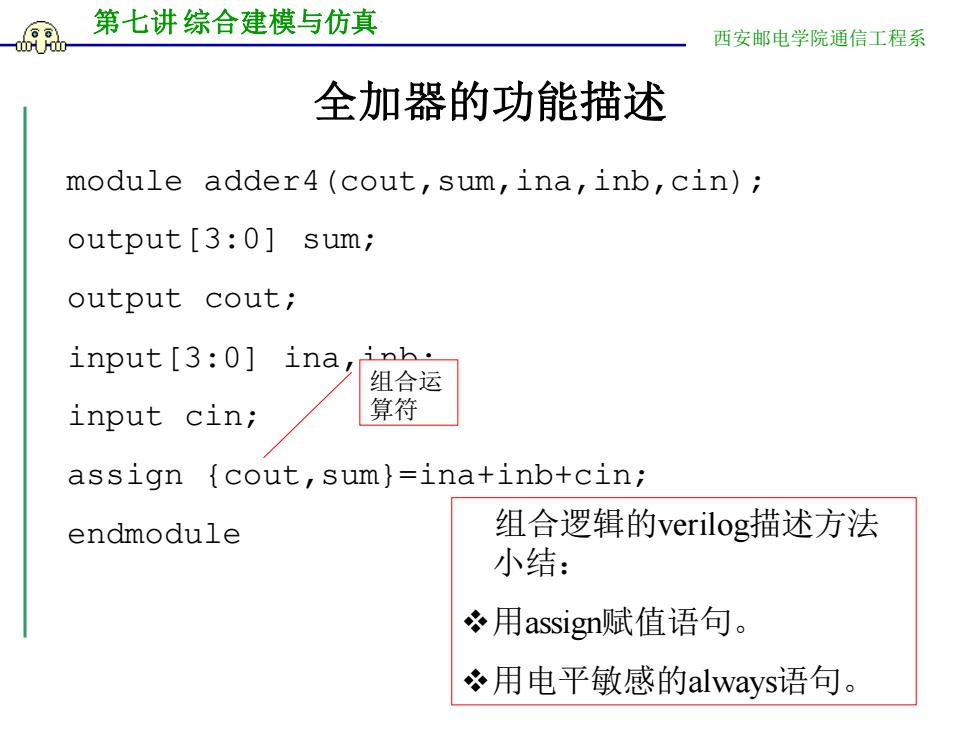

第七讲 综合建模与仿真 西安邮电学院通信工程系 全加器的功能描述 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 组合运 算符 组合逻辑的verilog描述方法 小结: ❖用assign赋值语句。 ❖用电平敏感的always语句

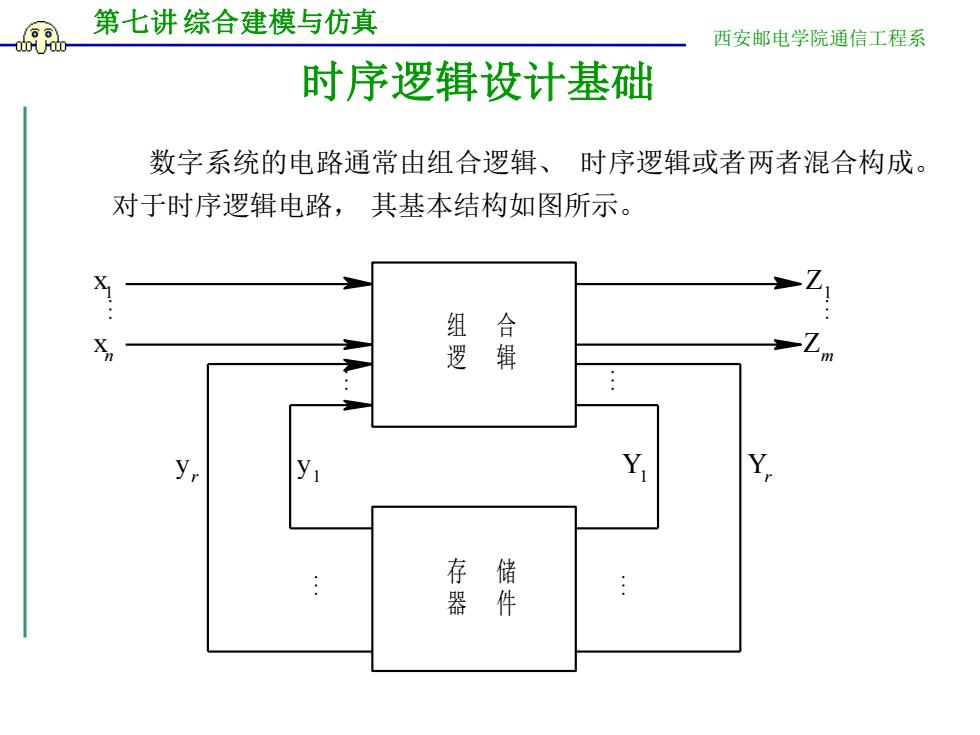

6 第七讲综合建模与仿真 西安邮电学院通信工程系 时序逻辑设计基础 数字系统的电路通常由组合逻辑、时序逻辑或者两者混合构成。 对于时序逻辑电路,其基本结构如图所示。 组逻 合辑 yr y Y 存器 储件

第七讲 综合建模与仿真 西安邮电学院通信工程系 数字系统的电路通常由组合逻辑、 时序逻辑或者两者混合构成。 对于时序逻辑电路, 其基本结构如图所示。 时序逻辑设计基础 . . . 组 合 逻 辑 存 储 器 件 . x1 xn Z1 Zm Y1 y1 yr Yr .