第三讲门级与结构建模 西安邮电学院通信工程系 第三讲门级与结构建模 内容: 冬结构建模分类 Verilog内建基本门 冬门级结构建模 冬门延迟 冬用户模块结构建模 冬模块仿真入门

第三讲 门级与结构建模 西安邮电学院通信工程系 第 三讲 门级与结构建模 内容: ❖ 结构建模分类 ❖ Verilog内建基本门 ❖ 门级结构建模 ❖ 门延迟 ❖ 用户模块结构建模 ❖ 模块仿真入门

第三讲门级与结构建模 西安邮电学院通信工程系 结构建模分类 编译指令 模块定义 时序特性 Compiler directives module (port list) timig specifications 端口说明 数据类型说明 电路功能描述 子程序 Port declarations Data type declarations Circuit functionality subprograms 模块实例 输入 线网类型 instantiation 任务 input net task 连续赋值 过程块 输出 寄存器类型 函数 Continuous Procedural function output register assignment blocks 双向 参数 赋值语句 过程块语句 系统任务和函数 inout parameter assign initial block System task always block function

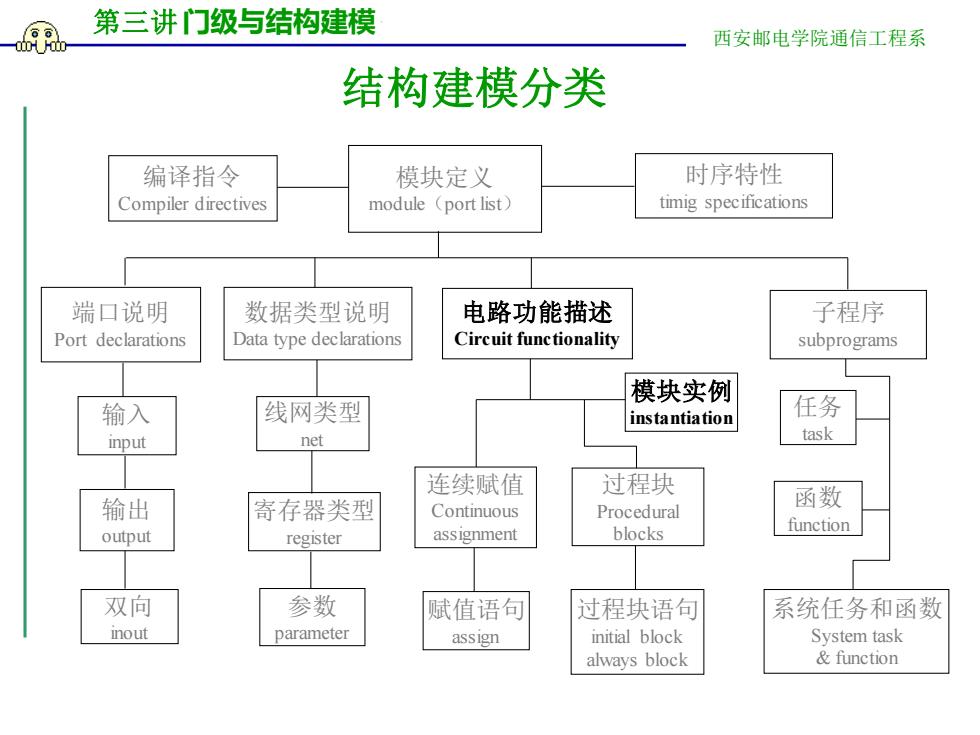

第三讲 门级与结构建模 西安邮电学院通信工程系 结构建模分类 模块定义 module(port list) 时序特性 timig specifications 端口说明 Port declarations 输入 input 双向 inout 输出 output 数据类型说明 Data type declarations 线网类型 net 参数 parameter 寄存器类型 register 电路功能描述 Circuit functionality 子程序 subprograms 任务 task 函数 function 系统任务和函数 System task & function 编译指令 Compiler directives 连续赋值 Continuous assignment 赋值语句 assign 过程块 Procedural blocks 过程块语句 initial block always block 模块实例 instantiation

第三讲门级与结构建模 西安邮电学院通信工程系 结构建模分类 。结构建模侧重反映模块内部的结构组成。 必 门级建模 由基本逻辑门级元件互连而成的具有一定功能的电路模块。 冬开关级建模(不讲) 是构成VerilogHDL对硬件设计最低层次的描述。通常的综合工具不 支持开关级描述。 冬用户定义原语建模(不讲) 由用户定义基础元件互连而成的具有一定功能的电路模块。 用户定义模块建模 由用户定义模块互连而成的具有一定功能的电路模块

第三讲 门级与结构建模 西安邮电学院通信工程系 结构建模分类 ❖ 结构建模侧重反映模块内部的结构组成。 ❖ 门级建模 由基本逻辑门级元件互连而成的具有一定功能的电路模块。 ❖ 开关级建模(不讲) 是构成VerilogHDL对硬件设计最低层次的描述。通常的综合工具不 支持开关级描述。 ❖ 用户定义原语建模(不讲) 由用户定义基础元件互连而成的具有一定功能的电路模块。 ❖ 用户定义模块建模 由用户定义模块互连而成的具有一定功能的电路模块

第三讲门级与结构建模 西安邮电学院通信工程系 Verilog内建基本门 多输入门:and,nand,or,nor,xor, xnor 多输出门:buf,not 三态门:bufif0,bufif1,notif0,notif1 冬上拉、下拉电阻:pullup,pulldown MOS开关:cmos,nmos, pmos,rcmos,rnmos,rpmos 双向开关:tran,tranifO,tranifl,rtran, rtranifO,rtranifl

第三讲 门级与结构建模 西安邮电学院通信工程系 Verilog内建基本门 ❖ 多输入门:and, nand, or, nor, xor, xnor ❖ 多输出门:buf, not ❖ 三态门:bufif0, bufif1, notif0,notif1 ❖ 上拉、下拉电阻:pullup, pulldown ❖ MOS开关:cmos, nmos, pmos, rcmos, rnmos, rpmos ❖ 双向开关:tran,tranif0, tranif1, rtran, rtranif0, rtranif1

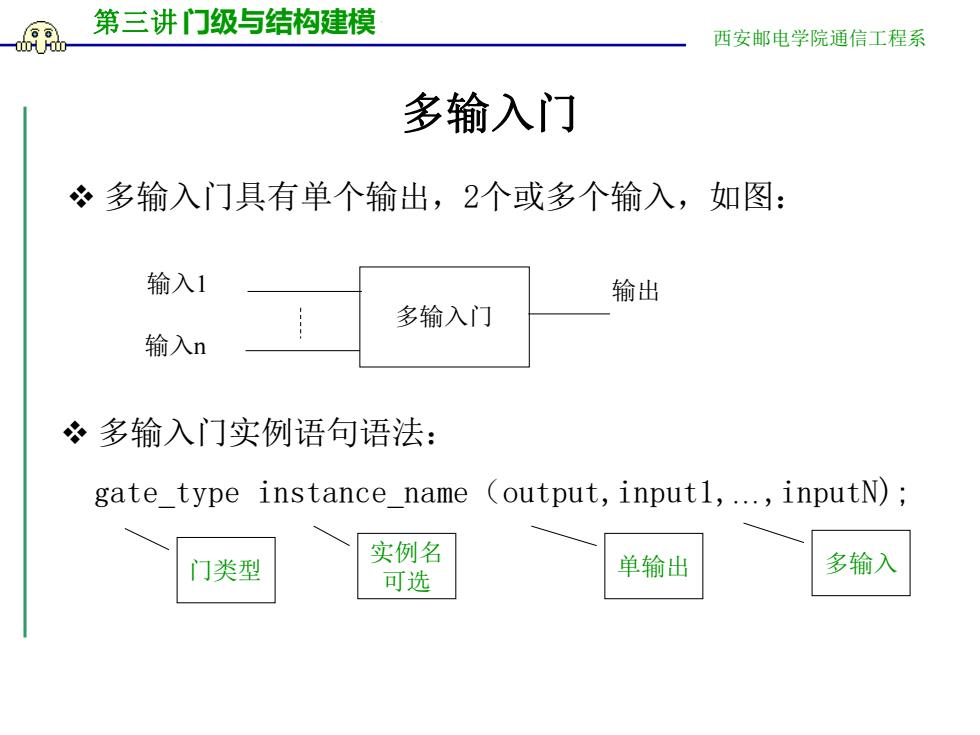

第三讲门级与结构建模 西安邮电学院通信工程系 多输入门 多输入门具有单个输出,2个或多个输入,如图: 输入1 输出 多输入门 输入n 冬多输入门实例语句语法: gate_type instance name (output,input1,.,inputN); 门类型 实例名 多输入 可选 单输出

第三讲 门级与结构建模 西安邮电学院通信工程系 多输入门 ❖ 多输入门具有单个输出,2个或多个输入,如图: ❖ 多输入门实例语句语法: gate_type instance_name(output,input1,.,inputN); 多输入门 输出 输入n 输入1 门类型 实例名 可选 单输出 多输入