2.2复杂可编程逻辑器件(CPLD) CPLD太都采用各种分区阵列绩构,每个区域内部相肖于 二个小规模的PLD,各区域之间通过可编程全局笪莲总线连 接,构成较天规模的CPLD器件。 小规模PLD 互连资源 (a) (b) (c) 图22CPLD的几种全局结构示意图

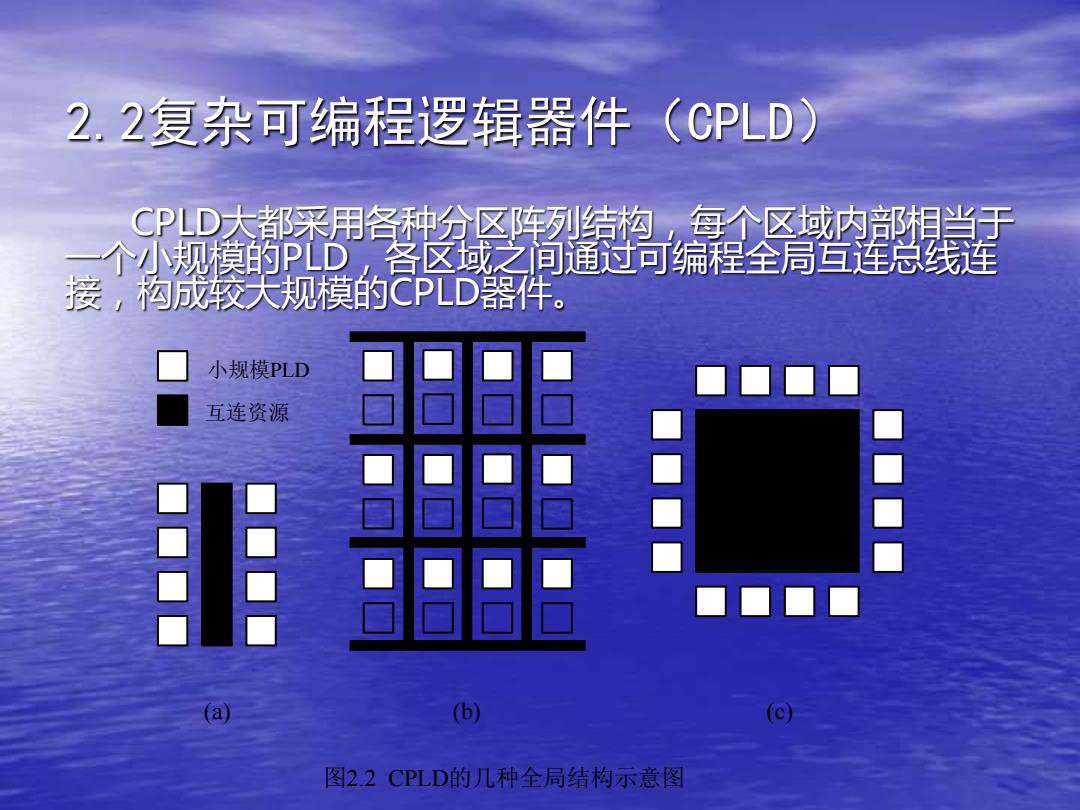

2.2复杂可编程逻辑器件(CPLD) CPLD大都采用各种分区阵列结构,每个区域内部相当于 一个小规模的PLD,各区域之间通过可编程全局互连总线连 接,构成较大规模的CPLD器件。 小规模PLD 互连资源 (a) (b) (c) 图2.2 CPLD的几种全局结构示意图

1,MAX7000系列器件的基本结构 MAX7000系列器件主要由2~16个逻辑阵列块LAB(Logic Array Bock)、2~16个I/O控制模块和一个可编程互连阵列 PIA(Programmable Interconnect Array)三部分构成。 全局时钟 全局活零 销出使能】 输出使能2 LABA 路8: 10控制模块 8如16 宏单元 36 30 宏单元 8to16 1到16 17到32 908 16 6 控制模块 8 to 18 816 中 LABC LABD 16控制模块 8o16 ■ 宏单元 38 宏单元 33道48 49到64 16 10控制模块 8 ● 图2.3MAX7000系列器件结构示意图

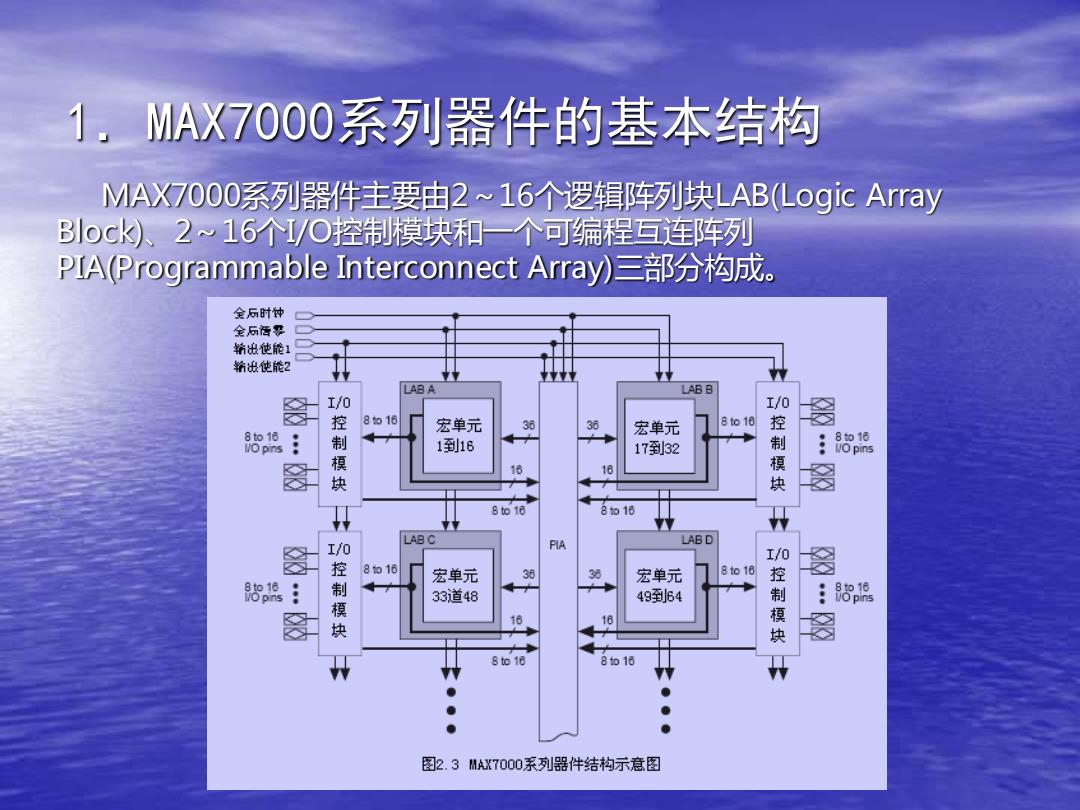

1.MAX7000系列器件的基本结构 MAX7000系列器件主要由2~16个逻辑阵列块LAB(Logic Array Block)、2~16个I/O控制模块和一个可编程互连阵列 PIA(Programmable Interconnect Array)三部分构成

2,MAX7000系列器件的逻辑宏单元结构 MAX7000系列器件中的逻辑宏单元是器件实现逻辑功能的主体,它 主要由逻辑阵列、乘积项选择矩阵和可编程寄存器三个功能块组成,每 一个宏单元可以被单独地配置为时序逻辑或组合逻辑工作方式。 金5金局 逻每阵列 香琴时钟 来自 来自其他 2 I/0 宠单元的 快速输可缤程 引迎 并行扩展 入选怪音存器 岛存器 旁路 到I/0 控制 乘积 模块 项选 时钟 怪纯 选择 复的 选择 共卒巡细 到PIA 扩展项 来自PIA的 16个扩展痕积项 6个倍号 图2.4 MAX7O00系列器件逻辑宏单元结构

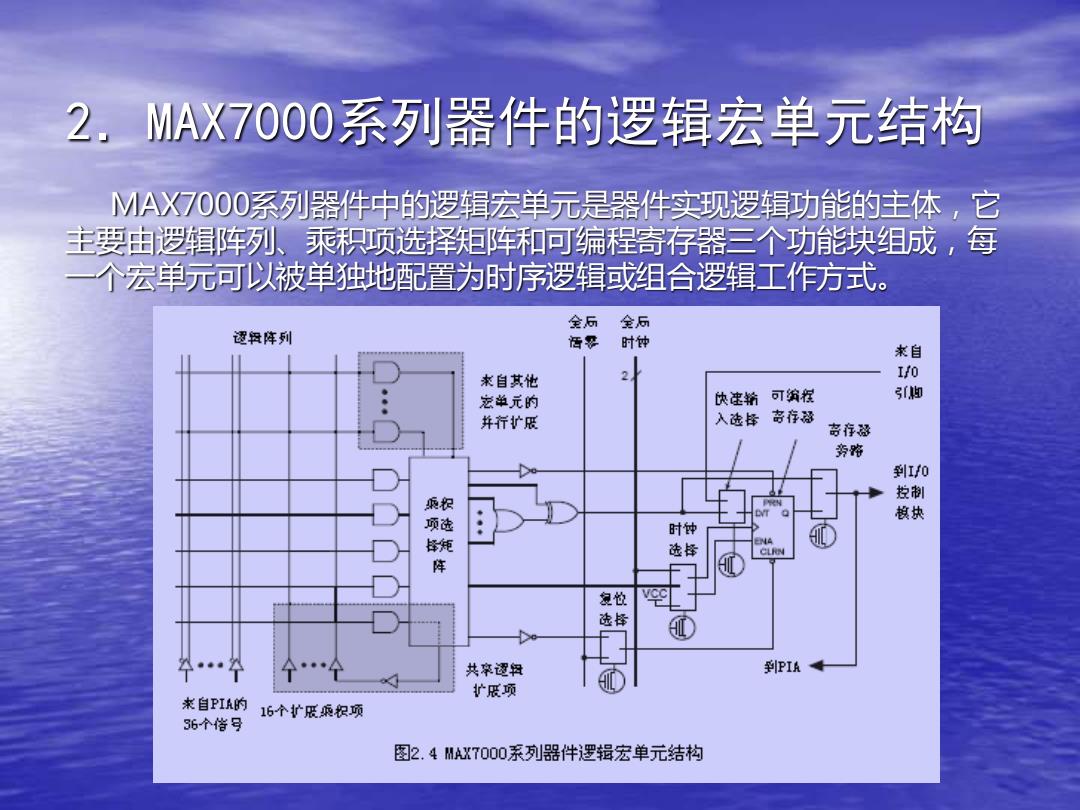

2.MAX7000系列器件的逻辑宏单元结构 MAX7000系列器件中的逻辑宏单元是器件实现逻辑功能的主体,它 主要由逻辑阵列、乘积项选择矩阵和可编程寄存器三个功能块组成,每 一个宏单元可以被单独地配置为时序逻辑或组合逻辑工作方式

2,MAX7000系列器件逻辑宏单元结构(续1) ·逻辑阵列功能模块 每个LAB有16个共享扩展项,每一个共享乘积项可以被LAB内任何一 个或全部宏单元使用和共享,以便实现复杂的逻辑函数。 密单元 乘积项 乘积项选怪矩阵 宠单元 乘枳项 来自PIA的 16个扩展乘积项 36个格号

2.MAX7000系列器件逻辑宏单元结构(续1) • 逻辑阵列功能模块 每个LAB有16个共享扩展项,每一个共享乘积项可以被LAB内任何一 个或全部宏单元使用和共享,以便实现复杂的逻辑函数

2,MAX7000系列器件逻辑宏单元结构(续2) ·逻辑阵列功能模块 除共享乘积项外可使用并联扩展乘积项实现复杂逻辑函数。此时,最 多允许20个乘积项直接传送到逻辑宏单元的"“或”逻辑中,其中5个乘 积项是由宏单元本身提供的,15个并联扩展项是从同一个LAB中相邻宏 单元借用的。 自前一个老单元 Prese 花单元 乘积项 乘积 Preset Clear 到后一个蔻单元 来自PIA的 16个扩展 36个偕号

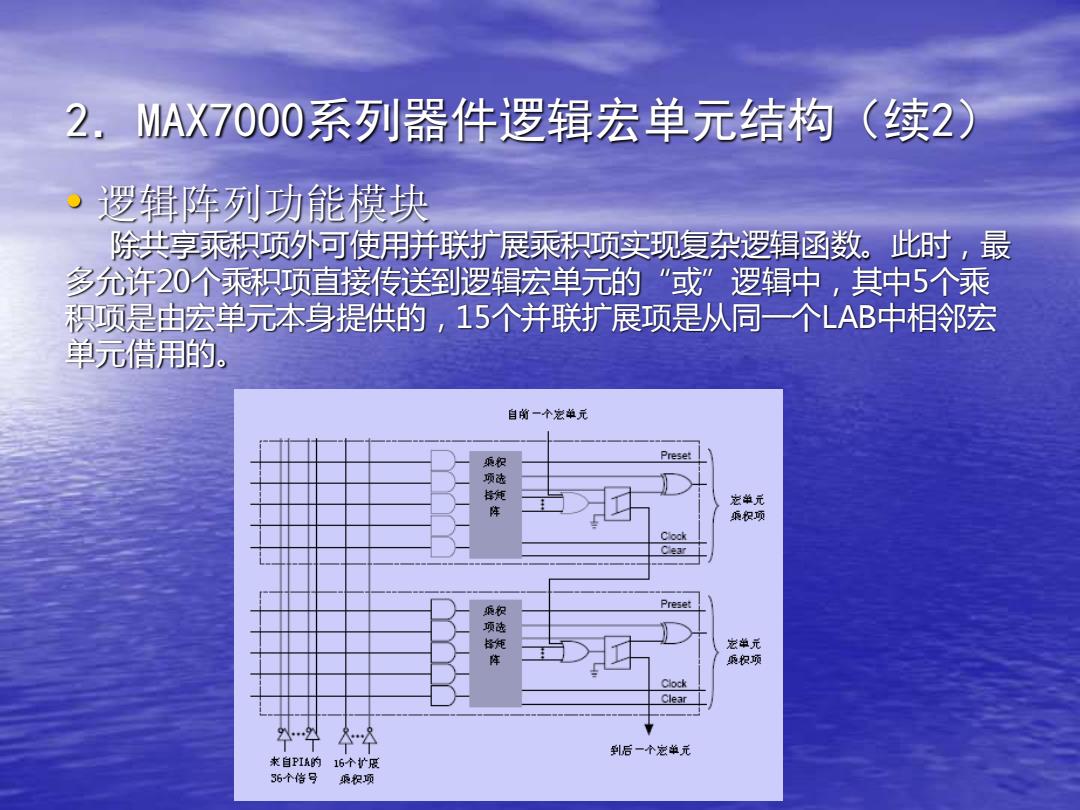

2.MAX7000系列器件逻辑宏单元结构(续2) • 逻辑阵列功能模块 除共享乘积项外可使用并联扩展乘积项实现复杂逻辑函数。此时,最 多允许20个乘积项直接传送到逻辑宏单元的“或”逻辑中,其中5个乘 积项是由宏单元本身提供的,15个并联扩展项是从同一个LAB中相邻宏 单元借用的