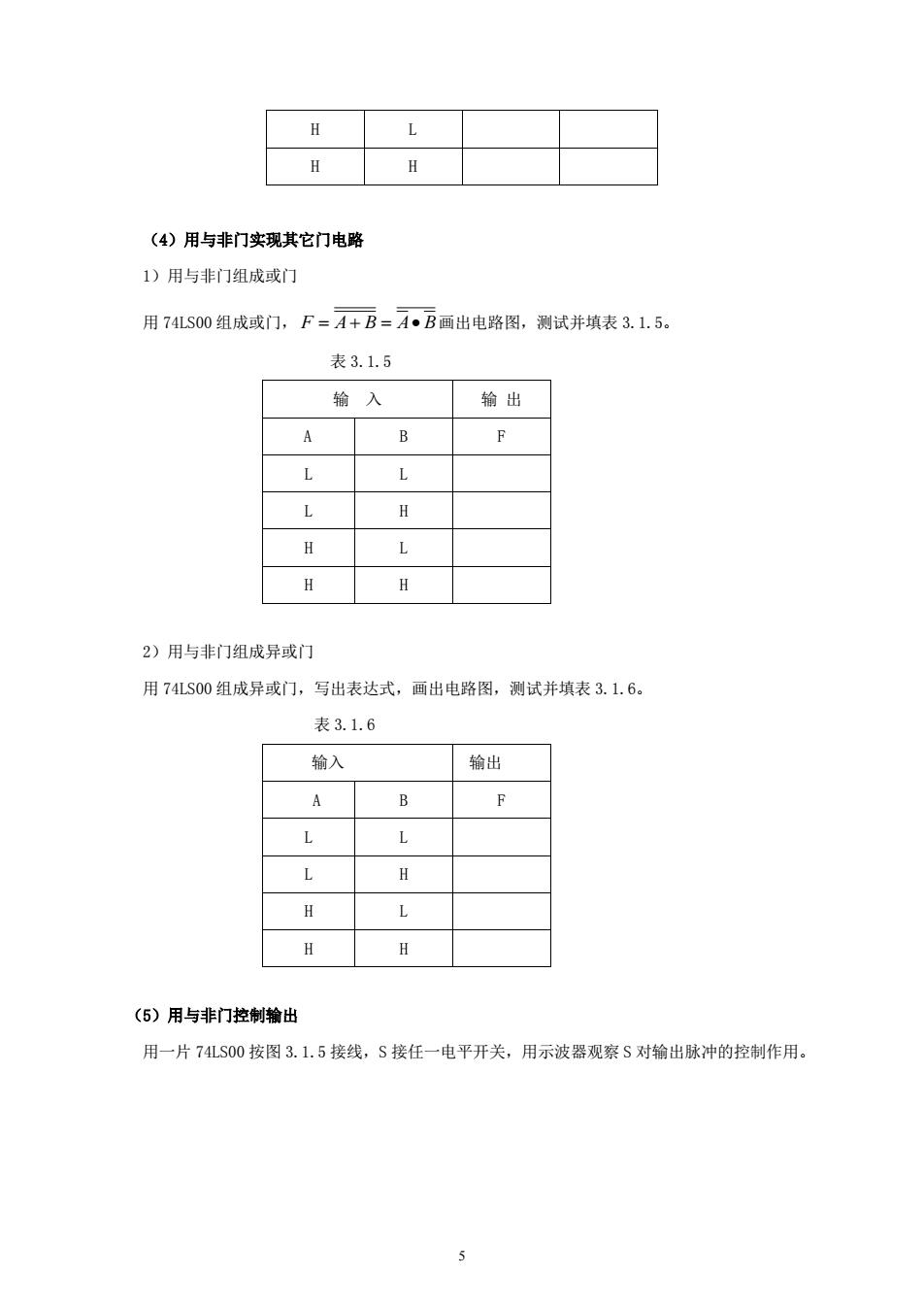

H L H H (4)用与非门实现其它门电略 1)用与非门组成或门 用74LS00组成或门,F=A+B=A●B画出电路图,测试并填表3.1.5。 表3.1.5 输入 输出 A B F L L L H H L H H 2)用与非门组成异或门 用74LS00组成异或门,写出表达式,画出电路图,测试并填表3.1.6。 表3.1.6 输入 输出 A B F L L L H H L H H (5)用与非门控制输出 用一片74LS00按图3.1.5接线,S接任一电平开关,用示波器观察S对输出脉冲的控制作用。 5

5 H L H H (4)用与非门实现其它门电路 1)用与非门组成或门 用 74LS00 组成或门, F A B A B 画出电路图,测试并填表 3.1.5。 表 3.1.5 2)用与非门组成异或门 用 74LS00 组成异或门,写出表达式,画出电路图,测试并填表 3.1.6。 表 3.1.6 (5)用与非门控制输出 用一片 74LS00 按图 3.1.5 接线,S 接任一电平开关,用示波器观察 S 对输出脉冲的控制作用。 输 入 输 出 A B F L L L H H L H H 输入 输出 A B F L L L H H L H H

图3.1.5用与非门控制输出 5.实验报告 (1)按各步骤填写表格: (2)回答问题: 怎样判断门电路逻功能是否正常? 实验二组合逻辑电路 1.实验目的 (1)学习及掌握组合逻辑电路的设计、调试方法: (2)掌握半加器和全加器的逻辑功能: (3)学会二进制数的运算规律。 2.实验设备与器件 (1)数字万用表: (2)数字实验台: (3)器件:74LS00 二输入端四与非门 3片 74LS86 二输入端四异或门 1片 74LS54 四组输入与或非门 1片 3.预习要求 (1)预习组合逻辑电路的分析方法: (2)推导由与非门和异或门构成半加器、全加器的逻辑表达式: (3)预习二进制数的运算规律。 4.实验内容及实验步骤 (1)组合逻辑电路的功能测试 6

6 图 3.1.5 用与非门控制输出 5.实验报告 (1)按各步骤填写表格; (2)回答问题: 怎样判断门电路逻辑功能是否正常? 实验二 组合逻辑电路 1.实验目的 (1)学习及掌握组合逻辑电路的设计、调试方法; (2)掌握半加器和全加器的逻辑功能; (3)学会二进制数的运算规律。 2.实验设备与器件 (1)数字万用表; (2)数字实验台; (3)器件: 74LS00 二输入端四与非门 3 片 74LS86 二输入端四异或门 1 片 74LS54 四组输入与或非门 1 片 3.预习要求 (1)预习组合逻辑电路的分析方法; (2)推导由与非门和异或门构成半加器、全加器的逻辑表达式; (3)预习二进制数的运算规律。 4.实验内容及实验步骤 (1)组合逻辑电路的功能测试

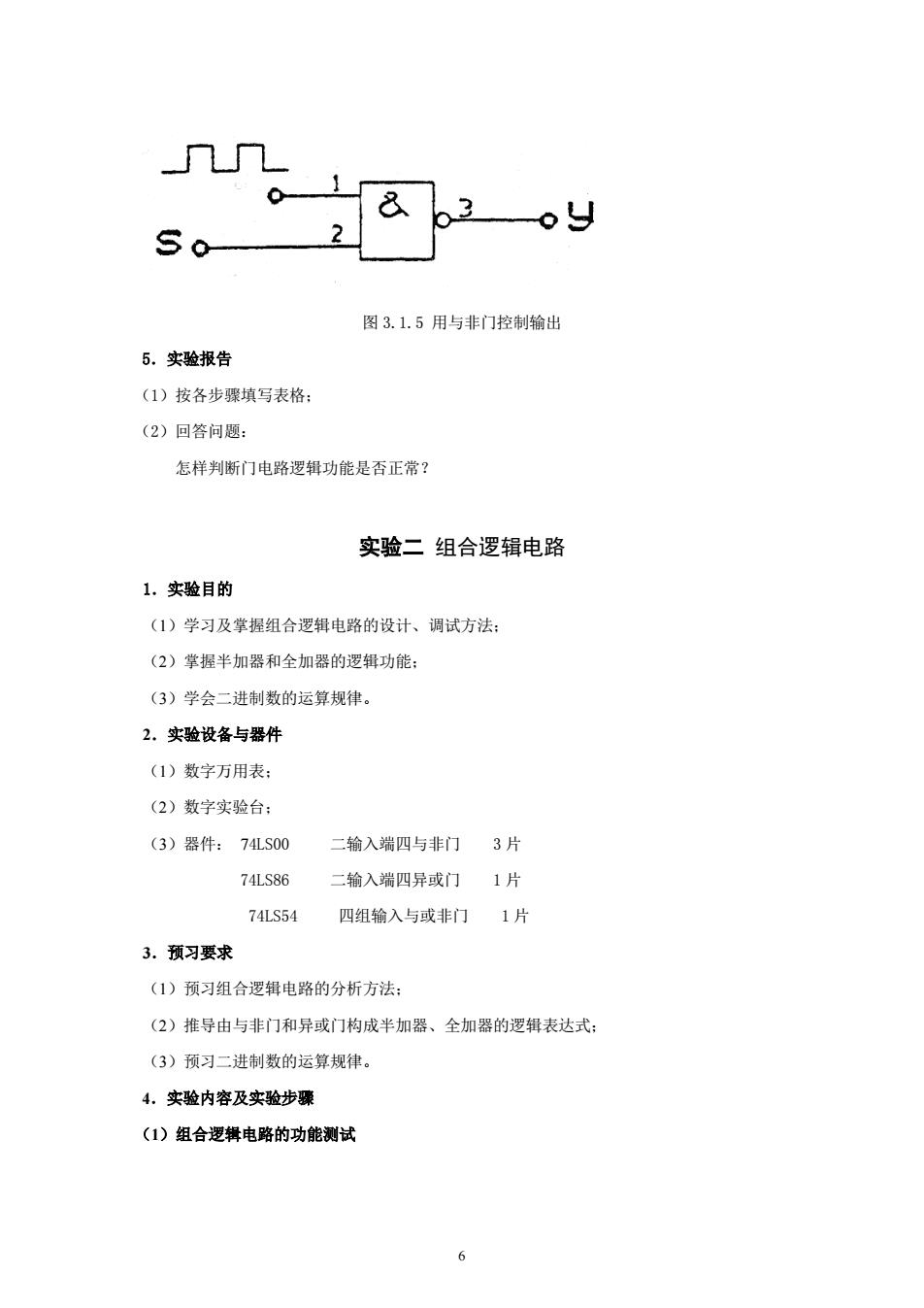

A 12 a 13 G3 B G6 18 G4 & G2 0 2 G? 12 & 11 13 2 GS 图3.1.6用2片74LS00组成的逻辑电路 1)用2片74LS00组成如图3.1.6所示的逻辑电路,为便于接线和检查,在图中注明了芯片的型 号及各引脚对应的编号。 2)图中A、B、C接电平开关,X、接发光二极管。 3)按表3.1.7的要求填表,并写出X、2的逻辑表达式。 4)将运算结果和实验结果比较。 表3.1.7 输入 输出 ABC Y Y2 000 001 010 011 100 101 110 111 (2)测试用异或门74LS86和与非门74LS00组成的半加器的逻辑功能

7 图 3.1.6 用 2 片 74LS00 组成的逻辑电路 1)用 2 片 74LS00 组成如图 3.1.6 所示的逻辑电路,为便于接线和检查,在图中注明了芯片的型 号及各引脚对应的编号。 2)图中 A、B、C 接电平开关,Y1、Y2接发光二极管。 3)按表 3.1.7 的要求填表,并写出 Y1、Y2的逻辑表达式。 4)将运算结果和实验结果比较。 表 3.1.7 输入 输出 A B C Y1 Y2 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 (2)测试用异或门 74LS86 和与非门 74LS00 组成的半加器的逻辑功能

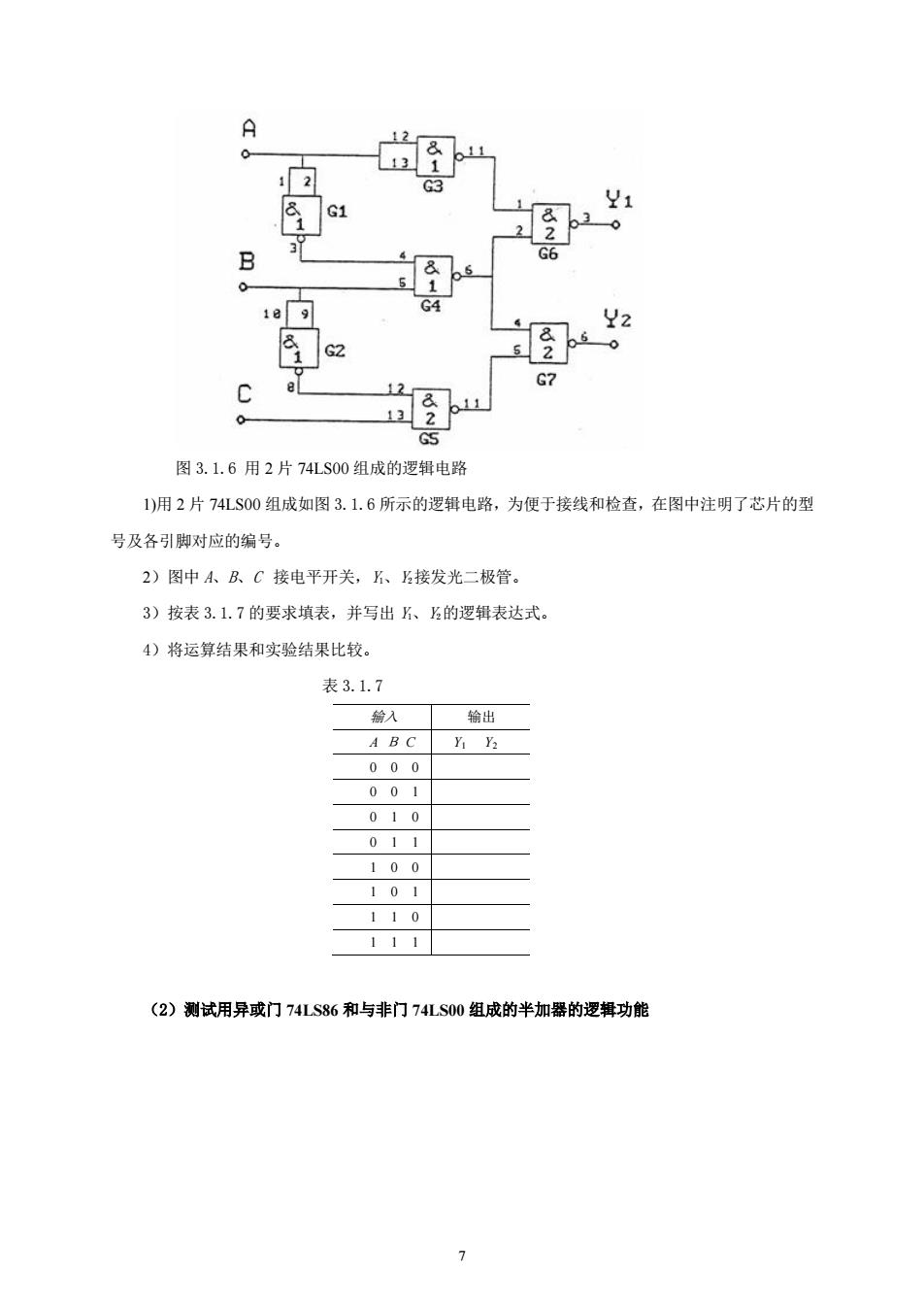

9 B 图3.1.7用一个集成异或门和两个与非门组成的半加器 由半加器的逻辑函数式可知,可以用一个异或门和一个与门组成半加器,因此用一个集成异或 门和两个与非门组成的半加器如图3.1.7所示 1)在数字实验台上连接电路。图中A、B接电平开关,XZ接电平显示。 2)按表3.1.8要求填表。 表3.1.8 输入 输出 AB YZ 00 01 10 11 (3)测试用异或门、与或非门和非门组成的全加器的逻辑功能 全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或 非门和一个与非门实现。 1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出表达式。 2)连接电路,接线时注意与或非门中不用的与门输入端接地。 3)当输入端A、、G为表3.1.9的情况时,用万用表测量S和C的电位并将其转为相应的 逻辑状态填如表。 表3.1.9 输入 输出 A B G S G 000 001 010 011 100 P

8 图 3.1.7 用一个集成异或门和两个与非门组成的半加器 由半加器的逻辑函数式可知,可以用一个异或门和一个与门组成半加器,因此用一个集成异或 门和两个与非门组成的半加器如图 3.1.7 所示 1)在数字实验台上连接电路。图中 A、B 接电平开关,Y、Z 接电平显示。 2)按表 3.1.8 要求填表。 表 3.1.8 输入 输出 A B Y Z 0 0 0 1 1 0 1 1 (3)测试用异或门、与或非门和非门组成的全加器的逻辑功能 全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或 非门和一个与非门实现。 1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出表达式。 2)连接电路,接线时注意与或非门中不用的与门输入端接地。 3)当输入端 Ai、Bi、Ci-1为表 3.1.9 的情况时,用万用表测量 Si和 Ci的电位并将其转为相应的 逻辑状态填如表。 表 3.1.9 输入 输出 Ai Bi Ci-1 Si Ci 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0

101 110 111 5.实验报告 (1)按各步骤填写表格: (2)总结逻辑电路的分析方法? 实验三译码器和数据选择器 1.实验目的 (1)掌握中规模集成译码器74LS139的逻辑功能和使用方法: (2)掌握中规模集成数据选择器74LS153的逻辑功能和使用方法。 2.实验设备与器件 (1)数字示波器: (2)数字万用表: (3)数字实验台: (4)器件:74LS139 双2-4线译码器 1片 74LS153 双4选1数据选择器 1片 74LS00 二输入端四与非门 1片 3.预习要求 (1)复习译码器的工作原理及集成译码器的使用方法 (2)熟悉数据选择器的工作原理及集成数据选择器的使用方法: (3)复习集成译码器和集成数据选择器设计组合逻辑电路的方法。 4.实验内容及实验步骤 (1)译码器功能测试 将74LS139译码器按图3.1.8接线,按表3.1.10输入电平分别置数,填输出状态。 9

9 1 0 1 1 1 0 1 1 1 5.实验报告 (1)按各步骤填写表格; (2)总结逻辑电路的分析方法? 实验三 译码器和数据选择器 1.实验目的 (1)掌握中规模集成译码器 74LSl39 的逻辑功能和使用方法; (2)掌握中规模集成数据选择器 74LSl53 的逻辑功能和使用方法。 2.实验设备与器件 (1)数字示波器; (2)数字万用表; (3)数字实验台; (4)器件:74LSl39 双 2-4 线译码器 1 片 74LSl53 双 4 选 1 数据选择器 1 片 74LS00 二输入端四与非门 l 片 3.预习要求 (1)复习译码器的工作原理及集成译码器的使用方法; (2)熟悉数据选择器的工作原理及集成数据选择器的使用方法; (3)复习集成译码器和集成数据选择器设计组合逻辑电路的方法。 4.实验内容及实验步骤 (1)译码器功能测试 将 74LSl39 译码器按图 3.1.8 接线,按表 3.1.10 输入电平分别置数,填输出状态