。UART0相关寄存器描述一中断使能寄存器 TxDO UOIIR UOIER UOTHR UOTSR UODLM UODLL UOLCR UOLSR RxDO UOIER 描述 复位值 0 RBR中断使能。1:使能RDA中断;O:禁止RDA中断。 0 1 THRE中断使能。1:使能THRE中断;O:禁止THRE中断。 0 Rx线状态中断使能。1:禁止Rx线状态中断;O:禁止Rx线状态中断; 2 0 该中断状态可从U0LSR[4:1]读出。 7:3 保留,用户软件不要向这些位写入1。 未定义 U0IER可以控制UART0的4个中断源。其中RBR中断使能包括两个中断, 一个是接收数据可用(RDA)中断,一个是接收超时中断(CTI)。稍后将 对各中断源作详细介绍

U0THR U0TSR TxD0 RxD0 U0LCR U0LSR U0IIR U0IER U0DLM U0DLL • UART0相关寄存器描述 U0IER 描述 复位值 0 RBR中断使能。1:使能RDA中断;0:禁止RDA中断。 0 1 THRE中断使能。1:使能THRE中断;0:禁止THRE中断。 0 2 Rx线状态中断使能。1:禁止Rx线状态中断;0:禁止Rx线状态中断; 该中断状态可从U0LSR[4:1]读出。 0 7 : 3 保留,用户软件不要向这些位写入1。 未定义 ——中断使能寄存器 U0IER U0IER可以控制UART0的4个中断源。其中RBR中断使能包括两个中断, 一个是接收数据可用(RDA)中断,一个是接收超时中断(CTI)。稍后将 对各中断源作详细介绍

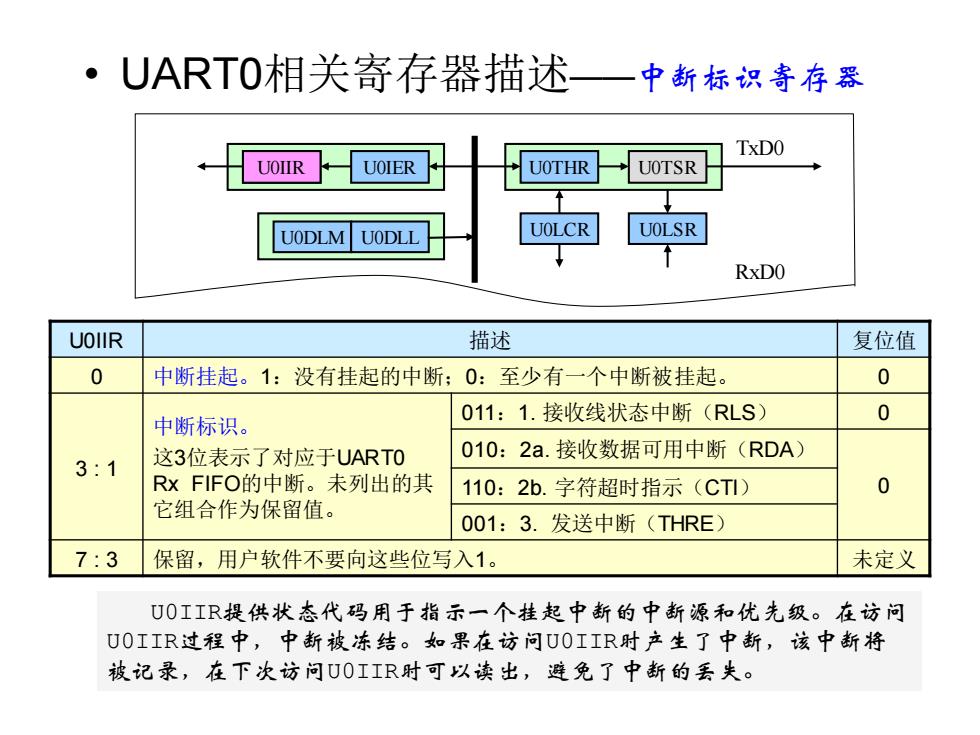

·UART0相关寄存器描述一中断标识寄存器 TxDO UOIIR UOIER UOTHR UOTSR UODLM UODLL UOLCR UOLSR RxDO UOIIR 描述 复位值 0 中断挂起。1:没有挂起的中断:0:至少有一个中断被挂起。 0 011:1.接收线状态中断(RLS) 0 中断标识。 这3位表示了对应于UARTO 010:2a.接收数据可用中断(RDA) 3:1 Rx FIFO的中断。未列出的其 110:2b.字符超时指示(CT1) 0 它组合作为保留值。 001:3.发送中断(THRE) 7:3 保留,用户软件不要向这些位写入1。 未定义 U0IIR提供状态代码用于指示一个挂起中断的中断源和优先级。在访问 U0IIR过程中,中断被冻结。如果在访问U0IIR时产生了中断,该中断将 被记录,在下次访问U0IIR时可以读出,避免了中断的丢失

U0THR U0TSR TxD0 RxD0 U0LCR U0LSR U0IIR U0IER U0DLM U0DLL • UART0相关寄存器描述 U0IIR 描述 复位值 0 中断挂起。1:没有挂起的中断;0:至少有一个中断被挂起。 0 3 : 1 中断标识。 这3位表示了对应于UART0 Rx FIFO的中断。未列出的其 它组合作为保留值。 011:1. 接收线状态中断(RLS) 0 010:2a. 接收数据可用中断(RDA) 110:2b. 字符超时指示(CTI) 0 001:3. 发送中断(THRE) 7 : 3 保留,用户软件不要向这些位写入1。 未定义 ——中断标识寄存器 U0IIR提供状态代码用于指示一个挂起中断的中断源和优先级。在访问 U0IIR过程中,中断被冻结。如果在访问U0IIR时产生了中断,该中断将 被记录,在下次访问U0IIR时可以读出,避免了中断的丢失。 U0IIR

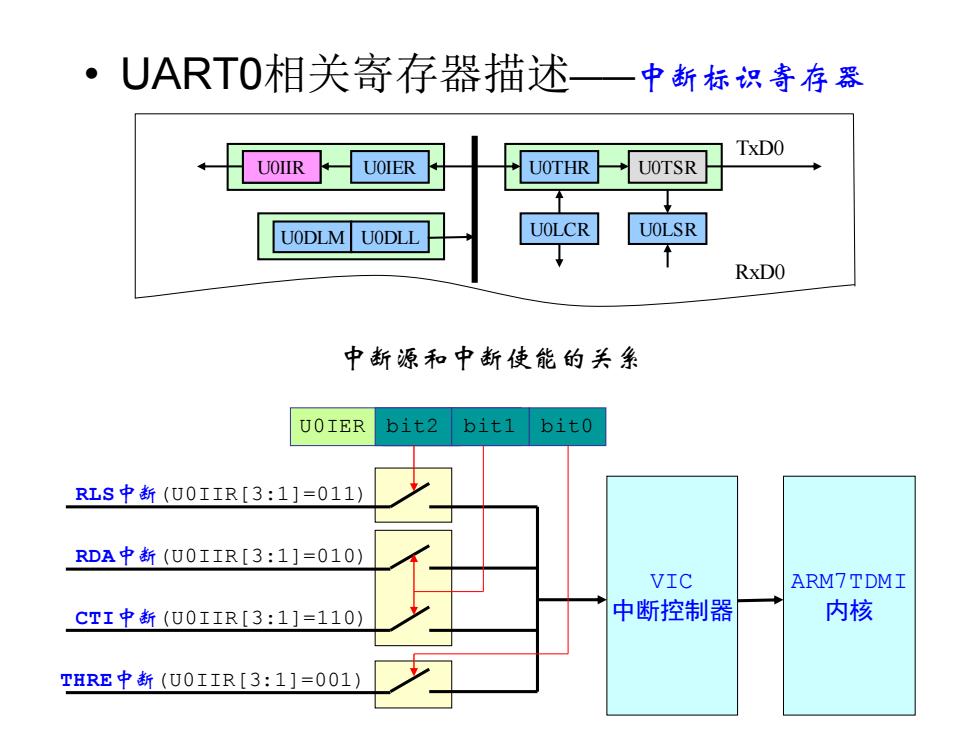

·UARTO相关寄存器描述一中断标识寄存器 TxDO UOIIR UOIER UOTHR UOTSR UODLM UODLL CR UOLSR RxDO 中断源和中断使能的关系 UOIER bit2 bitl bit0 RLS中新(U0IIR[3:1]=011) RDA中断(U0IIR[3:1]=010) VIC ARM7TDMI CTI中新(U0IIR[3:1]=110) 中断控制器 内核 THRE中断(U0IIR[3:1]=001)

U0THR U0TSR TxD0 RxD0 U0LCR U0LSR U0IIR U0IER U0DLM U0DLL • UART0相关寄存器描述——中断标识寄存器 中断源和中断使能的关系 U0IIR RLS中断(U0IIR[3:1]=011) RDA中断(U0IIR[3:1]=010) CTI中断(U0IIR[3:1]=110) THRE中断(U0IIR[3:1]=001) VIC 中断控制器 ARM7TDMI 内核 U0IER bit2 bit1 bit0

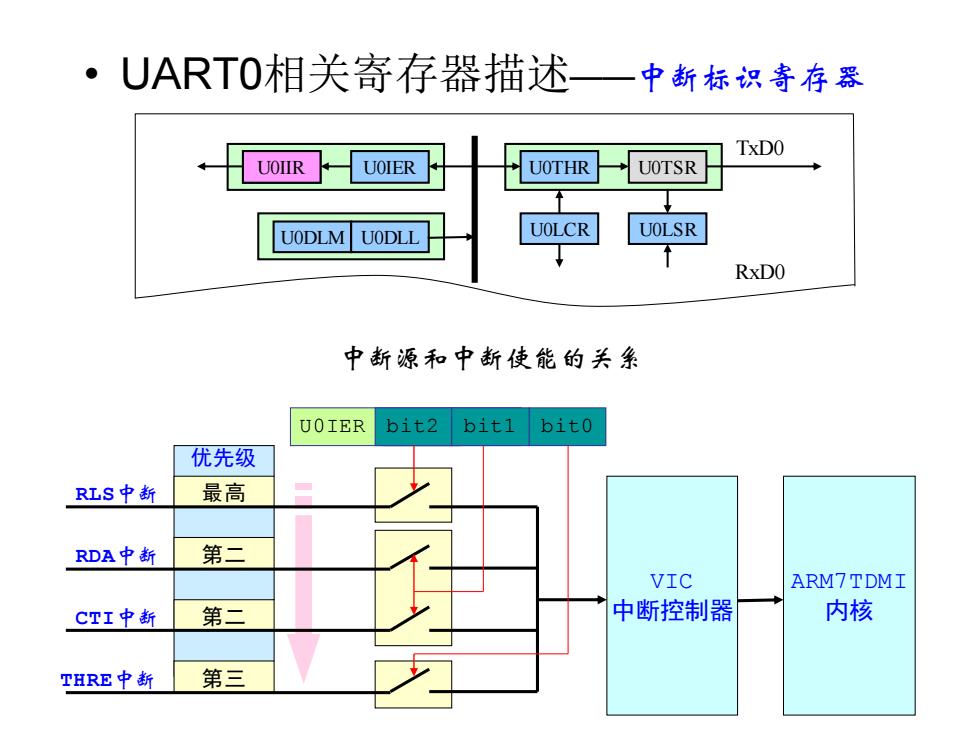

·UARTO相关寄存器描述一中断标识寄存器 TxDO UOIIR UOIER UOTHR UOTSR UODLM UODLL UOL CR UOLSR RxDO 中断源和中断使能的关系 UOIER bit2 bitl bit0 优先级 RLS中断 最高 RDA中新 第二 VIC ARM7TDMI CTI中断 第二 中断控制器 内核 THRE中新 第三

优先级 最高 第二 第二 第三 U0THR U0TSR TxD0 RxD0 U0LCR U0LSR U0IIR U0IER U0DLM U0DLL • UART0相关寄存器描述——中断标识寄存器 U0IIR RLS中断 RDA中断 CTI中断 THRE中断 VIC 中断控制器 ARM7TDMI 内核 U0IER bit2 bit1 bit0 中断源和中断使能的关系

·UART0相关寄存器描述一中断源说明 ●RLS中断:该中断为最高优先级。它在UART0产生了四个错误 条件(谥出错误(OE)、奇偶错误(PE)、帧错误(FE)和间隔中断 (BI))中的任意一个时置位。通过查看U0LSR[4:1]可以了解 到产生该中断的错误条件。读取U0LSR时请除该中断;

• UART0相关寄存器描述——中断源说明 ⚫ RLS中断:该中断为最高优先级。它在UART0产生了四个错误 条件(溢出错误(OE)、奇偶错误(PE)、帧错误(FE)和间隔中断 (BI))中的任意一个时置位。通过查看U0LSR[4:1]可以了解 到产生该中断的错误条件。读取U0LSR时清除该中断;