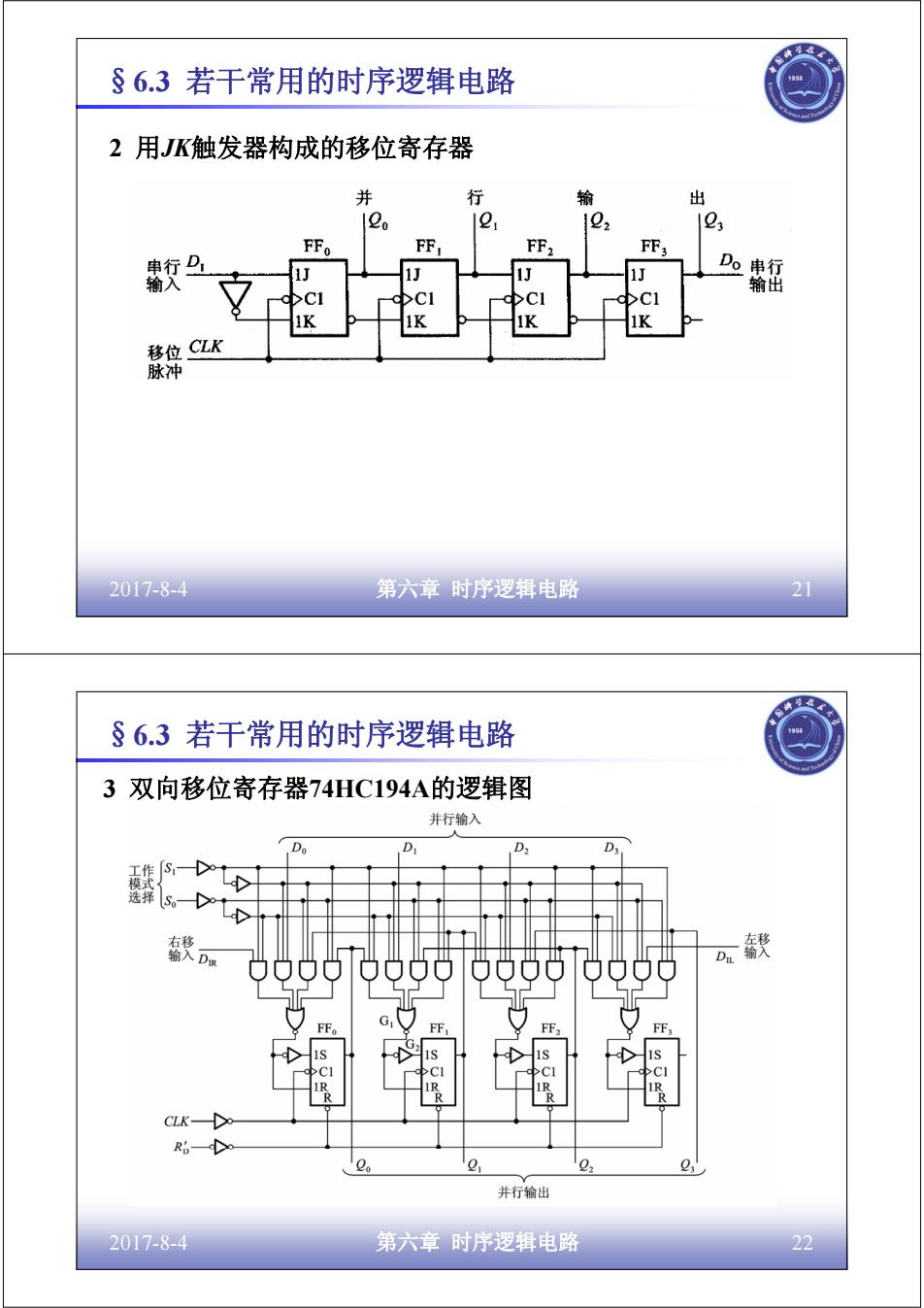

§6.3若干常用的时序逻辑电路 2用JK触发器构成的移位寄存器 并 行 输 12o 2 122 2 FFo FF FF2 FF; 行D Do 输入 行 输出 >ci >CI >C1 1K 1K 1K 1K 移位CLK 脉冲 2017-8-4 第六章时序逻辑电路 21 §6.3若干常用的时序逻辑电路 3双向移位寄存器74HC194A的逻辑图 并行输入 Do D D D 工作 模式 选择 右 输入DR 0000000666660000 Du. 款 FFo FF FF: FF CLK- 2 并行输出 2017-8-4 第六章时序逻辑电路 22

2017-8-4 第六章 时序逻辑电路 21 2 用JK触发器构成的移位寄存器 §6.3 若干常用的时序逻辑电路 2017-8-4 第六章 时序逻辑电路 22 3 双向移位寄存器74HC194A的逻辑图 §6.3 若干常用的时序逻辑电路

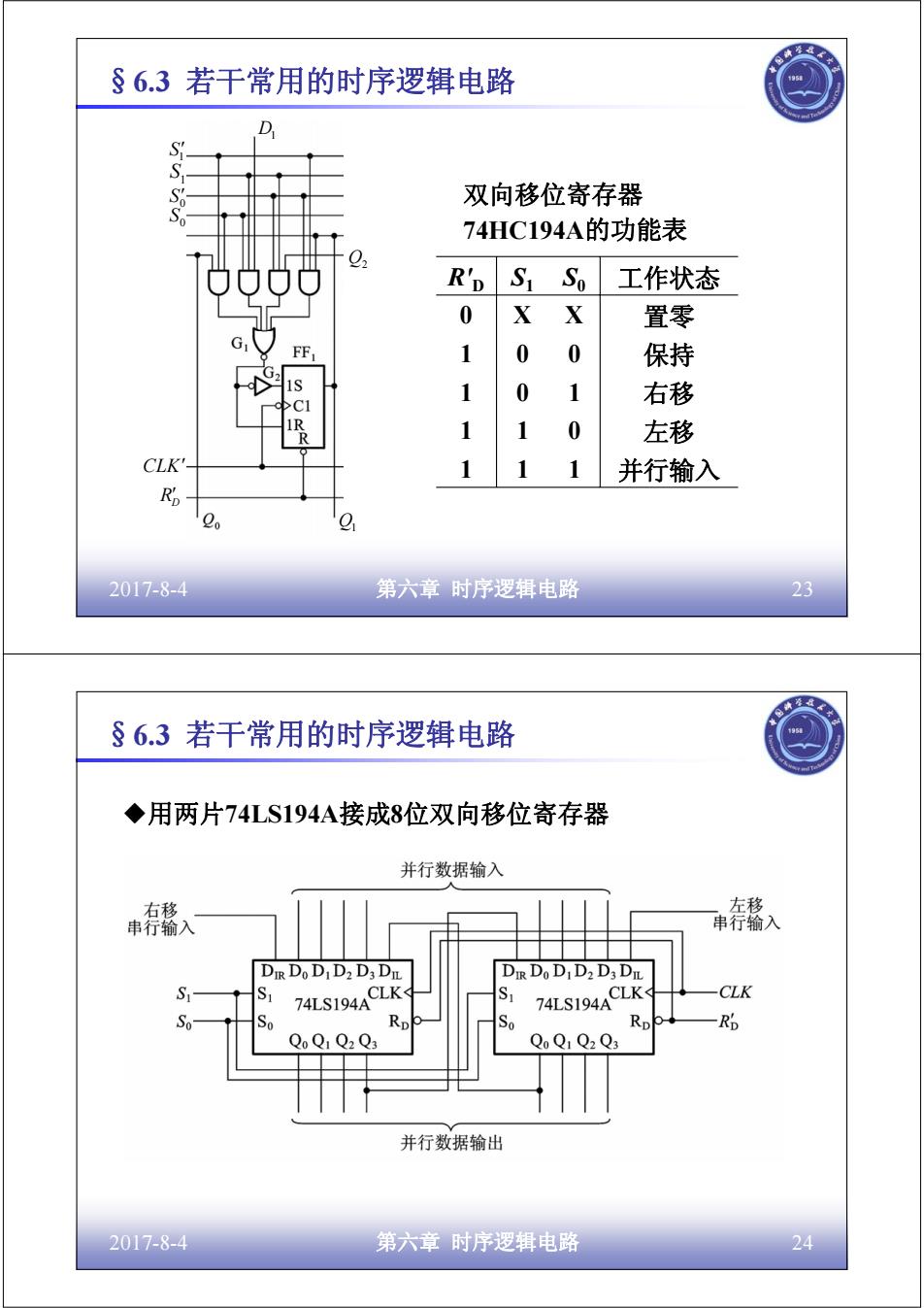

§6.3若干常用的时序逻辑电路 D 双向移位寄存器 74HC194A的功能表 R'p S1 So 工作状态 0 X X 置零 G 1 0 0 保持 1S 1 0 1 右移 R 1 1 0 左移 CLK' 1 1 并行输入 R 2o 2017-8-4 第六章时序逻辑电路 23 §6.3若干常用的时序逻辑电路 ◆用两片74LS194A接成8位双向移位寄存器 并行数据输入 右移 左移 串行输入 串行输入 DIR Do DI D2 D3 DIL DIR Do DI D2 D3 DIL S S 74LS194ACLK CLK 74LS194A CLK So Rp So Rp Rp Qo Q1 Q2 Q3 Qo Q:Q2Q3 并行数据输出 2017-8-4 第六章时序逻辑电路 24

2017-8-4 第六章 时序逻辑电路 23 1 1 1 并行输入 1 1 0 左移 1 0 1 右移 1 0 0 保持 0 X X 置零 R'D S1 S0 工作状态 S1 S0 S1 ′ 0 S′ D1 Q1 CLK′ RD ′ Q2 双向移位寄存器 74HC194A的功能表 §6.3 若干常用的时序逻辑电路 2017-8-4 第六章 时序逻辑电路 24 用两片74LS194A接成8位双向移位寄存器 §6.3 若干常用的时序逻辑电路

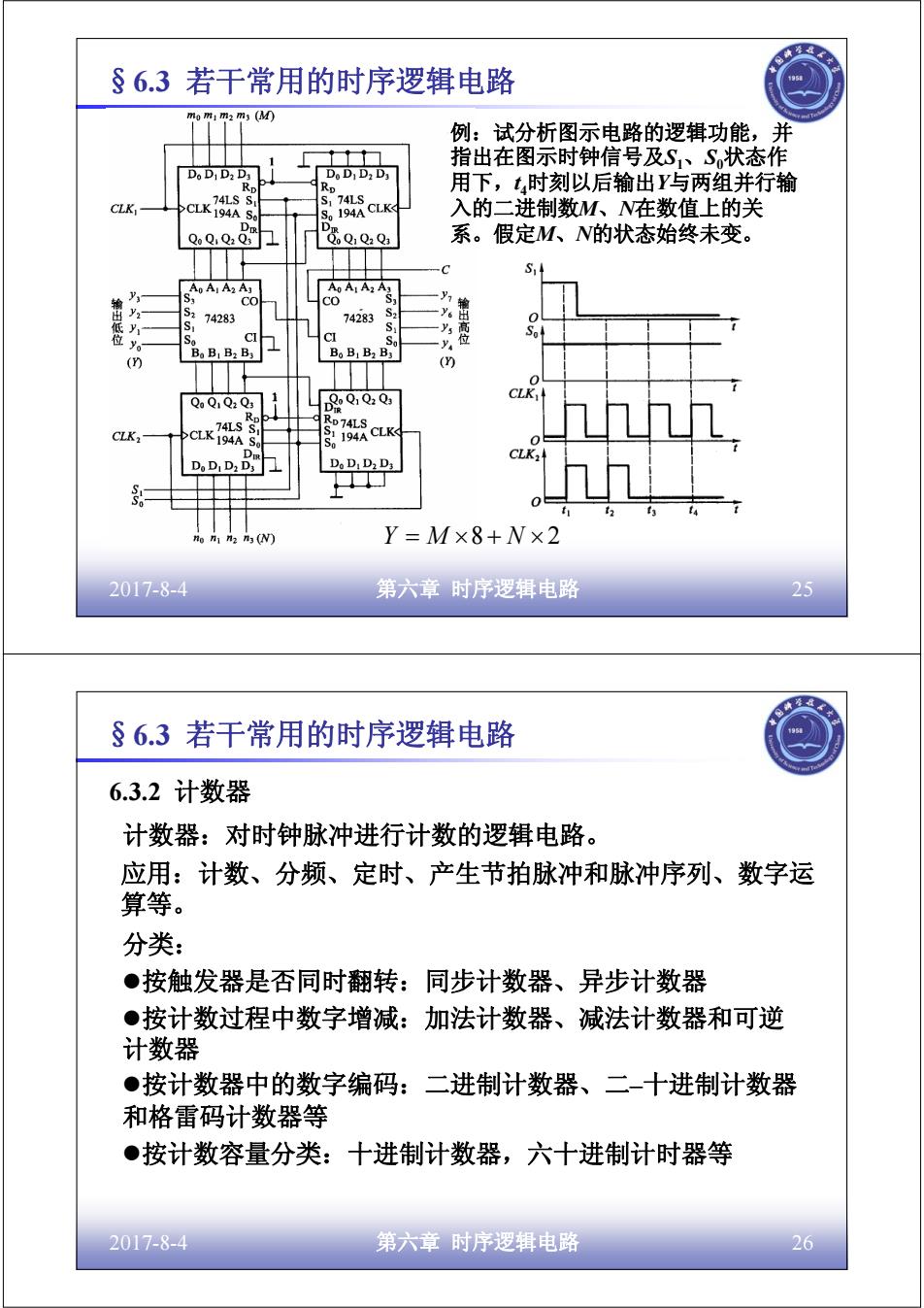

§6.3 若干常用的时序逻辑电路 mo mi m2 ms (M) 例:试分析图示电路的逻辑功能,并 指出在图示时钟信号及S1、S状态作 DoD1D2 D3 Do D:D2 D3 PCIK R Rp 用下,t时刻以后输出Y与两组并行输 74LS CLK 194A CLK 入的二进制数M、N在数值上的关 0.0,8 Qo Q:Q2 Qa 系。假定M、N的状态始终未变。 AoAI A2A3 Co co 输出低位 y 74283 74283 C1 输出高位 B。B1B2B1 B。B1B2B3 y () DQ:Q:Q CLK Qo Q1 Q2Q3 R 74LS S RD74LS CLK2 CLK 194A S:194A CLK D D。D1D2D3 CLK: DoDID2 D; n2 n3 (N) Y=M×8+N×2 2017-8-4 第六章时序逻辑电路 25 §6.3若干常用的时序逻辑电路 6.3.2计数器 计数器:对时钟脉冲进行计数的逻辑电路。 应用:计数、分频、定时、产生节拍脉冲和脉冲序列、数字运 算等。 分类: ●按触发器是否同时翻转:同步计数器、」 异步计数器 ●按计数过程中数字增减:加法计数器、 减法计数器和可逆 计数器 ●按计数器中的数字编码:二进制计数器、二-十进制计数器 和格雷码计数器等 ●按计数容量分类:十进制计数器,六十进制计时器等 2017-8-4 第六章时序逻辑电路 26

2017-8-4 第六章 时序逻辑电路 25 例:试分析图示电路的逻辑功能,并 指出在图示时钟信号及S1、S0状态作 用下,t4时刻以后输出Y与两组并行输 入的二进制数M、N在数值上的关 系。假定M、N的状态始终未变。 Y = M ×8 + N × 2 §6.3 若干常用的时序逻辑电路 2017-8-4 第六章 时序逻辑电路 26 6.3.2 计数器 计数器:对时钟脉冲进行计数的逻辑电路。 应用:计数、分频、定时、产生节拍脉冲和脉冲序列、数字运 算等。 分类: z按触发器是否同时翻转:同步计数器、异步计数器 z按计数过程中数字增减:加法计数器、减法计数器和可逆 计数器 z按计数器中的数字编码:二进制计数器、二–十进制计数器 和格雷码计数器等 z按计数容量分类:十进制计数器,六十进制计时器等 §6.3 若干常用的时序逻辑电路

§6.3若干常用的时序逻辑电路 同步二进制加法计数器 同步二进制计数器同步二进制减法计数器 同步二进制加/减计数器 同步计数器 同步十进制加法计数器 同步十进制计数器同步十进制减法计数器 同步十进制加/减计数器 计数器 「异步二进制加法计数器 异步计数器 异步二进制计数器 异步二进制减法计数器 异步十进制计数器 M<N 任意进制计数器的构成方法 M>N 移位寄存器型计数器 环形计数器 扭环形计数器 2017-8-4 第六章时序逻辑电路 27 §6.3若干常用的时序逻辑电路 一、同步计数器 1011 1同步二进制计数器 (1)同步二进制加法计数器 1011100 原理:根据二进制加法运算规则可知,在一个多位二进制数 末位加1,若第i位以下皆为1时,则第i位应改变状态。而最 低位的状态在每次加1时都要改变。 同步计数器通常用T触发器构成,结构形式有两种。控制输入 端T和控制时钟信号。 ①控制输入端T: I=1,T=g102g0=g (i=1,2,…,n-1) 2017-8-4 第六章时序逻辑电路 28

2017-8-4 第六章 时序逻辑电路 27 §6.3 若干常用的时序逻辑电路 ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎩ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎪ ⎨ ⎧ ⎩ ⎨ ⎧ ⎩ ⎨ ⎧ > < ⎪ ⎩ ⎪ ⎨ ⎧ ⎩ ⎨ ⎧ ⎪ ⎪ ⎪ ⎪ ⎩ ⎪ ⎪ ⎪ ⎪ ⎨ ⎧ ⎪ ⎩ ⎪ ⎨ ⎧ ⎪ ⎩ ⎪ ⎨ ⎧ 扭环形计数器 环形计数器 移位寄存器型计数器 任意进制计数器的构成方法 异步十进制计数器 异步二进制减法计数器 异步二进制加法计数器 异步二进制计数器 异步计数器 同步十进制加 减计数器 同步十进制减法计数器 同步十进制加法计数器 同步十进制计数器 同步二进制加 减计数器 同步二进制减法计数器 同步二进制加法计数器 同步二进制计数器 同步计数器 计数器 M N M N / / 2017-8-4 第六章 时序逻辑电路 28 一、同步计数器 1 同步二进制计数器 (1)同步二进制加法计数器 原理:根据二进制加法运算规则可知,在一个多位二进制数 末位加1,若第i 位以下皆为1时,则第i 位应改变状态。而最 低位的状态在每次加1时都要改变。 同步计数器通常用T触发器构成,结构形式有两种。控制输入 端T和控制时钟信号。 ①控制输入端T: 1, T0 ≡ ... ( 1,2, , 1) 1 0 = 1 ⋅ 2 1 ⋅ 0 =∏ = − − = T Q − Q − Q Q Q i n i j i i i j L §6.3 若干常用的时序逻辑电路

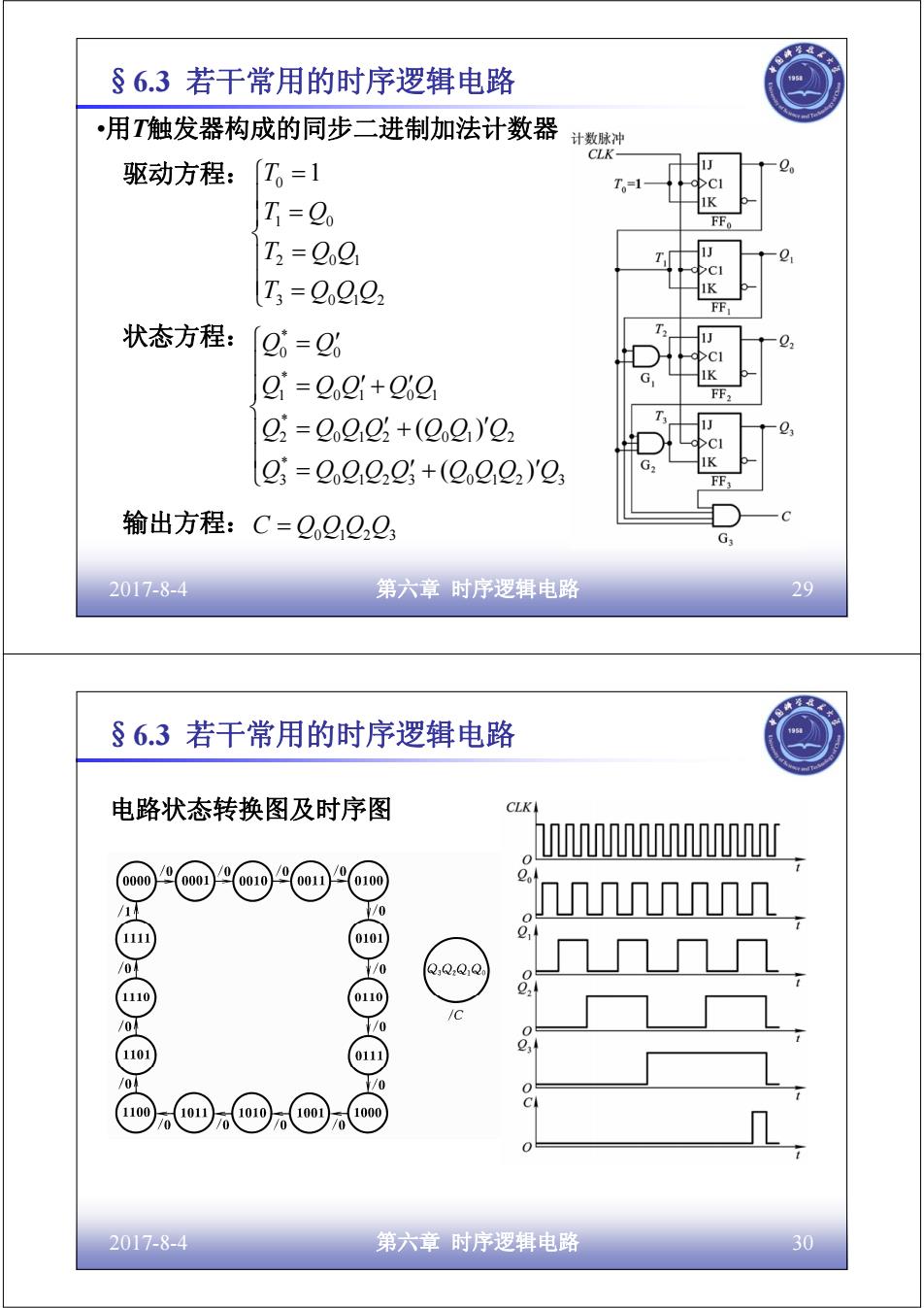

§6.3若干常用的时序逻辑电路 ·用T触发器构成的同步二进制加法计数器 计数脉冲 CLK 驱动方程: T,=1 T。1 T=C0 FF T2=0Q T3=Q202 1K FF 状态方程: es =0i g=92+Q62 G FF2 Q2=Q2Q3+(QQ)'Q2 >C1 g=Q222g+(0202)'Q FF 输出方程:C=Q2Q2Q G 2017-8-4 第六章时序逻辑电路 29 §6.3若干常用的时序逻辑电路 电路状态转换图及时序图 CLKI 0000 0001 0010 0 0011 0100 /0 1111 0101 /0 /0 QQQQ 0110 /c /0 0111 0 1100 1011 1010 1001 1000 /0 2017-8-4 第六章时序逻辑电路 30

2017-8-4 第六章 时序逻辑电路 29 •用T触发器构成的同步二进制加法计数器 驱动方程: ⎪ ⎪ ⎩ ⎪ ⎪ ⎨ ⎧ = = = = 3 0 1 2 2 0 1 1 0 0 1 T Q Q Q T Q Q T Q T 状态方程: ⎪ ⎪ ⎩ ⎪ ⎪ ⎨ ⎧ = ′ + ′ = ′ + ′ = ′ + ′ = ′ 0 1 2 3 0 1 2 3 * 3 0 1 2 0 1 2 * 2 0 1 0 1 * 1 0 * 0 ( ) ( ) Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 输出方程:C = Q0Q1Q2Q3 §6.3 若干常用的时序逻辑电路 2017-8-4 第六章 时序逻辑电路 30 电路状态转换图及时序图 §6.3 若干常用的时序逻辑电路