◆第三阶段,DSP的完善阶段 (2000年以后) >信号处理能力更加完善,而且使系统开发更加方 便、程序编辑调试更加灵活、功耗进一步降低、 成本不断下降 >各种通用外设集成到片上,大大地提高了数字信 号处理能力 >DSP运算速度可达到单指令周期10ns左右,可在 Windows下用C语言编程,使用方便灵活 >广泛应用:通信、计算机领域,并渗透到日常消 费领域 15

◆ 第三阶段,DSP的完善阶段(2000年以后) ➢信号处理能力更加完善,而且使系统开发更加方 便、程序编辑调试更加灵活、功耗进一步降低、 成本不断下降 ➢各种通用外设集成到片上,大大地提高了数字信 号处理能力 ➢ DSP运算速度可达到单指令周期10ns左右,可在 Windows 下用C语言编程,使用方便灵活 ➢广泛应用:通信、计算机领域,并渗透到日常消 费领域 15

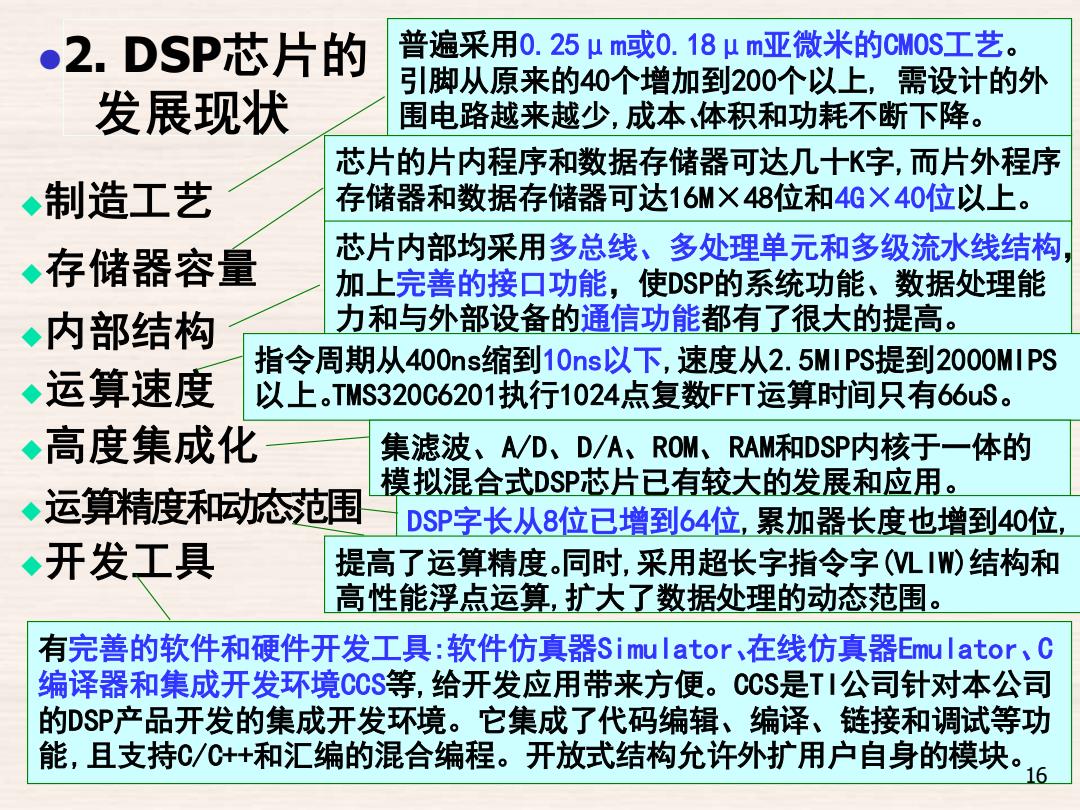

2.DSP芯片的 普遍采用0.25μm或0.18μm亚微米的cM0S工艺。 引脚从原来的40个增加到200个以上,需设计的外 发展现状 围电路越来越少,成本、体积和功耗不断下降。 芯片的片内程序和数据存储器可达几十K字,而片外程序 ◆制造工艺 存储器和数据存储器可达16MX48位和4G×40位以上。 ◆存储器容量 芯片内部均采用多总线、多处理单元和多级流水线结构, 加上完善的接口功能,使DSP的系统功能、数据处理能 ◆内部结构 力和与外部设备的通信功能都有了很大的提高。 指令周期从400ns缩到10ns以下,速度从2.5MIPS提到2000MIPS ◆运算速度 以上。TMS320C6201执行1024点复数FFT运算时间只有66uS。 ◆高度集成化 集滤波、AWD、D/A、ROM、RAM和DSP内核于一体的 模拟混合式DSP芯片已有较大的发展和应用。 ◆运算精度和动态范围 DSP字长从8位已增到64位,累加器长度也增到40位, ◆开发工具 提高了运算精度同时,采用超长字指令字(LI)结构和 高性能浮点运算,扩大了数据处理的动态范围。 有完善的软件和硬件开发工具:软件仿真器Simulator,在线仿真器Emulator、C 编译器和集成开发环境CCS等,给开发应用带来方便。CCS是T1公司针对本公司 的DSP产品开发的集成开发环境。它集成了代码编辑、编译、链接和调试等功 能,且支持C/C++和汇编的混合编程。开放式结构允许外扩用户自身的模块。 16

◆制造工艺 ◆存储器容量 ◆内部结构 ◆运算速度 ◆高度集成化 ◆运算精度和动态范围 ◆开发工具 有完善的软件和硬件开发工具:软件仿真器Simulator、在线仿真器Emulator、C 编译器和集成开发环境CCS等,给开发应用带来方便。CCS是TI公司针对本公司 的DSP产品开发的集成开发环境。它集成了代码编辑、编译、链接和调试等功 能,且支持C/C++和汇编的混合编程。开放式结构允许外扩用户自身的模块。 普遍采用0.25μm或0.18μm亚微米的CMOS工艺。 引脚从原来的40个增加到200个以上, 需设计的外 围电路越来越少,成本、体积和功耗不断下降。 芯片的片内程序和数据存储器可达几十K字,而片外程序 存储器和数据存储器可达16M×48位和4G×40位以上。 芯片内部均采用多总线、多处理单元和多级流水线结构, 加上完善的接口功能,使DSP的系统功能、数据处理能 力和与外部设备的通信功能都有了很大的提高。 指令周期从400ns缩到10ns以下,速度从2.5MIPS提到2000MIPS 以上。TMS320C6201执行1024点复数FFT运算时间只有66uS。 集滤波、A/D、D/A、ROM、RAM和DSP内核于一体的 模拟混合式DSP芯片已有较大的发展和应用。 DSP字长从8位已增到64位,累加器长度也增到40位, 提高了运算精度。同时,采用超长字指令字(VLIW)结构和 高性能浮点运算,扩大了数据处理的动态范围。 ⚫2. DSP芯片的 发展现状 16

●3.DSP技术的发展趋势 ◆DSP的内核结构将进一步改善 ◆DSP和微控制器的融合 ◆DSP和高档CPU的融合 ◆DSP和FPGA、CPLD的融合 ◆实时操作系统RTOS与DSP的结合 ◆DSP的并行处理结构 ◆功耗越来越低 17

⚫3. DSP技术的发展趋势 ◆ DSP的内核结构将进一步改善 ◆ DSP和微控制器的融合 ◆ DSP和高档CPU的融合 ◆ DSP 和FPGA、CPLD的融合 ◆ 实时操作系统RTOS与DSP的结合 ◆ DSP的并行处理结构 ◆ 功耗越来越低 17