第2章TMS320C55x的硬件结构 ■2.1TMS320C55x的总体结构 ■2.2封装和引脚功能 ■2.3CPU结构 ■2.4CPU寄存器 ■2.5存储空间和1/O空间 ▣2.6堆栈操作 ■2.7中断和复位操作 3

第2章 TMS320C55x的硬件结构 ◼ 2.1 TMS320C55x的总体结构 ◼ 2.2 封装和引脚功能 ◼ 2.3 CPU结构 ◼ 2.4 CPU寄存器 ◼ 2.5 存储空间和I/O空间 ◼ 2.6 堆栈操作 ◼ 2.7 中断和复位操作 3

2.1TMS320C55x的总体结构 ·C55x芯片由CPU、存储空间、片内外设、 内部总线组成 。不同芯片(例C5501,C5509A,C5510) 体系结构相同,具有相同的CPU,片上 存储器和外围电路配置以及封装引脚等 有所不同(具体见芯片手册)。 参考:TMS320VC5509 A Fixed-Point Digital Signal Processor-Data Manual-SPRS205K-2008.pdf 4

2.1 TMS320C55x的总体结构 ⚫ C55x芯片由CPU、存储空间、片内外设、 内部总线组成 ⚫ 不同芯片(例C5501, C5509A, C5510) 体系结构相同,具有相同的CPU,片上 存储器和外围电路配置以及封装引脚等 有所不同(具体见芯片手册)。 参考: TMS320VC5509A Fixed-Point Digital Signal Processor-Data Manual-SPRS205K-2008年版.pdf 4

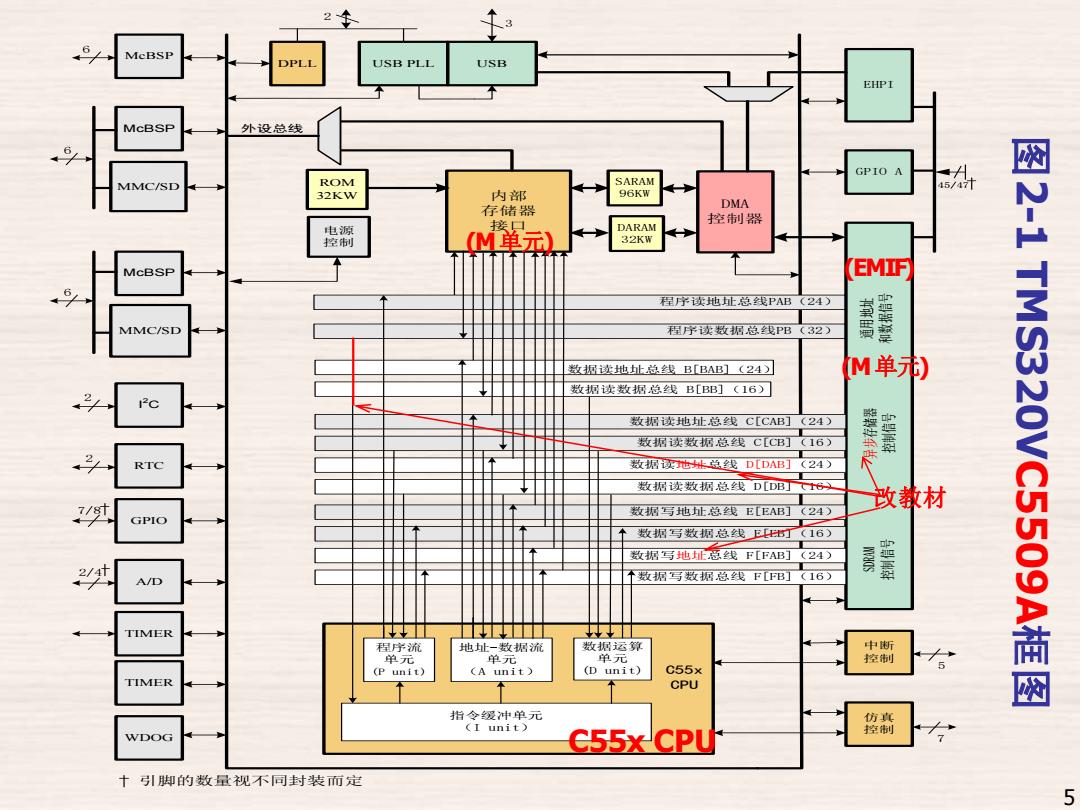

6 McBSP EHPI McBSP 外设总线 GPIO A MMC/SD ROM SARAM 32KW 内部 96KW 存储器 DMA 接▣ DARAM 控带荆器 电源 空伟制 M单元) 32KW McBSP EMIF 程序地址总线PAB(24) MMC/SD 星序读数据总线PB(32) 数据读地止总线B[BAB1(24) M单) 数据读数据总线B[BB](16) 数据读地址总线C[CAB] (24) 数据读数据总线C[CB](16) 篷置 2 RTC 数据读地址总线D[DAB](24) 数据读数据总线D[DB丁 改教材 数据写地址总线E[EAB]■(24) GPIO 数据写数据总线卫生出丁(16) 数据写地址总线F[FAB](24) 2/4 募 A/D 数据写数烟总线F[FB](16) 图2-1TMS320VC550SA程窗 TIMER ■ ■■■ 程序流 地址一数据流 数据运算 中断 单元 单元 单元 控制 (P unit) (A unit) (D unit) C55x TIMER CPU 指令缓冲单元 仿 (I unit) C55x CPU 控制 WDOG 十引脚的数量视不同封装而定 5

M c B S P R T C I 2 C M M C / S D M c B S P W D O G T I M E R A / D G P I O T I M E R M c B S P M M C / S D D P L L U S B P L L U S B R O M 3 2 K W 电 源 控 制 内 部 存 储 器 接 口 S A R A M 9 6 K W D A R A M 3 2 K W D M A 控 制 器 E H P I G P I O A 程 序 流 单 元 ( P u n i t ) 地 址 - 数 据 流 单 元 ( A u n i t ) 数 据 运 算 单 元 ( D u n i t ) 指 令 缓 冲 单 元 ( I u n i t ) C 5 5 x C P U 中 断 控 制 仿 真 控 制 SDRAM 控制信号 异步存储器 控制信号 通用地址 和数据信号 6 66 22 7 / 8 2 / 4 754 5 / 4 7 3 2 外 设 总 线 引 脚 的 数 量 视 不 同 封 装 而 定 数 据 读 地 址 总 线 B [ B A B ] ( 2 4 ) 数 据 读 数 据 总 线 B [ B B ] ( 1 6 ) 程 序 读 地 址 总 线 P A B ( 2 4 ) 程 序 读 数 据 总 线 P B ( 3 2 ) 数 据 读 地 址 总 线 C [ C A B ] ( 2 4 ) 数 据 读 数 据 总 线 C [ C B ] ( 1 6 ) 数 据 读 地 址 总 线 D [ D A B ] ( 2 4 ) 数 据 读 数 据 总 线 D [ D B ] ( 1 6 ) 数 据 写 地 址 总 线 E [ E A B ] ( 2 4 ) 数 据 写 数 据 总 线 E [ E B ] ( 1 6 ) 数 据 写 地 址 总 线 F [ F A B ] ( 2 4 ) 数 据 写 数 据 总 线 F [ F B ] ( 1 6 ) 改教材 5 (M 单元 ) C55x CPU (EMIF) 图2-1 TMS320VC5509A框图 (M 单元 )

2.1TMS320C55x的总体结构 2.1.1C55xCPU内部总线结构 2.1.2C55x的CPU组成 2.1.3C55x存储器配置 。2.1.4C55x外设配置 6

2.1 TMS320C55x的总体结构 ⚫ 2.1.1 C55x CPU内部总线结构 ⚫ 2.1.2 C55x的CPU组成 ⚫ 2.1.3 C55x存储器配置 ⚫ 2.1.4 C55x外设配置 6

2.1.1C55xCPU内部总线结构 ●内部独立总线:12组 ◆程序地址总线(PAB):1组,24位 ◆程序数据总线(PDB):1组,32位 ◆数据读地址总线(BAB、CAB、DAB):3组,24位 ◆数据读总线(BB、CB、DB):3组,16位 ◆数据写地址总线(EAB、FAB):2组,24位 ◆数据写总线(EB、FB):2组,16位。 7

2.1.1 C55x CPU内部总线结构 ⚫内部独立总线:12组 ◆ 程序地址总线(PAB):1组,24位 ◆ 程序数据总线(PDB):1组,32位 ◆ 数据读地址总线(BAB、CAB、DAB):3组,24位 ◆ 数据读总线(BB、CB、DB):3组,16位 ◆ 数据写地址总线(EAB、FAB):2组,24位 ◆ 数据写总线(EB、FB):2组,16位。 7