dsP1C30F4011/4012 表1-1: dsPIC30F4011引脚说明(续) 引脚名称 引脚 缓冲器 类型 类型 说明 OSC1 ST/CMOS 晶振输入。配置在RC模式时为ST缓冲器输入;否则为CMOS输入。 OSC2 1/O 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在RC和EC模式 下用作CLKO。 PGD 1/O ST 在线串行编程数据输入/输出引脚。 PGC ST 在线串行编程时钟输入引脚。 RBO-RB8 1/O ST PORTB是双向/O端口。 8RC13-RC15 81/○ 8ST PORTC是双向VO端口。 RDO-RD3 V/O ST PORTD是双向VO端口. REO-RE5. O ST PORTE是双向VO端口。 RE8 RFO-RF6 l/O ST PORTF是双向VO端口 SCK1 1/O ST SPI1的同步串行时钟输入/输出。 SDI1 ST SPI1数据输入。 SDO1 0 SPI1数据输出. SS1 ST SPI1同步从动模式。 SCL 1/O ST 2Cw的同步串行时钟输入/输出。 SDA 1O ST 2℃的同步串行数据输入/输出。 sosco 32kHz低功耗晶振输出。 SOSCI ST/CMOS 32kHz低功耗晶振输入。配置为RC模式时为ST缓冲器输入:否则为CMOS 输入。 T1CK Timer1外部时钟输入。 T2CK T Timer2外部时钟输入。 U1RX ST UART1接收. U1TX 0 UART1发送 U1ARX ST UART1备用接收。 U1ATX 0 UART1备用发送。 U2RX ST UART2接收。 U2TX 0 UART2发送. VoD P 一 逻辑和VO引脚的正电源。 Vss 逻辑和/O引脚的参考地. VREF+ Analog 模拟参考电压(高电压)输入。 VREF- Analog模拟参考电压(低电压)输入。 图注: CMOS= CMOS兼容输入或输出 Analog= 模拟输入 ST CMOS电平的施密特触发器输入 0 = 输出 =输入 P =电源 DS70135ECN第10页 2007 Microchip Technology Inc

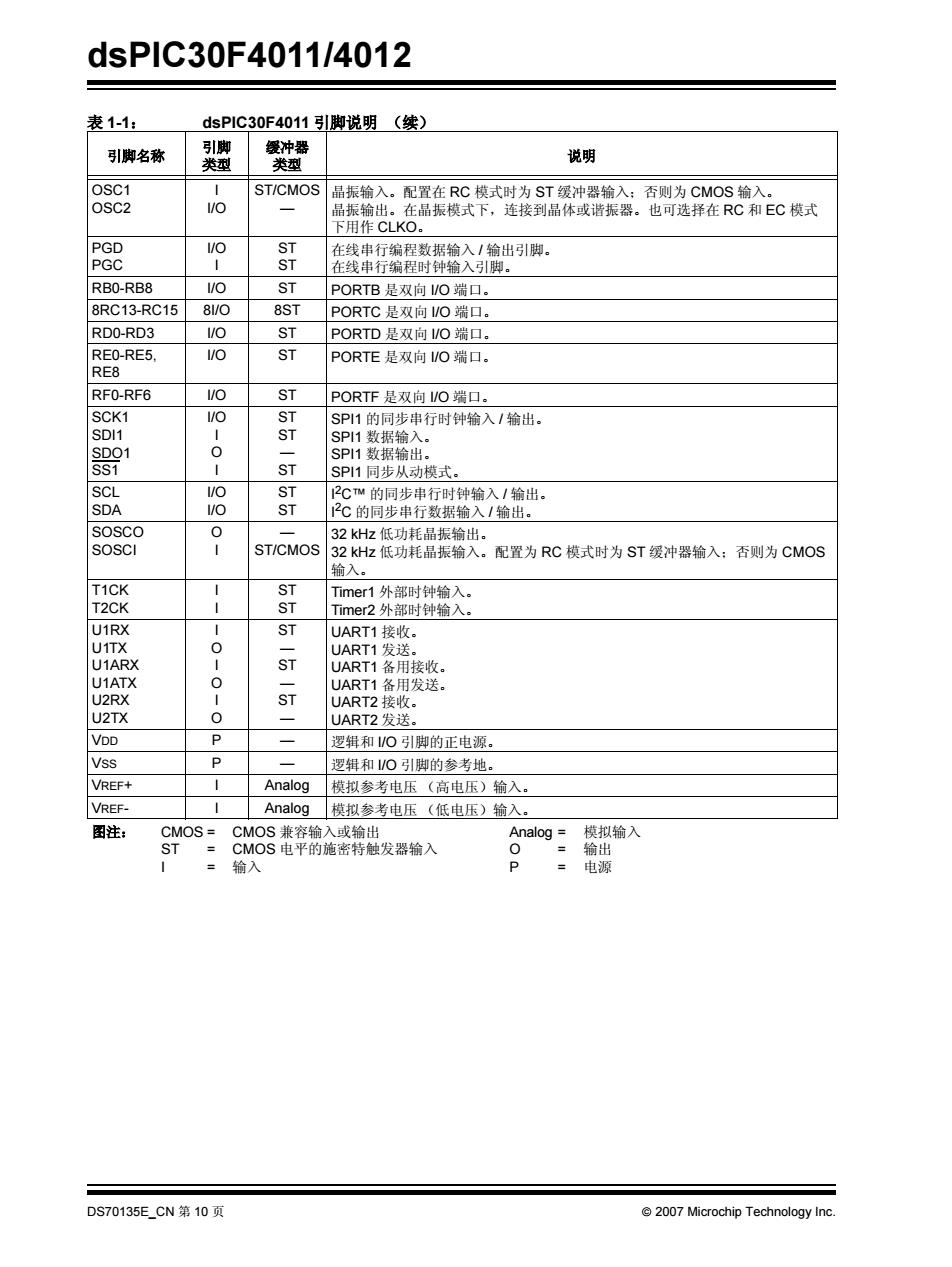

dsPIC30F4011/4012 DS70135E_CN 第 10 页 2007 Microchip Technology Inc. OSC1 OSC2 I I/O ST/CMOS — 晶振输入。配置在 RC 模式时为 ST 缓冲器输入;否则为 CMOS 输入。 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在 RC 和 EC 模式 下用作 CLKO。 PGD PGC I/O I ST ST 在线串行编程数据输入 / 输出引脚。 在线串行编程时钟输入引脚。 RB0-RB8 I/O ST PORTB 是双向 I/O 端口。 8RC13-RC15 8I/O 8ST PORTC 是双向 I/O 端口。 RD0-RD3 I/O ST PORTD 是双向 I/O 端口。 RE0-RE5, RE8 I/O ST PORTE 是双向 I/O 端口。 RF0-RF6 I/O ST PORTF 是双向 I/O 端口。 SCK1 SDI1 SDO1 SS1 I/O I O I ST ST — ST SPI1 的同步串行时钟输入 / 输出。 SPI1 数据输入。 SPI1 数据输出。 SPI1 同步从动模式。 SCL SDA I/O I/O ST ST I 2C™ 的同步串行时钟输入 / 输出。 I 2C 的同步串行数据输入 / 输出。 SOSCO SOSCI O I — ST/CMOS 32 kHz 低功耗晶振输出。 32 kHz 低功耗晶振输入。配置为 RC 模式时为 ST 缓冲器输入;否则为 CMOS 输入。 T1CK T2CK I I ST ST Timer1 外部时钟输入。 Timer2 外部时钟输入。 U1RX U1TX U1ARX U1ATX U2RX U2TX I O I O I O ST — ST — ST — UART1 接收。 UART1 发送。 UART1 备用接收。 UART1 备用发送。 UART2 接收。 UART2 发送。 VDD P — 逻辑和 I/O 引脚的正电源。 VSS P — 逻辑和 I/O 引脚的参考地。 VREF+ I Analog 模拟参考电压 (高电压)输入。 VREF- I Analog 模拟参考电压 (低电压)输入。 表 1-1: dsPIC30F4011 引脚说明 (续) 引脚名称 引脚 类型 缓冲器 类型 说明 图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入 P = 电源

dsPIC30F4011/4012 表1-2对器件的/O引脚配置和端口引脚的复用功能进 行了简要说明。端口引脚可具有多种功能。当发生复用 时,外设模块的功能要求可强制替代端口引脚的数据方 向。 表1-2: dsP1C30F4012引脚说明 引脚名称 引脚 缓冲器 类型 类型 说明 ANO-AN5 Analog 模拟输入通道。AN0和AN1也分别用于器件编程数据和时钟输入。 AVDD ⊙ P 模拟模块的正电源。 AVss P P 模拟模块的参考地。 CLKI ST/CMOS 外部时钟源输入。总是与OSC1引脚功能相关联。 CLKO 0 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在RC和EC模式 下用作CLKO. 总是与OSC2引脚功能相关联。 CNO-CN7 ST 输入电平变化通知输入。可将所有输入软件编程为内部弱上拉。 C1RX ST CAN1总线接收引脚。 C1TX 0 CAN1总线发送引脚。 EMUD VO ST ICD主通信通道数据输入/输出引脚。 EMUC VO ST 1CD主通信通道时钟输入/输出引脚。 EMUD1 l/O ST 1CD第二通信通道数据输入/输出引脚。 EMUC1 lO 1CD第二通信通道时钟输入/输出引脚。 EMUD2 lO ST 1CD第三通信通道数据输入I输出引脚。 EMUC2 1/O CD第三通信通道时钟输入/输出引脚. EMUD3 l/O T 1CD第四通信通道数据输入/输出引脚。 EMUC3 VO ST 1CD第四通信通道时钟输入/输出引脚。 1C1,IC2,1C7, ST 捕捉输入1、2、7和8。 IC8 INDX 正交编码器索引脉冲输入。 QEA T 在QE模式下为正交编码器A相输入。 在定时器模式下为辅助定时器外部时钟/门控输入。 QEB ST 在QEI模式下为正交编码器A相输入。 在定时器模式下为辅助定时器外部时钟/门控输入。 INTO ST 外部中断0。 INT1 T 外部中断1。 INT2 外部中断2. FLTA ST PWM故障A输入. PWM1L 0 PWM1低瑞输出. PWM1H 0 PWM1高端输出. PWM2L PWM2低端输出。 PWM2H 0 PWM2高端输出. PWM3L 0 PWM3低端输出。 PWM3H 0 PWM3高端输出. MCLR I/P ST 主复位输入或编程电压输入。此引脚为低电平有效的器件复位输入端。 OCFA ST 比较故障A输入(对于比较通道1、2、3和4)。 0C1,0C2 O 比较输出1和2。 图注: CMOS= CMOS兼容输入或输出 Analog=模拟输入 ST = CMOS电平的施密特触发器输入 0 =输出 输入 =电源 @2007 Microchip Technology Inc. DS70135ECN第11页

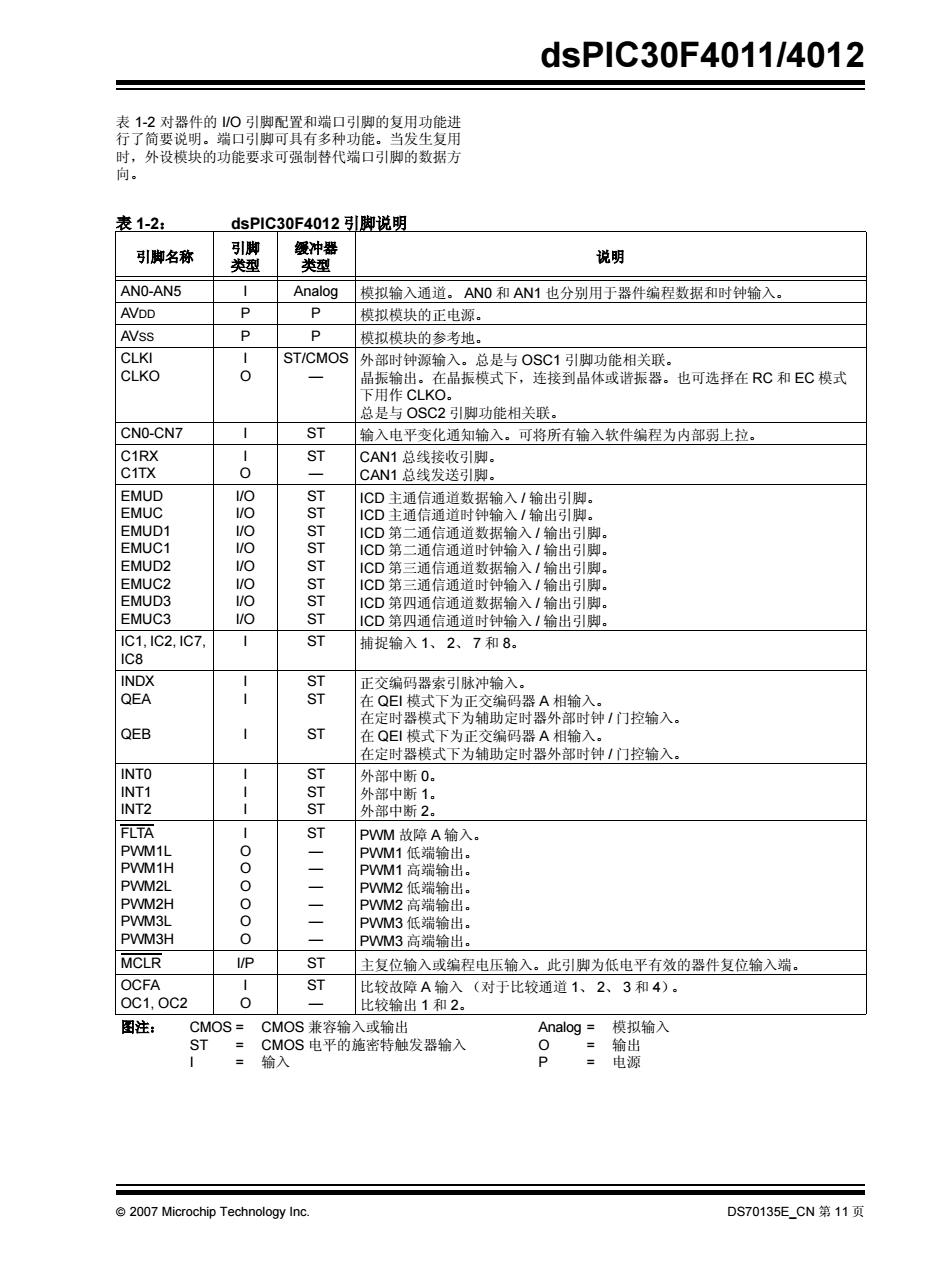

2007 Microchip Technology Inc. DS70135E_CN 第 11 页 dsPIC30F4011/4012 表 1-2 对器件的 I/O 引脚配置和端口引脚的复用功能进 行了简要说明。端口引脚可具有多种功能。当发生复用 时,外设模块的功能要求可强制替代端口引脚的数据方 向。 表 1-2: dsPIC30F4012 引脚说明 引脚名称 引脚 类型 缓冲器 类型 说明 AN0-AN5 I Analog 模拟输入通道。 AN0 和 AN1 也分别用于器件编程数据和时钟输入。 AVDD P P 模拟模块的正电源。 AVSS P P 模拟模块的参考地。 CLKI CLKO I O ST/CMOS — 外部时钟源输入。总是与 OSC1 引脚功能相关联。 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在 RC 和 EC 模式 下用作 CLKO。 总是与 OSC2 引脚功能相关联。 CN0-CN7 I ST 输入电平变化通知输入。可将所有输入软件编程为内部弱上拉。 C1RX C1TX I O ST — CAN1 总线接收引脚。 CAN1 总线发送引脚。 EMUD EMUC EMUD1 EMUC1 EMUD2 EMUC2 EMUD3 EMUC3 I/O I/O I/O I/O I/O I/O I/O I/O ST ST ST ST ST ST ST ST ICD 主通信通道数据输入 / 输出引脚。 ICD 主通信通道时钟输入 / 输出引脚。 ICD 第二通信通道数据输入 / 输出引脚。 ICD 第二通信通道时钟输入 / 输出引脚。 ICD 第三通信通道数据输入 / 输出引脚。 ICD 第三通信通道时钟输入 / 输出引脚。 ICD 第四通信通道数据输入 / 输出引脚。 ICD 第四通信通道时钟输入 / 输出引脚。 IC1, IC2, IC7, IC8 I ST 捕捉输入 1、 2、 7 和 8。 INDX QEA QEB I I I ST ST ST 正交编码器索引脉冲输入。 在 QEI 模式下为正交编码器 A 相输入。 在定时器模式下为辅助定时器外部时钟 / 门控输入。 在 QEI 模式下为正交编码器 A 相输入。 在定时器模式下为辅助定时器外部时钟 / 门控输入。 INT0 INT1 INT2 I I I ST ST ST 外部中断 0。 外部中断 1。 外部中断 2。 FLTA PWM1L PWM1H PWM2L PWM2H PWM3L PWM3H I O O O O O O ST — — — — — — PWM 故障 A 输入。 PWM1 低端输出。 PWM1 高端输出。 PWM2 低端输出。 PWM2 高端输出。 PWM3 低端输出。 PWM3 高端输出。 MCLR I/P ST 主复位输入或编程电压输入。此引脚为低电平有效的器件复位输入端。 OCFA OC1, OC2 I O ST — 比较故障 A 输入 (对于比较通道 1、 2、 3 和 4)。 比较输出 1 和 2。 图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入 P = 电源

dsP1C30F4011/4012 表1-2: dsPIC30F4012引脚说明(续) 引脚名称 引脚 缓冲器 类型 类型 说明 OSC1 ST/CMOS 晶振输入。配置在RC模式时为ST缓冲器输入:否则为CMOS输入。 OSC2 1/O 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在RC和EC模式 下用作CLKO。 PGD 1/O ST 在线串行编程数据输入/输出引脚。 PGC ST 在线串行编程时钟输入引脚。 RBO-RB5 1/O ST PORTB是双向/O端口。 RC13-RC15 81/○ 8ST PORTC是双向VO端口。 RDO-RD1 V/O ST PORTD是双向VO端口. REO-RE5. O ST PORTE是双向VO端口。 RE8 RF2-RF3 l/O ST PORTF是双向VO端口 SCK1 1/O ST SPI1的同步串行时钟输入/输出。 SDI1 ST SPI1数据输入。 SDO1 0 SP11数据输出。 SS1 l/O ST SPI1同步从动模式。 SCL 1/O ST 2Cw的同步串行时钟输入/输出。 SDA 1O ST 2℃的同步串行数据输入/输出。 sosco 0 32kHz低功耗晶振输出。 SOSCI ST/CMOS 32kHz低功耗晶振输入。配置为RC模式时为ST缓冲器输入:否则为CMOS 输入。 T1CK Timer1外部时钟输入。 T2CK T Timer2外部时钟输入。 U1RX ST UART1接收. U1TX 0 UART1发送 U1ARX ST UART1备用接收。 U1ATX 0 UART1备用发送. VDD P 逻辑和/O引脚的正电源。 Vss P 逻辑和VO引脚的参考地。 VREF+ Analog 模拟参考电压(高电压)输入。 VREF- Analog 模拟参考电压(低电压)输入。 图注: CMOS= CMOS兼容输入或输出 Analog=模拟输入 ST=CMOS电平的施密特触发器输入 0 输出 =输入 =电源 DS70135ECN第12页 2007 Microchip Technology Inc

dsPIC30F4011/4012 DS70135E_CN 第 12 页 2007 Microchip Technology Inc. OSC1 OSC2 I I/O ST/CMOS — 晶振输入。配置在 RC 模式时为 ST 缓冲器输入;否则为 CMOS 输入。 晶振输出。在晶振模式下,连接到晶体或谐振器。也可选择在 RC 和 EC 模式 下用作 CLKO。 PGD PGC I/O I ST ST 在线串行编程数据输入 / 输出引脚。 在线串行编程时钟输入引脚。 RB0-RB5 I/O ST PORTB 是双向 I/O 端口。 RC13-RC15 8I/O 8ST PORTC 是双向 I/O 端口。 RD0-RD1 I/O ST PORTD 是双向 I/O 端口。 RE0-RE5, RE8 I/O ST PORTE 是双向 I/O 端口。 RF2-RF3 I/O ST PORTF 是双向 I/O 端口。 SCK1 SDI1 SDO1 SS1 I/O I O I/O ST ST — ST SPI1 的同步串行时钟输入 / 输出。 SPI1 数据输入。 SPI1 数据输出。 SPI1 同步从动模式。 SCL SDA I/O I/O ST ST I 2C™ 的同步串行时钟输入 / 输出。 I 2C 的同步串行数据输入 / 输出。 SOSCO SOSCI O I — ST/CMOS 32 kHz 低功耗晶振输出。 32 kHz 低功耗晶振输入。配置为 RC 模式时为 ST 缓冲器输入;否则为 CMOS 输入。 T1CK T2CK I I ST ST Timer1 外部时钟输入。 Timer2 外部时钟输入。 U1RX U1TX U1ARX U1ATX I O I O ST — ST — UART1 接收。 UART1 发送。 UART1 备用接收。 UART1 备用发送。 VDD P — 逻辑和 I/O 引脚的正电源。 VSS P — 逻辑和 I/O 引脚的参考地。 VREF+ I Analog 模拟参考电压 (高电压)输入。 VREF- I Analog 模拟参考电压 (低电压)输入。 表 1-2: dsPIC30F4012 引脚说明 (续) 引脚名称 引脚 类型 缓冲器 类型 说明 图注: CMOS = CMOS 兼容输入或输出 Analog = 模拟输入 ST = CMOS 电平的施密特触发器输入 O = 输出 I = 输入 P = 电源

dsP1C30F4011/4012 2.0 CPU架构概述 使用任何工作寄存器,通过表读和表写指令,也可 以对程序空间内的32K字页进行线性间接访问。 注:本数据手册总结了dsPIC30F系列器件的功能,但是不 表读和表写指令能够用来访问一个指令字的全部 应把本手册当作无所不包的参考手册来使用。有关CPU、外 24位。 设、寄存器说明和一般器件功能的更多信息,请参见 《dsPIC30F系列参考手册》(DS70046ECN)。有关器件 X和Y地址空间都支持无开销循环缓冲区(模寻址)。 指令集和编程的更多信,息,请参见《dsP1C30F33F程序 模寻址的主要目的是要消除DSP算法的循环开销。 员参考手册》(DS70157BCN)。 XAGU还支持对目标有效地址进行位反转寻址,对于 本文档对dsP1C30F4011/4012的CPU和外设功能进行 基2FFT算法,这极大地简化了输入或输出数据的重 了简要概述。有关这些内容的完整说明,请参见 新排序。有关模寻址和位反转寻址的详细信息,请参见 《dsPIC30F系列参考手册》(DS70046ECN). 第4.0节“地址发生器单元”。 内核支持固有(无操作数)寻址、相对寻址、立即数寻 2.1 内核概述 址、存储器直接寻址、寄存器直接寻址、寄存器间接寻 内核的指令字长为24位。程序计数器(PC)为23位 址、寄存器偏移量寻址和立即数偏移量寻址模式。指令 宽,其最低有效位(Least Significant bit,LSb)始终 与预定义的寻址模式相关联,这取决于其功能需求。 清零(见第3.1节“程序地址空间”),最高有效位 对于大多数指令,内核能够在每个指令周期内执行一次 (Most Significant bit,MSb)在正常的程序执行期间被 数据(或程序数据)存储器读取、一次工作寄存器(数 忽略,某些专用指令除外。因此,PC能够寻址最大为 据)读取、一次数据存储器写入以及一次程序(指令) 4M指令字的用户程序空间。使用指令预取机制来帮助 存储器读取操作。因此,支持3操作数指令,允许在单 维持吞吐量。使用DO和REPEAT指令,支持无循环计 个周期内执行C=A+B这样的操作。 数管理开销的程序循环结构,并且这两条指令在任何时 内核包含DSP引擎,这极大地提高了内核的运算能力 候都可被中断。 和吞吐量。它具有一个高速17位x17位乘法器、一个 工作寄存器阵列由16个16位寄存器组成,每个工作寄 40位ALU、两个40位饱和累加器和一个40位双向桶 存器均可作为数据、地址或偏移量寄存器。一个工作寄 形移位寄存器。累加器或任何工作寄存器中的数据可以 存器(W15)用作中断和调用时的软件堆栈指针。 在单个周期内右移16位或左移16位。DSP指令可以 数据空间为64KB(32K字),被分成两块,称为X和 无缝地与所有其他指令一起操作,且设计为能获得最佳 Y数据存储区。每个存储块有各自独立的地址发生单元 实时性能。MAC类指令能够在从存储器取出两个数据操 (Address Generation Unit,.AGU)。大多数指令只通过 作数的同时,将两个W寄存器相乘。为了能够同时取两 X存储空间AGU进行操作,这样对外界而言数据空间就 个数据操作数,对于MAC类指令,数据空间拆分为两 是单独而统一的。乘-累加(Multiply-Accumulate,Mac) 块,对所有其他指令数据空间则是线性的。对于MAC类 类双源操作数DSP指令,通过X和Y的AGU进行操 指令,这是通过将某些工作寄存器专用于每个地址空 作,这将数据地址空间分成两个部分(见第3.2节“数 间,以透明而灵活的方式实现的。 据地址空间”)。X和Y数据空间边界视具体器件而定, 内核不支持多级指令流水线。不过,为了最大限度地获 用户不能改变它们。每个数据字由2个字节组成,大多 得可用的执行时间,使用了单级指令预取机制,在指令 数指令按字或字节对数据进行寻址。 执行的前一个周期取指令并部分译码指令。除了一些特 对于存储在程序存储器中的数据,有两种访问方法: 例外,大部分指令都在单个周期内执行。 ·数据存储空间的高32KB可以映射到程序空间的下 内核具有用于陷阱和中断的向量异常处理结构,具有62 半部分(用户空间),映射的边界可以是任何16K 个独立的向量。异常包括最多8个陷阱(其中有4个是 程序字边界,边界由8位程序空间可视性页 保留的)和54个中断。根据用户指定的1到7之间的 (Program Space Visibility Page,PSVPAG)寄存 优先级(1为最低优先级,7为最高优先级),以及预 器定义。这使得任何指令都能像访问数据空间那样 定义的“自然顺序”,决定每个中断的优先级。陷阱的 访问程序空间,但访问需要一个额外的周期。此 优先级是固定的,其范围从8到15。 外,使用这个方法,只能访问每个指令字的低16 位。 @2007 Microchip Technology Inc. DS70135ECN第13页

2007 Microchip Technology Inc. DS70135E_CN 第 13 页 dsPIC30F4011/4012 2.0 CPU 架构概述 本文档对 dsPIC30F4011/4012 的 CPU 和外设功能进行 了 简 要 概 述。有 关 这 些 内 容 的 完 整 说 明,请 参 见 《dsPIC30F 系列参考手册》(DS70046E_CN)。 2.1 内核概述 内核的指令字长为 24 位。程序计数器 (PC)为 23 位 宽,其最低有效位 (Least Significant bit, LSb)始终 清零 (见第 3.1 节 “程序地址空间”),最高有效位 (Most Significant bit,MSb)在正常的程序执行期间被 忽略,某些专用指令除外。因此, PC 能够寻址最大为 4M 指令字的用户程序空间。使用指令预取机制来帮助 维持吞吐量。使用 DO 和 REPEAT 指令,支持无循环计 数管理开销的程序循环结构,并且这两条指令在任何时 候都可被中断。 工作寄存器阵列由 16 个 16 位寄存器组成,每个工作寄 存器均可作为数据、地址或偏移量寄存器。一个工作寄 存器 (W15)用作中断和调用时的软件堆栈指针。 数据空间为 64 KB (32K 字),被分成两块,称为 X 和 Y 数据存储区。每个存储块有各自独立的地址发生单元 (Address Generation Unit,AGU)。大多数指令只通过 X 存储空间 AGU 进行操作,这样对外界而言数据空间就 是单独而统一的。乘-累加(Multiply-Accumulate,MAC) 类双源操作数 DSP 指令,通过 X 和 Y 的 AGU 进行操 作,这将数据地址空间分成两个部分 (见第 3.2 节 “数 据地址空间”)。X 和 Y 数据空间边界视具体器件而定, 用户不能改变它们。每个数据字由 2 个字节组成,大多 数指令按字或字节对数据进行寻址。 对于存储在程序存储器中的数据,有两种访问方法: • 数据存储空间的高 32 KB 可以映射到程序空间的下 半部分 (用户空间),映射的边界可以是任何 16K 程序字边界,边界由 8 位程序空间可视性页 (Program Space Visibility Page, PSVPAG)寄存 器定义。这使得任何指令都能像访问数据空间那样 访问程序空间,但访问需要一个额外的周期。此 外,使用这个方法,只能访问每个指令字的低 16 位。 • 使用任何工作寄存器,通过表读和表写指令,也可 以对程序空间内的 32K 字页进行线性间接访问。 表读和表写指令能够用来访问一个指令字的全部 24 位。 X 和 Y 地址空间都支持无开销循环缓冲区 (模寻址)。 模寻址的主要目的是要消除 DSP 算法的循环开销。 X AGU 还支持对目标有效地址进行位反转寻址,对于 基 2 FFT 算法,这极大地简化了输入或输出数据的重 新排序。有关模寻址和位反转寻址的详细信息,请参见 第 4.0 节 “地址发生器单元”。 内核支持固有(无操作数)寻址、相对寻址、立即数寻 址、存储器直接寻址、寄存器直接寻址、寄存器间接寻 址、寄存器偏移量寻址和立即数偏移量寻址模式。指令 与预定义的寻址模式相关联,这取决于其功能需求。 对于大多数指令,内核能够在每个指令周期内执行一次 数据(或程序数据)存储器读取、一次工作寄存器(数 据)读取、一次数据存储器写入以及一次程序 (指令) 存储器读取操作。因此,支持 3 操作数指令,允许在单 个周期内执行 C = A + B 这样的操作。 内核包含 DSP 引擎,这极大地提高了内核的运算能力 和吞吐量。它具有一个高速 17 位 x 17 位乘法器、一个 40 位 ALU、两个 40 位饱和累加器和一个 40 位双向桶 形移位寄存器。累加器或任何工作寄存器中的数据可以 在单个周期内右移 16 位或左移 16 位。 DSP 指令可以 无缝地与所有其他指令一起操作,且设计为能获得最佳 实时性能。MAC 类指令能够在从存储器取出两个数据操 作数的同时,将两个 W 寄存器相乘。为了能够同时取两 个数据操作数,对于 MAC 类指令,数据空间拆分为两 块,对所有其他指令数据空间则是线性的。对于 MAC 类 指令,这是通过将某些工作寄存器专用于每个地址空 间,以透明而灵活的方式实现的。 内核不支持多级指令流水线。不过,为了最大限度地获 得可用的执行时间,使用了单级指令预取机制,在指令 执行的前一个周期取指令并部分译码指令。除了一些特 例外,大部分指令都在单个周期内执行。 内核具有用于陷阱和中断的向量异常处理结构,具有62 个独立的向量。异常包括最多 8 个陷阱(其中有 4 个是 保留的)和 54 个中断。根据用户指定的 1 到 7 之间的 优先级 (1 为最低优先级, 7 为最高优先级),以及预 定义的 “自然顺序”,决定每个中断的优先级。陷阱的 优先级是固定的,其范围从 8 到 15。 注:本数据手册总结了 dsPIC30F 系列器件的功能,但是不 应把本手册当作无所不包的参考手册来使用。有关 CPU、外 设、寄存器说明和一般器件功能的更多信息,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件 指令集和编程的更多信息,请参见 《dsPIC30F/33F 程序 员参考手册》(DS70157B_CN)

dsP1C30F401114012 2.2 编程模型 2.2.1 软件堆栈指针/帧指针 编程模型如图2-1所示,它包括16个16位工作寄存器 dsPI1C数字信号控制器具有一个软件堆栈。W15是专用 (W0至W15)、2个40位累加器(ACCA和ACCB)、状 的软件堆栈指针(Stack Pointer,SP),异常处理、子 态寄存器(SR)、数据表页寄存器(TBLPAG)、程序 程序调用与返回时会自动修改W15。但是,W15可以 空间可视性页寄存器(PSVPAG)、DO和REPEAT寄 被任何指令所引用,引用方式与引用所有其他W寄存器 存器(DOSTART、DOEND、DCOUNT和RCOUNT) 相同。这简化了堆栈指针的读、写和操作(例如,创建 以及程序计数器(PC)。工作寄存器可作为数据、地 堆栈帧)。 或偏移量寄存器。所有寄存器都是存储器映射的。WO 注 为了防止出现不对齐的堆栈访问, 用作进行文件寄存器寻址的W寄存器。 W15<0>始终清零。 这些寄存器中,一些寄存器有与之相关的影子寄存器, 复位时W15初始化为0x0800。在初始化过程中,用户 如图21所示。影子寄存器用作临时保持寄存器,事件 可以重新设定SP,使它指向数据空间内的任何存储单 发生时可在影子寄存器和主寄存器之间传递内容。所有 元。 影子寄存器均不能直接访问。寄存器与其影子寄存器之 间的数据传递遵循以下规则: W14是专用的堆栈帧指针,由LNK和ULNK指令定义。 但是,W14可以被任何指令所引用,引用方式与引用所 ·PUSH.S和OP.S 有其他W寄存器相同。 WO、W1、W2、W3和SR(仅限DC、N、OV、 Z和C位)与对应的影子寄存器之间进行内容传 2.2.2 状态寄存器 递。 dsPIC DSC内核有一个16位状态寄存器(SR),其最 ·D0指令 低有效字节称为SR低字节(SR Low Byte,SRL),其 循环开始时,DOSTART、DOEND和DCOUNT 最高有效字节称为SR高字节(SR High Byte,SRH)。 寄存器的内容压入影子寄存器,在循环结束时其内 容从各自的影子寄存器中弹出。 SR寄存器组成见图2-1。 SRL包含所有的DSP ALU运算状态标志位(包括Z 对工作寄存器进行字节操作时,只影响目标寄存器的低 位),以及CPU中断优先级状态位IPL<2:O>和REPEAT 字节(Least Significant Byte,LSB)。不过,存储器映 有效状态位RA。在异常处理期间,SRL与PC的MSB 射工作寄存器的一个好处是,可以通过字节宽数据存储 连接起来形成一个完整的字值,然后将该字值压入堆 空间访问来操作低字节和高字节(Most Significant 栈。 Byte,MSB)。 SR寄存器的高字节包含DSP加法器I减法器状态位、 DO循环有效位(DA)和半进位(DC)状态位。 2.2.3 程序计数器 程序计数器为23位宽,bt0始终清零:因此,P℃能够 寻址最多4M指令字。 DS70135ECN第14页 @2007 Microchip Technology Inc

dsPIC30F4011/4012 DS70135E_CN 第 14 页 2007 Microchip Technology Inc. 2.2 编程模型 编程模型如图 2-1 所示,它包括 16 个 16 位工作寄存器 (W0至W15)、2个40位累加器(ACCA和ACCB)、状 态寄存器 (SR)、数据表页寄存器 (TBLPAG)、程序 空间可视性页寄存器(PSVPAG)、DO 和 REPEAT 寄 存器(DOSTART、DOEND、DCOUNT 和 RCOUNT) 以及程序计数器(PC)。工作寄存器可作为数据、地址 或偏移量寄存器。所有寄存器都是存储器映射的。 W0 用作进行文件寄存器寻址的 W 寄存器。 这些寄存器中,一些寄存器有与之相关的影子寄存器, 如图 2-1 所示。影子寄存器用作临时保持寄存器,事件 发生时可在影子寄存器和主寄存器之间传递内容。所有 影子寄存器均不能直接访问。寄存器与其影子寄存器之 间的数据传递遵循以下规则: • PUSH.S 和 POP.S W0、W1、W2、W3 和 SR(仅限 DC、N、OV、 Z 和 C 位)与对应的影子寄存器之间进行内容传 递。 • DO 指令 循环开始时, DOSTART、 DOEND 和 DCOUNT 寄存器的内容压入影子寄存器,在循环结束时其内 容从各自的影子寄存器中弹出。 对工作寄存器进行字节操作时,只影响目标寄存器的低 字节(Least Significant Byte,LSB)。不过,存储器映 射工作寄存器的一个好处是,可以通过字节宽数据存储 空间访问来操作低字节和高字节(Most Significant Byte, MSB)。 2.2.1 软件堆栈指针 / 帧指针 dsPIC®数字信号控制器具有一个软件堆栈。W15是专用 的软件堆栈指针(Stack Pointer,SP),异常处理、子 程序调用与返回时会自动修改 W15。但是, W15 可以 被任何指令所引用,引用方式与引用所有其他W寄存器 相同。这简化了堆栈指针的读、写和操作(例如,创建 堆栈帧)。 复位时 W15 初始化为 0x0800。在初始化过程中,用户 可以重新设定 SP,使它指向数据空间内的任何存储单 元。 W14 是专用的堆栈帧指针,由 LNK 和 ULNK 指令定义。 但是,W14 可以被任何指令所引用,引用方式与引用所 有其他 W 寄存器相同。 2.2.2 状态寄存器 dsPIC DSC 内核有一个 16 位状态寄存器 (SR),其最 低有效字节称为 SR 低字节(SR Low Byte,SRL),其 最高有效字节称为 SR 高字节(SR High Byte,SRH)。 SR 寄存器组成见图 2-1。 SRL 包含所有的 DSP ALU 运算状态标志位 (包括 Z 位),以及CPU中断优先级状态位IPL<2:0>和REPEAT 有效状态位 RA。在异常处理期间,SRL 与 PC 的 MSB 连接起来形成一个完整的字值,然后将该字值压入堆 栈。 SR 寄存器的高字节包含 DSP 加法器 / 减法器状态位、 DO 循环有效位 (DA)和半进位 (DC)状态位。 2.2.3 程序计数器 程序计数器为 23 位宽,bit 0 始终清零;因此,PC 能够 寻址最多 4M 指令字。 注: 为 了 防 止 出 现 不 对 齐 的 堆 栈 访 问, W15<0> 始终清零