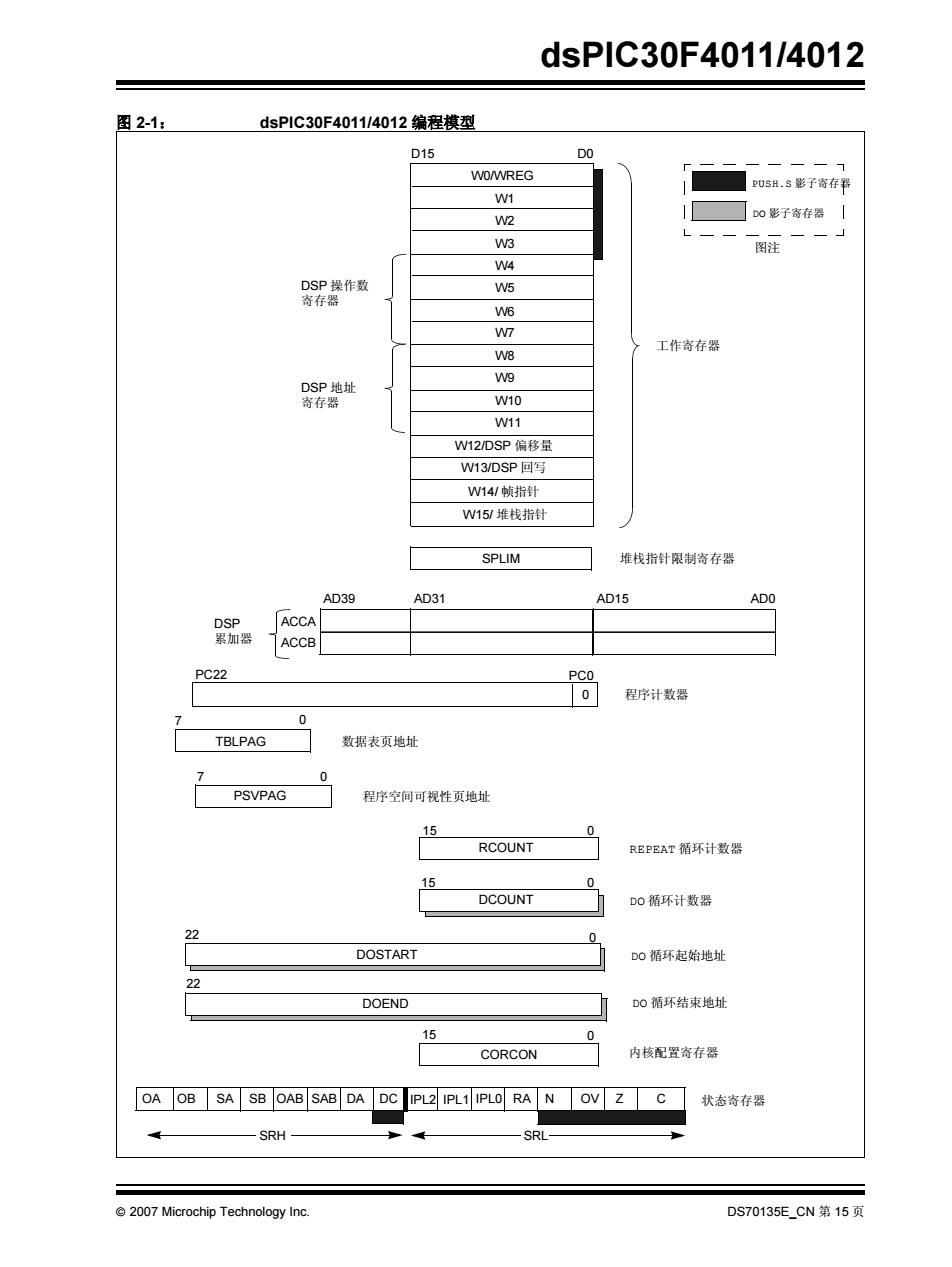

dsPIC30F4011/4012 图2-1: dsPIC30F4011/4012编程模型 D15 DO WO/WREG PUsH.s影子寄存释 W1 W2 DO影子寄存器I L一 W3 图注 W4 DSP操作数 W5 寄存器 W6 W7 工作寄存器 W8 DSP地址 W9 寄存器 W10 W11 W12/DSP偏移量 W13/DSP回写 W14/帧指针 W15/堆栈指针 SPLIM 堆栈指针限制寄存器 AD39 AD31 AD15 ADO DSP ACCA 累加器 ACCB PC22 PCO 0 程序计数器 7 0 TBLPAG 数据表页地址 0 PSVPAG 程序空间可视性页地址 15 0 RCOUNT REPEAT循环计数器 DCOUNT Do循环计数器 22 DOSTART D0循环起始地址 22 DOEND D0循环结束地址 15 CORCON 内核配置寄存器 OA OB SA SB OAB SAB DA DC IPL2 IPL1IPLO RA NOV Z C 状态寄存器 SRH SRL 2007 Microchip Technology Inc. DS70135ECN第15页

2007 Microchip Technology Inc. DS70135E_CN 第 15 页 dsPIC30F4011/4012 图 2-1: dsPIC30F4011/4012 编程模型 TABPAG PC22 PC0 7 0 D15 D0 程序计数器 数据表页地址 状态寄存器 工作寄存器 DSP 操作数 寄存器 W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12/DSP 偏移量 W13/DSP 回写 W14/ 帧指针 W15/ 堆栈指针 DSP 地址 寄存器 AD39 AD0 AD31 DSP 累加器 ACCA ACCB PSVPAG 7 0 程序空间可视性页地址 Z 0 OA OB SA SB RCOUNT 15 0 REPEAT 循环计数器 DCOUNT 15 0 DO 循环计数器 DOSTART 22 0 DO 循环起始地址 IPL2 IPL1 SPLIM 堆栈指针限制寄存器 AD15 SRL PUSH.S 影子寄存器 DO 影子寄存器 OAB SAB 15 0 内核配置寄存器 图注 CORCON DA DC RA N TBLPAG PSVPAG IPL0 OV W0/WREG SRH DOEND DO 循环结束地址 22 C

dsPIC30F4011/4012 2.3除法支持 除法指令必须在一个REPEAT循环内执行。任何其他执 行方式(例如,一系列不连续的除法指令),将不会正 dsP1CDSC具有这样的特性支持16/16位有符号小数 常运行,因为指令流取决于RCOUNT。除法指令不会自 除法运算,以及32/16位、16/16位有符号和无符号整 动设置RCOUNT值,于是RCOUNT必须显式地、正确 数除法运算,除法形式均为单指令迭代除法。支持以下 地在REPEAT指令中指定,如表2-1所示(REPEAT将 指令和数据长度: 执行目标指令{操作数的值+1}次)。DIV/DIVF指令 1.DIVE—16/16有符号小数除法 的REPEAT循环计数必须设置为18次迭代。所以,完整 2.DIV.sd- 一3216有符号除法 的除法操作需要19个周期。 3.DIV.ud—32/16无符号除法 注: 除法流可以被中断。但是,用户需要恰当地 4.DIV.s一16/16有符号除法 保存中断现场。 5.DIV.u—16/16无符号除法 表2-1: 除法指令 指令 功能 DIVF 有符号小数除法:WmWh→WO:Rem→W1 DIV.sd 有符号除法:Wm+1:Wm)Wh→W0:Rem→W1 DIV.s 有符号除法:WmWn→W0:Rem→W1 DIV.ud 无符号除法:Wm+1:Wm)Wn→W0:Rem→W1 DIV.u 无符号除法:WmWn→W0:Rem→WI 2.4 DSP引擎 DSP引擎的框图如图2-2所示. DSP引擎由一个高速17位x17位乘法器、一个桶形移 表2-2: DSP指令汇总 位寄存器和一个40位加法器/减法器(两个目标累加 指令 代数运算 器、舍入逻辑和饱和逻辑)组成。 CLR A=0 dsPIC30F器件采用单周期指令流,可以执行DSP指令 ED A=(X-y)2 或MCU指令。许多硬件资源可以被DSP和MCU指令 共用。例如,指令集具有DSP和MCU乘法指令,它们 EDAC A=A+(X-y)2 使用相同的硬件乘法器。 MAC A=A+(x*y) DSP引擎还能够执行固有的不需要其他数据的累加器- MOVSAC A中内容将不发生改变 累加器操作。这些指令是ADD、SUB和NEG。 MPY A=x*y 通过CPU内核配置寄存器(CORCON)中的各个位, MPY.N A=-x*y 可以选择DSP引擎的多种功能,功能如下: MSC A=A-x*y 1.小数或整数DSP乘法(IF)。 2.有符号或无符号DSP乘法(US)。 3.常规或收敛舍入(RND)。 4.ACCA自动饱和使能/禁止(SATA)。 5.ACCB自动饱和使能/禁止(SATB). 6. 对于写数据存储器,自动饱和使能/禁止(SATDW)。 7.累加器饱和模式选择(ACCSAT)。 注: CORCON的组成见表3-3. DS70135E_CN第16页 2007 Microchip Technology Inc

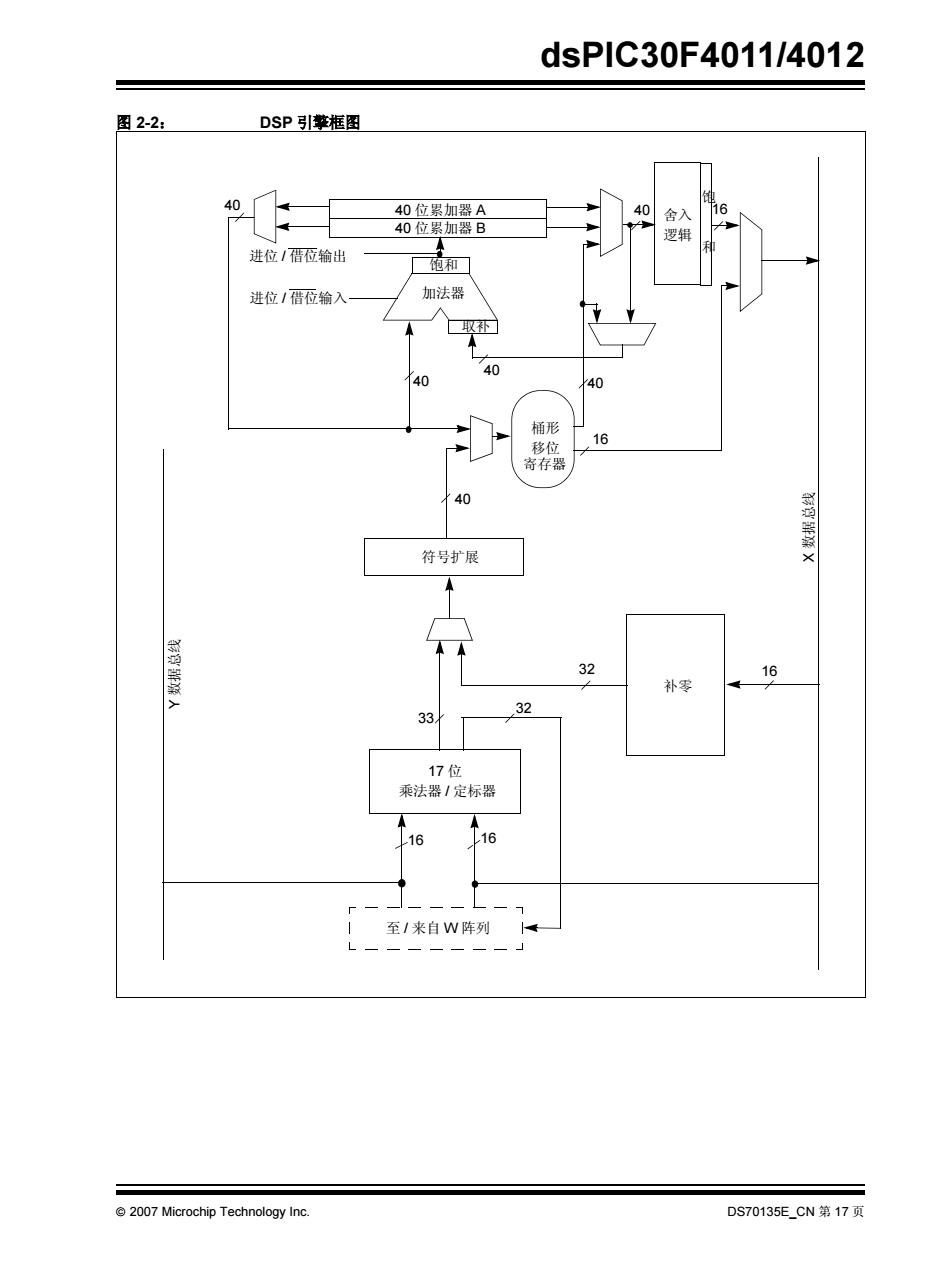

dsPIC30F4011/4012 DS70135E_CN 第 16 页 2007 Microchip Technology Inc. 2.3 除法支持 dsPIC DSC 具有这样的特性:支持 16/16 位有符号小数 除法运算,以及 32/16 位、 16/16 位有符号和无符号整 数除法运算,除法形式均为单指令迭代除法。支持以下 指令和数据长度: 1. DIVF——16/16 有符号小数除法 2. DIV.sd——32/16 有符号除法 3. DIV.ud——32/16 无符号除法 4. DIV.s——16/16 有符号除法 5. DIV.u——16/16 无符号除法 除法指令必须在一个 REPEAT 循环内执行。任何其他执 行方式 (例如,一系列不连续的除法指令),将不会正 常运行,因为指令流取决于 RCOUNT。除法指令不会自 动设置 RCOUNT 值,于是 RCOUNT 必须显式地、正确 地在 REPEAT 指令中指定,如表 2-1 所示 (REPEAT 将 执行目标指令 { 操作数的值 + 1} 次)。 DIV/DIVF 指令 的 REPEAT 循环计数必须设置为 18 次迭代。所以,完整 的除法操作需要 19 个周期。 表 2-1: 除法指令 2.4 DSP 引擎 DSP 引擎由一个高速 17 位 x 17 位乘法器、一个桶形移 位寄存器和一个 40 位加法器 / 减法器 (两个目标累加 器、舍入逻辑和饱和逻辑)组成。 dsPIC30F 器件采用单周期指令流,可以执行 DSP 指令 或 MCU 指令。许多硬件资源可以被 DSP 和 MCU 指令 共用。例如,指令集具有 DSP 和 MCU 乘法指令,它们 使用相同的硬件乘法器。 DSP 引擎还能够执行固有的不需要其他数据的累加器 - 累加器操作。这些指令是 ADD、 SUB 和 NEG。 通过 CPU 内核配置寄存器 (CORCON)中的各个位, 可以选择 DSP 引擎的多种功能,功能如下: 1. 小数或整数 DSP 乘法 (IF)。 2. 有符号或无符号 DSP 乘法 (US)。 3. 常规或收敛舍入 (RND)。 4. ACCA 自动饱和使能 / 禁止 (SATA)。 5. ACCB 自动饱和使能 / 禁止 (SATB)。 6. 对于写数据存储器,自动饱和使能/禁止(SATDW)。 7. 累加器饱和模式选择 (ACCSAT)。 DSP 引擎的框图如图 2-2 所示。 注: 除法流可以被中断。但是,用户需要恰当地 保存中断现场。 指令 功能 DIVF 有符号小数除法:Wm/Wn → W0 ; Rem → W1 DIV.sd 有符号除法:(Wm + 1:Wm)/Wn → W0 ; Rem → W1 DIV.s 有符号除法:Wm/Wn → W0 ; Rem → W1 DIV.ud 无符号除法:(Wm + 1:Wm)/Wn → W0 ; Rem → W1 DIV.u 无符号除法:Wm/Wn → W0 ; Rem → W1 注: CORCON 的组成见表 3-3。 表 2-2: DSP 指令汇总 指令 代数运算 CLR A = 0 ED A = (x – y)2 EDAC A = A + (x – y)2 MAC A = A + (x * y) MOVSAC A 中内容将不发生改变 MPY A = x * y MPY.N A = – x * y MSC A = A – x * y

dsPIC30F4011/4012 图2-2 DSP引莘框图 40 40位累加器A 40 舍入 16 40位累加器B 逻辑 进位/借位输出 饱和 进位/借位输入 加法器 取补 40 40 40 桶形 移位 16 寄存器 40 新迎入 符号扩展 胶纸入 32 16 补零 33 32 17位 乘法器/定标器 16 16 至/来自W阵列 L 2007 Microchip Technology Inc. DS70135ECN第17页

2007 Microchip Technology Inc. DS70135E_CN 第 17 页 dsPIC30F4011/4012 图 2-2: DSP 引擎框图 补零 符号扩展 桶形 移位 40 位累加器 A 40 位累加器 B 舍入 逻辑 X 数据总线 至 / 来自 W 阵列 加法器 饱和 取补 32 32 33 16 16 16 16 40 40 40 40 饱 和 Y 数据总线 40 进位 / 借位输出 进位 / 借位输入 16 40 乘法器 / 定标器 17 位 寄存器

dsPIC30F4011/4012 2.4.1 乘法器 2.4.2.1 加法器/减法器、溢出和饱和 17x17位乘法器可以进行有符号或无符号的运算,其输 加法器/减法器是一个40位加法器,一侧输入可以选择 出经过定标器进行换算后可支持1.31小数(Q31)或 为零,而另一侧输入可以是原数据或求补后的数据。对 32位整数结果。无符号操作数经过零扩展后,送入乘法 于加法,进位/借位输入为高电平有效,另一侧输入是 器输入值的第17位。有符号操作数经过符号扩展,送 原数据(没有求补的):对于减法,进位/借位输入为 入乘法器输入值的第17位。17x17位乘法器/定标器的 低电平有效,另一侧输入是求补后的数据。加法器/减 输出是33位值,它将被符号扩展为40位。整型数据的 法器产生溢出状态位SA/SB和OA/OB,这些状态位被 固有表示形式为有符号的二进制补码值,其中MSb定 锁存在状态寄存器中并在其中得到反映。 多兴:秀68 ·从bt39溢出:这是灾难性溢出,会破坏累加器的 符号位。 (0x8000)到32767(0x7FFF),包括0在内。对于 32位整数,数据范围为-2,147.483.648(0x80000000) ·溢出到警戒位(bt32到bit39):这是可恢复的溢 到2,147,483.645(0x7 FFF FFFF)。 出。每当警戒位彼此不完全一致时,就将把这个状 态位置1。 当乘法器配置为小数乘法时,数据表示为二进制补码小 数,其中MSb定义为符号位,小数点暗含在符号位之后 加法器有一个额外的饱和模块,如果选取的话,饱和模 (QX格式)。暗含小数点的N位二进制补码小数的范围 块将控制累加器的数据饱和。饱和模块使用加法器的结 为-1.0到(1-21-N)。对于16位小数,Q15数据范围为 果、上述的溢出状态位、SATA/B(CORCON<7:6>) -1.0(0x8000)到0.999969482(0x7FFF),包括0在 和ACCSAT(CORCON<4>)模式控制位,来确定何 内,其精度为3.01518x105。在小数模式下,16x16乘 时饱和、达到何值为饱和。 法运算将产生1.31乘积,其精度为4.65661x1010。 状态寄存器中有6个支持饱和和溢出的位,它们是: 同一个乘法器还用来支持DSC乘法指令,包括整数的 1.OA: 16位有符号、无符号和混合符号乘法。 ACCA溢出到警戒位 M如L指令可以使用字节或字长度的操作数。字节操作数 2.OB: 将产生16位结果,而字操作数将产生32位结果,结果 ACCB溢出到警戒位 存放在W寄存器阵列的指定寄存器中。 3. SA: ACCA已饱和(bit31溢出并饱和) 2.4.2 数据累加器和加法器/减法器 或 数据累加器包含一个40位加法器/减法器,它带有自 ACCA溢出到警戒位并饱和(bit39溢出并饱和) 动符号扩展逻辑。它可以选择两个累加器(A或B)之 4.SB: 一作为其累加前的源累加器和累加后的目标累加器。对 ACCB已饱和(bit31溢出并饱和) 于ADD和LAC指令,可选择通过桶形移位器在累加之 或 前将要累加或装入的数据进行换算。 ACCB溢出到警戒位并饱和(bt39溢出并饱和) 5.OAB: OA和OB的逻辑或(OR) 6.SAB: SA和SB的逻辑或(OR) 每次数据通过加法器/减法器,就会修改OA和OB位。 置1时,它们表明最近的操作已溢出到累加器警戒位 (bit32到bit39)。如果OA和OB位置1而且NTCON1 寄存器中相应的溢出陷阱标志使能位(OVATE和 OVBTE)置1的话,还可以选择用OA和OB位产生算 术警告陷阱(见第5.0节“中断”)。这使得用户能够 立即采取措施,例如,校正系统增益。 DS70135ECN第18页 2007 Microchip Technology Inc

dsPIC30F4011/4012 DS70135E_CN 第 18 页 2007 Microchip Technology Inc. 2.4.1 乘法器 17x17 位乘法器可以进行有符号或无符号的运算,其输 出经过定标器进行换算后可支持 1.31 小数 (Q31)或 32 位整数结果。无符号操作数经过零扩展后,送入乘法 器输入值的第 17 位。有符号操作数经过符号扩展,送 入乘法器输入值的第 17 位。17x17 位乘法器 / 定标器的 输出是 33 位值,它将被符号扩展为 40 位。整型数据的 固有表示形式为有符号的二进制补码值,其中 MSb 定 义为符号位。一般来说,N 位二进制补码整数的范围为 -2N-1 到 2N-1 – 1。对于 16 位整数,数据范围为 -32768 (0x8000)到 32767 (0x7FFF),包括 0 在内。对于 32位整数,数据范围为-2,147,483,648(0x8000 0000) 到 2,147,483,645 (0x7FFF FFFF)。 当乘法器配置为小数乘法时,数据表示为二进制补码小 数,其中 MSb 定义为符号位,小数点暗含在符号位之后 (QX格式)。暗含小数点的 N 位二进制补码小数的范围 为 -1.0 到(1-21-N)。对于 16 位小数,Q15 数据范围为 -1.0(0x8000)到 0.999969482(0x7FFF),包括 0 在 内,其精度为 3.01518x10-5。在小数模式下, 16x16 乘 法运算将产生 1.31 乘积,其精度为 4.65661x10-10。 同一个乘法器还用来支持 DSC 乘法指令,包括整数的 16 位有符号、无符号和混合符号乘法。 MUL 指令可以使用字节或字长度的操作数。字节操作数 将产生 16 位结果,而字操作数将产生 32 位结果,结果 存放在 W 寄存器阵列的指定寄存器中。 2.4.2 数据累加器和加法器 / 减法器 数据累加器包含一个 40 位加法器 /减法器,它带有自 动符号扩展逻辑。它可以选择两个累加器(A 或 B)之 一作为其累加前的源累加器和累加后的目标累加器。对 于 ADD 和 LAC 指令,可选择通过桶形移位器在累加之 前将要累加或装入的数据进行换算。 2.4.2.1 加法器 / 减法器、溢出和饱和 加法器 / 减法器是一个 40 位加法器,一侧输入可以选择 为零,而另一侧输入可以是原数据或求补后的数据。对 于加法,进位 / 借位输入为高电平有效,另一侧输入是 原数据 (没有求补的);对于减法,进位 / 借位输入为 低电平有效,另一侧输入是求补后的数据。加法器 / 减 法器产生溢出状态位 SA/SB 和 OA/OB,这些状态位被 锁存在状态寄存器中并在其中得到反映。 • 从 bit 39 溢出:这是灾难性溢出,会破坏累加器的 符号位。 • 溢出到警戒位 (bit 32 到 bit 39):这是可恢复的溢 出。每当警戒位彼此不完全一致时,就将把这个状 态位置 1。 加法器有一个额外的饱和模块,如果选取的话,饱和模 块将控制累加器的数据饱和。饱和模块使用加法器的结 果、上述的溢出状态位、 SATA/B (CORCON<7:6>) 和 ACCSAT (CORCON<4>)模式控制位,来确定何 时饱和、达到何值为饱和。 状态寄存器中有 6 个支持饱和和溢出的位,它们是 : 1. OA: ACCA 溢出到警戒位 2. OB: ACCB 溢出到警戒位 3. SA: ACCA 已饱和 (bit 31 溢出并饱和) 或 ACCA 溢出到警戒位并饱和(bit 39 溢出并饱和) 4. SB: ACCB 已饱和 (bit 31 溢出并饱和) 或 ACCB 溢出到警戒位并饱和(bit 39 溢出并饱和) 5. OAB: OA 和 OB 的逻辑或 (OR) 6. SAB: SA 和 SB 的逻辑或 (OR) 每次数据通过加法器 / 减法器,就会修改 OA 和 OB 位。 置 1 时,它们表明最近的操作已溢出到累加器警戒位 (bit 32到bit 39)。如果OA和OB位置1而且INTCON1 寄存器中相应的溢出陷阱标志使能位(OVATE 和 OVBTE)置 1 的话,还可以选择用 OA 和 OB 位产生算 术警告陷阱 (见第 5.0 节 “中断”)。这使得用户能够 立即采取措施,例如,校正系统增益

dsP1C30F4011/4012 每次数据通过加法器/减法器,就会修改SA和SB位, 2.4.2.2 累加器“回写” 但用户只能对它们进行清零。置1时,它们表明累加器 已溢出其最大范围(对于32位饱和是bit31,而40位 MAC类指令(MPY、MPY.N、ED和EDAC除外)可以选 择将累加器高位字(bit16到bit31)的舍入形式写入 饱和是bt39),将发生饱和(如果饱和使能的话)。如 数据存储空间,前提是当前指令不对该累加器进行操 果没有使能饱和,SA和SB置1默认为bit39滋出,以 此指示产生了灾难性溢出。如果NTCON1寄存器中的 作。通过X总线寻址组合的X和Y地址空间,执行回写 COVTE位置1,当饱和被禁止时,SA和SB位将产生算 操作。支持以下寻址模式: 术警告陷阱。 1. W13,寄存器直接寻址: 在状态寄存器(S尔)中,对于溢出和饱和状态位,可 非操作日标的累加器的舍入内容以1.15小数形 以将OA和OB的逻辑或形成OAB位,将SA和SB的 式写入W13。 逻辑或形成SAB位。这样,只需检查状态寄存器中的一 2. W13]+=2,执行后递增的寄存器间接寻址: 个位,程序员就能判断是否有累加器溢出:检查状态寄 非操作目标的累加器的舍入内容以1.15小数形式 存器中的另一个位,就可以判断是否有累加器饱和。对 写入W13指向的地址。然后W13递增2(对于 于通常要使用两个累加器的复数运算而言,这很有用。 字写入)。 器件支持三种饱和和溢出模式: 2.4.2.3 舍入逻辑 1.bit39溢出和饱和: 舍入逻辑是一个组合模块,在累加器写(存储)过程中 当发生bit39溢出和饱和时,饱和逻辑将最大的 执行常规的(有偏)或收敛的(无偏)舍入功能。舍入 正9.31值(0x7 FFFFFFFFF)或最大的负9.31 模式由CORCON寄存器中RND位的状态决定。它会产 值(0x8000000000)装入目标累加器。SA或 生一个16位的1.15数据值,该值被送到数据空间写饱 SB位置1并保持直到被用户清零。这称为“超 和逻辑。如果指令不指明舍入,就会存储一个截取的 饱和”,为错误数据或不可预期的算法问题(例 1.15数据值,简单地丢弃低位字。 如,增益计算)提供了保护机制。 常规舍入取累加器的bit15,对它进行零扩展并将扩展 2. bit31溢出和饱和: 后的值加到ACCxH字(累加器的bit16到bit31)。如 当发生bt31溢出和饱和时,饱和逻辑将最大的 果ACCxL字(累加器的bit0到bit15).在0x8000和 正1.31值(0x007 FFFFFFF)或最大的负1.31 0 xFFFF之间(包括0x8000),则ACCxH递增1。如 值(0x0080000000)装入目标累加器。SA或 果ACCxL在0x0000和0x7FFF之间,则ACCxH不 SB位置1并保持直到被用户清零。当这种饱和模 变。此算法的结果经过一系列随机舍入操作,值会稍稍 式生效时,不使用警戒位(因此OA、OB或OAB 偏大(正偏)。 位不会被置1)。 3.bit39灾难性溢出 除非ACCxL等于0x8000,否则收敛的(或无偏)舍入 加法器的bit39溢出状态位用来将SA或SB位 操作方式与常规舍入相同。ACCxL等于0x8000时,要 置1:这两位置1后,将保持该状态直到被用户 对ACCxH的LSb(累加器的bit16)进行检测。如果 清零。不进行饱和操作,允许累加器溢出(破坏 它为1,ACCxH递增1。如果它为0,ACCxH不变. 其符号位)。如果INTCON1寄存器中的COVTE 假设bt16本身是随机的,这样的机制将消除任何可能 位置1,灾难性溢出会导致一个陷阱异常。 累加的舍入偏差。 通过X总线,SAC和SAC.R指令将目标累加器内容的 截取(SAC)或舍入(SAC.R)形式存入数据存储空间 (这受数据饱和的影响,请参见第2.4.2.4节“数据空 间写饱和”)。注意,对于MAC类指令,累加器回写操 作将以同样的方式进行,通过X总线寻址组合的DSC (X和Y)数据空间。对于此类指令,数据始终要进行 舍入。 @2007 Microchip Technology Inc. DS70135ECN第19页

2007 Microchip Technology Inc. DS70135E_CN 第 19 页 dsPIC30F4011/4012 每次数据通过加法器 / 减法器,就会修改 SA 和 SB 位, 但用户只能对它们进行清零。置 1 时,它们表明累加器 已溢出其最大范围 (对于 32 位饱和是 bit 31,而 40 位 饱和是 bit 39),将发生饱和(如果饱和使能的话)。如 果没有使能饱和,SA 和 SB 置 1 默认为 bit 39 溢出,以 此指示产生了灾难性溢出。如果 INTCON1 寄存器中的 COVTE 位置 1,当饱和被禁止时,SA 和 SB 位将产生算 术警告陷阱。 在状态寄存器 (SR)中,对于溢出和饱和状态位,可 以将 OA 和 OB 的逻辑或形成 OAB 位,将 SA 和 SB 的 逻辑或形成 SAB 位。这样,只需检查状态寄存器中的一 个位,程序员就能判断是否有累加器溢出;检查状态寄 存器中的另一个位,就可以判断是否有累加器饱和。对 于通常要使用两个累加器的复数运算而言,这很有用。 器件支持三种饱和和溢出模式: 1. bit 39 溢出和饱和: 当发生 bit 39 溢出和饱和时,饱和逻辑将最大的 正 9.31 值 (0x7FFFFFFFFF)或最大的负 9.31 值 (0x8000000000)装入目标累加器。 SA 或 SB 位置 1 并保持直到被用户清零。这称为 “超 饱和”,为错误数据或不可预期的算法问题 (例 如,增益计算)提供了保护机制。 2. bit 31 溢出和饱和: 当发生 bit 31 溢出和饱和时,饱和逻辑将最大的 正 1.31 值 (0x007FFFFFFF)或最大的负 1.31 值 (0x0080000000)装入目标累加器。 SA 或 SB 位置 1 并保持直到被用户清零。当这种饱和模 式生效时,不使用警戒位(因此 OA、OB 或 OAB 位不会被置 1)。 3. bit 39 灾难性溢出 加法器的 bit 39 溢出状态位用来将 SA 或 SB 位 置 1 ;这两位置 1 后,将保持该状态直到被用户 清零。不进行饱和操作,允许累加器溢出(破坏 其符号位)。如果 INTCON1 寄存器中的 COVTE 位置 1,灾难性溢出会导致一个陷阱异常。 2.4.2.2 累加器 “回写” MAC 类指令(MPY、MPY.N、ED 和 EDAC 除外)可以选 择将累加器高位字 (bit 16 到 bit 31)的舍入形式写入 数据存储空间,前提是当前指令不对该累加器进行操 作。通过 X 总线寻址组合的 X 和 Y 地址空间,执行回写 操作。支持以下寻址模式: 1. W13,寄存器直接寻址: 非操作目标的累加器的舍入内容以 1.15 小数形 式写入 W13。 2. [W13]+=2,执行后递增的寄存器间接寻址: 非操作目标的累加器的舍入内容以1.15小数形式 写入 W13 指向的地址。然后 W13 递增 2(对于 字写入)。 2.4.2.3 舍入逻辑 舍入逻辑是一个组合模块,在累加器写 (存储)过程中 执行常规的(有偏)或收敛的(无偏)舍入功能。舍入 模式由 CORCON 寄存器中 RND 位的状态决定。它会产 生一个 16 位的 1.15 数据值,该值被送到数据空间写饱 和逻辑。如果指令不指明舍入,就会存储一个截取的 1.15 数据值,简单地丢弃低位字。 常规舍入取累加器的 bit 15,对它进行零扩展并将扩展 后的值加到 ACCxH 字(累加器的 bit 16 到 bit 31)。如 果 ACCxL 字 (累加器的 bit0 到 bit 15)在 0x8000 和 0xFFFF 之间 (包括 0x8000),则 ACCxH 递增 1。如 果 ACCxL 在 0x0000 和 0x7FFF 之间,则 ACCxH 不 变。此算法的结果经过一系列随机舍入操作,值会稍稍 偏大 (正偏)。 除非 ACCxL 等于 0x8000,否则收敛的(或无偏)舍入 操作方式与常规舍入相同。ACCxL 等于 0x8000 时,要 对 ACCxH 的 LSb (累加器的 bit 16)进行检测。如果 它为 1, ACCxH 递增 1。如果它为 0, ACCxH 不变。 假设 bit 16 本身是随机的,这样的机制将消除任何可能 累加的舍入偏差。 通过 X 总线, SAC 和 SAC.R 指令将目标累加器内容的 截取(SAC)或舍入(SAC.R)形式存入数据存储空间 (这受数据饱和的影响,请参见第 2.4.2.4 节 “数据空 间写饱和”)。注意,对于 MAC 类指令,累加器回写操 作将以同样的方式进行,通过 X 总线寻址组合的 DSC (X 和 Y)数据空间。对于此类指令,数据始终要进行 舍入