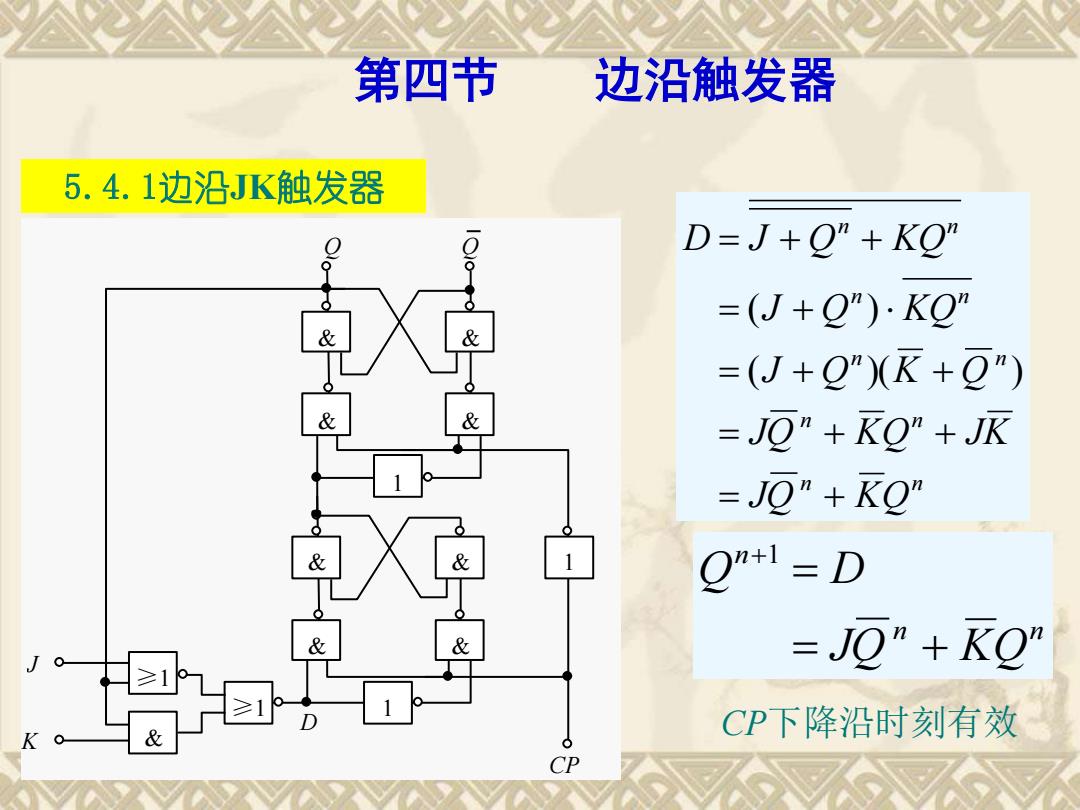

第四节 边沿触发器 5.4.1边沿JK触发器 D=J+Q”+KQ” =(J+Q”)·KQ” =(J+Q"”K+夏") =JQ”+KQ”+J瓜 =J0”+KQ On+1=D =J0"+KQ' CP下降沿时刻有效 K

5.4.1边沿JK触发器 D CP & & Q Q 1 & & & 1 1 ≥1 ≥1 J K & & & & n n n n n n n n n n JQ KQ JQ KQ JK J Q K Q J Q KQ D J Q KQ = + = + + = + + = + = + + ( )( ) ( ) n n n JQ KQ Q D = + = +1 CP下降沿时刻有效 第四节 边沿触发器

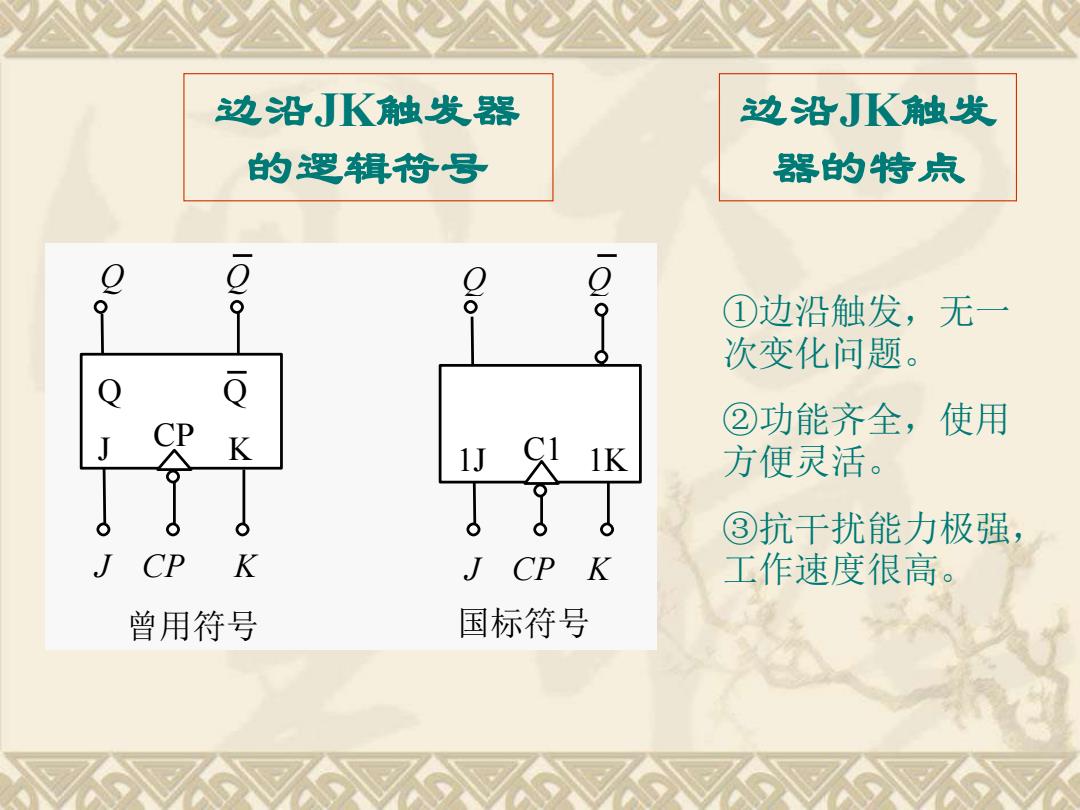

边沿JK触发器 边沿JK触发 的逻辑符号 器的特点 ①边沿触发,无一 次变化问题。 ②功能齐全,使用 K 1】 1K 方便灵活。 ③抗干扰能力极强, CP K J CP K 工作速度很高。 曾用符号 国标符号

J CP K Q Q J K Q Q 曾用符号 J CP K 1J 1K Q Q 国标符号 CP C1 边沿JK触发器 的逻辑符号 边沿JK触发 器的特点 ①边沿触发,无一 次变化问题。 ②功能齐全,使用 方便灵活。 ③抗干扰能力极强, 工作速度很高

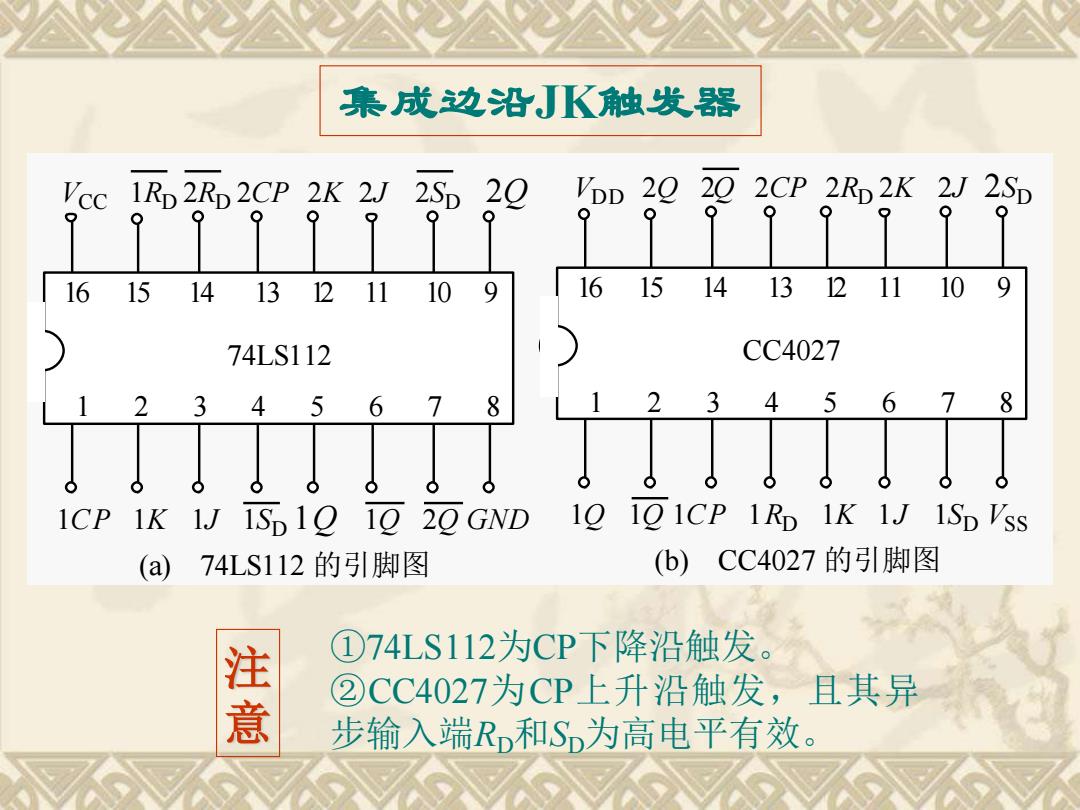

集成边沿JK触发器 Vcc 1Rp 2Rp2CP 2K 2J 2Sp 20 )bD2Q2g 2CP 2Rp 2K 2J 2Sp ]● 161514 131211109 1615 14 131211 109 74LS112 CC4027 2 345 6 8 1234567 8 ICP 1K 1J 1Sp 10 10 20 GND 1Q 10 1CP 1Rp 1K 1J 1Sp Vss (a) 74LS112的引脚图 (b) CC4027的引脚图 注 ①74LS112为CP下降沿触发 ②CC4027为CP上升沿触发,且其异 步输入端RD和SD为高电平有效

集成边沿JK触发器 (a) 74LS112 的引脚图 16 15 14 13 12 11 10 9 74LS112 1 2 3 4 5 6 7 8 VCC 1RD 2RD 2CP 2K 2J 2S D 2Q 1C P 1K 1J 1S D 1Q 1Q 2Q GND (b) CC4027 的引脚图 16 15 14 13 12 11 10 9 CC4027 1 2 3 4 5 6 7 8 VD D 2Q 2Q 2CP 2RD 2K 2J 2S D 1Q 1Q 1C P 1RD 1K 1J 1S D VSS ①74LS112为CP下降沿触发。 ②CC4027为CP上升沿触发,且其异 步输入端RD和SD为高电平有效。 注 意

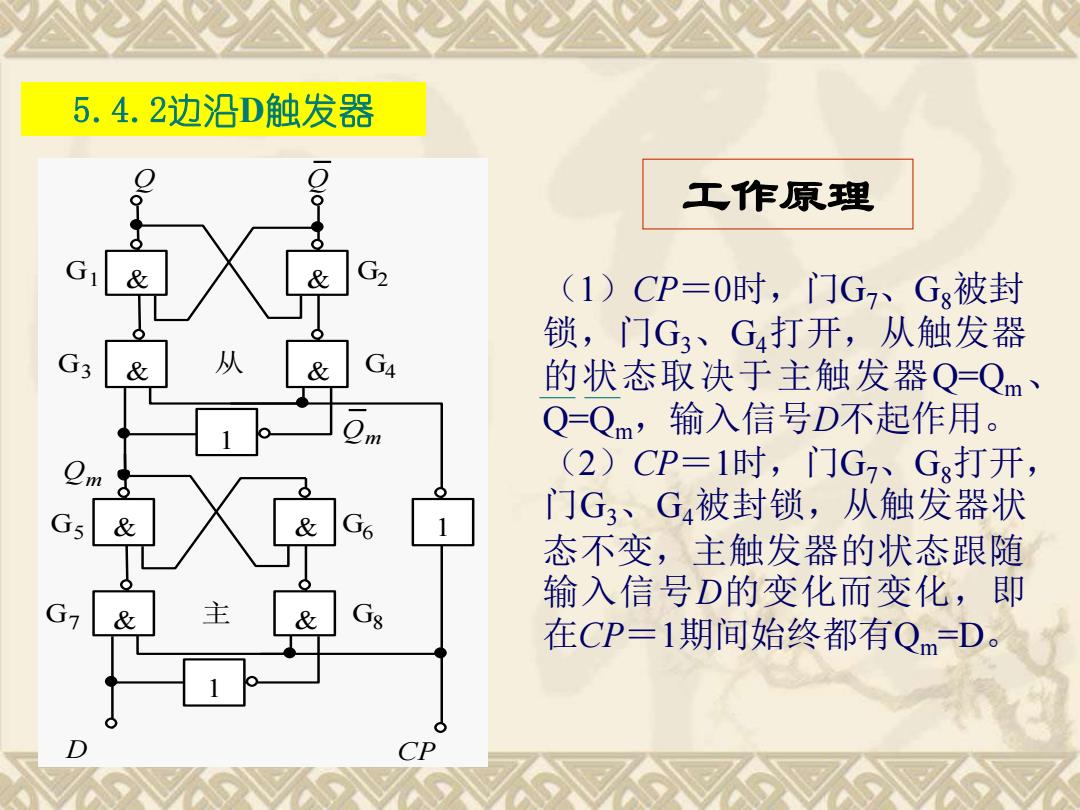

5.4.2边沿D触发器 工作原理 (1)CP=0时,门G、G被封 锁,门G3、G4打开,从触发器 & GA 的状态取决于主触发器Q=Qm、 Q=Qm,输入信号D不起作用。 m (2)CP=1时,门G、G3打开, 门G3、G4被封锁,从触发器状 态不变,主触发器的状态跟随 输入信号D的变化而变化,即 & G& 在CP=1期间始终都有Qm=D

5.4.2边沿D触发器 工作原理 G5 G6 G1 G2 CP G3 从 G & 4 Q Q 1 G7 主 G8 & & 1 D 1 Qm Qm & & & & & (1)CP=0时,门G7、G8被封 锁,门G3、G4打开,从触发器 的状态取决于主触发器Q=Qm、 Q=Qm,输入信号D不起作用。 (2)CP=1时,门G7、G8打开, 门G3、G4被封锁,从触发器状 态不变,主触发器的状态跟随 输入信号D的变化而变化,即 在CP=1期间始终都有Qm=D

(3)CP下降沿到来时, 封锁门 G7、Gg,打开门G3、G4,主触 Q 发器锁存CP下降时刻D的值,即 Qm=D,随后将该值送入从触发 器,使Q=D、Q=D。 & & GA (4)CP下降沿过后,主触发器 锁存的CP下降沿时刻D的值被保 m 存下来,而从触发器的状态也将 保持不变。 综上所述,边沿D触发器的特性 & 方程为: n+l G7 & & 下降沿时刻有效 边沿D触发器没有一次变化问题

G5 G6 G1 G2 CP G3 从 G & 4 Q Q 1 G7 主 G8 & & 1 D 1 Qm Qm & & & & & Q D n = +1 下降沿时刻有效 (3)CP下降沿到来时,封锁门 G7、G8,打开门G3、G4,主触 发器锁存CP下降时刻D的值,即 Qm=D,随后将该值送入从触发 器,使Q=D、Q=D。 (4)CP下降沿过后,主触发器 锁存的CP下降沿时刻D的值被保 存下来,而从触发器的状态也将 保持不变。 综上所述,边沿D触发器的特性 方程为: 边沿D触发器没有一次变化问题