逻辑符号 9 Q CP D CP D CP 曾用符号 国标符号

D CP Q Q D Q Q 曾用符号 D CP 1D Q Q 国标符号 CP C1 逻辑符号

维特阻塞触发器(D触发器 1.工作原理 CP=0时 触发器保持。且有: S-D R上D CP上升沿时 电路按RSFF动作。注意到上式, 因此有Qn+=D 研究一下CP上升沿到来后的清况,以 判断它是不是边沿触发器: (1)若原来D=0,则G4,使得D变为1无影响; (2)若原来D=1,则G4=1,但G3=0,使得改变仍无影响; 说明它是CP上沿翻转的边沿触发署。 将2号线称置1阻塞线、置0娃持线: 将1号线称为置1维持线、3号线称为置0阻塞线;

维持阻塞触发器(D触发器) 1.工作原理 CP=0时 触发器保持。且有: CP上升沿时 电路按RSFF动作。注意到上式, 因此有 Qn+1=D 研究一下CP上升沿到来后的情况,以 判断它是不是边沿触发器: (1)若原来 D=0,则G4=0,使得D变为1无影响; (2)若原来 D=1,则G4=1,但G3=0,使得D改变仍无影响; 将2号线称为置1阻塞线、置0维持线; 将1号线称为置1维持线、3号线称为置0阻塞线; 说明它是CP上升沿翻转的边沿触发器。 S =D R = D

具有异步输入端和多输入端的维持阻塞D触发器 Sp Rp & CP Q 2 D & 6 R

具有异步输入端和多输入端的维持阻塞D触发器

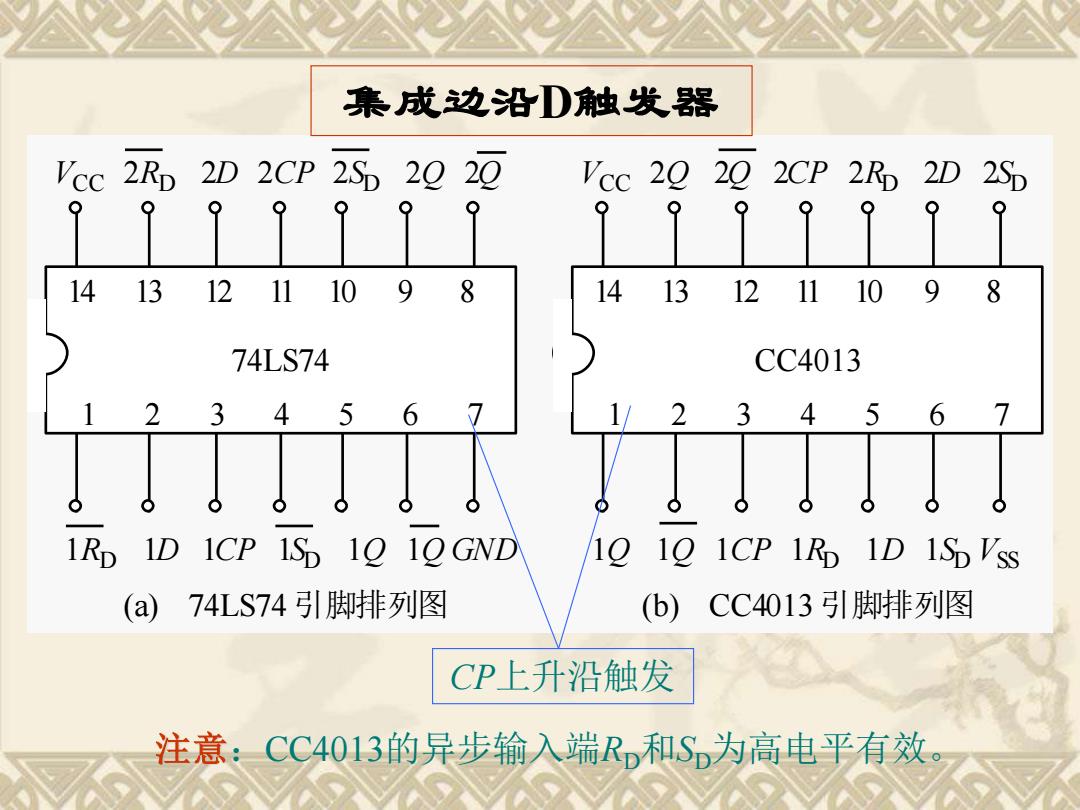

集成边沿D触发器 Vec 2Rp 2D 2CP 25)20 20 Vcc 2020 2CP 2Rp 2D 2Sp ● 1413 1211 1098 141312 1110 98 74LS74 CC4013 23456 7 1y23456 1D 1CP 1S 10 10GND 10 10 1CP 1R 1D 1Sp Vss (a) 74LS74引脚排列图 (b) CC4013引脚排列图 CP上升沿触发 注意:CC4013的异步输入端R,和Sp为高电平有效

14 13 12 11 10 9 8 74LS74 1 2 3 4 5 6 7 VCC 2RD 2D 2CP 2S D 2Q 2Q 1RD 1D 1CP 1S D 1Q 1Q GND 14 13 12 11 10 9 8 CC4013 1 2 3 4 5 6 7 VCC 2Q 2Q 2CP 2RD 2D 2S D 1Q 1Q 1CP 1RD 1D 1S D VSS (a) 74LS74引脚排列图 (b) CC4013引脚排列图 集成边沿D触发器 注意:CC4013的异步输入端RD和SD为高电平有效。 CP上升沿触发

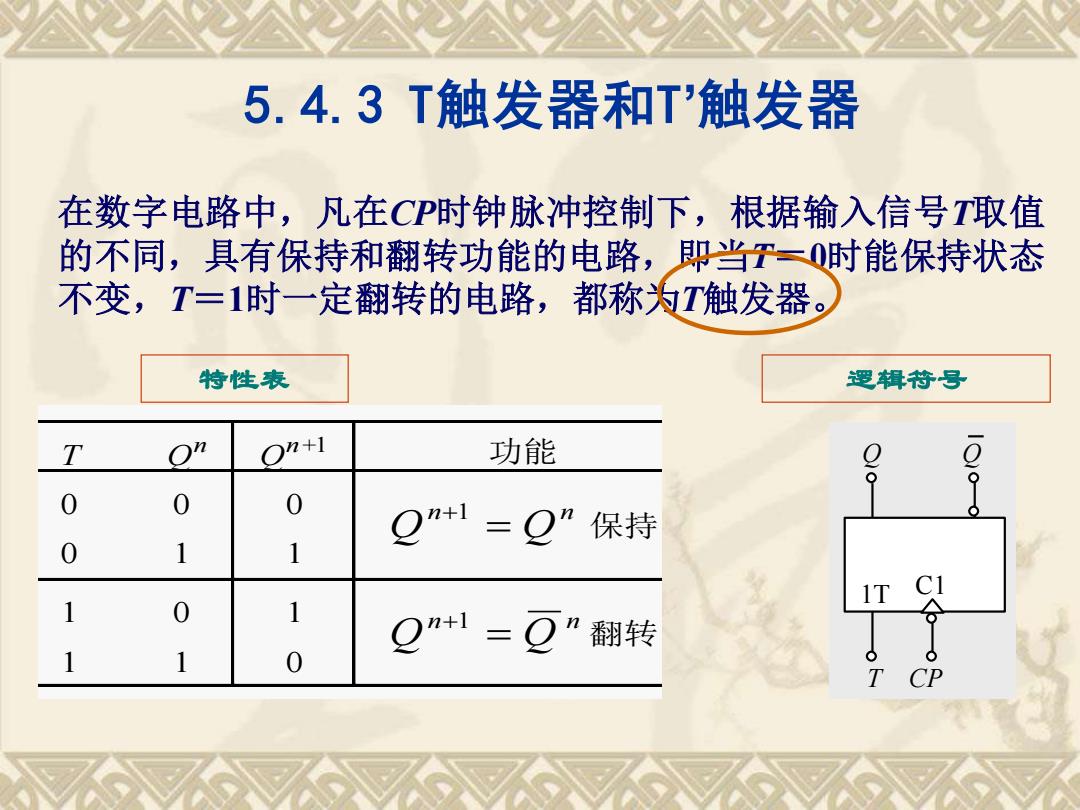

5.4.3T触发器和T触发器 在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值 的不同,具有保持和翻转功能的电路,即当T二Q时能保持状态 不变,T=1时一定翻转的电路,都称为T触发器 特性表 逻辑符号 On+1 功能 0 0 Q”+1=Q” 保持 1 1 0 Qn+1=Qn 翻转 1 0

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号T取值 的不同,具有保持和翻转功能的电路,即当T=0时能保持状态 不变,T=1时一定翻转的电路,都称为T触发器。 T Qn Q n +1 功能 0 0 0 1 0 1 n n Q = Q +1 保持 1 0 1 1 1 0 n n Q = Q +1 翻转 特性表 逻辑符号 T CP 1T Q Q C1 5.4.3 T触发器和T’触发器