第二讲Verilog HDL语言基础 西安邮电学院通信工程系 线网(Net)类型 由模块或门驱动的连线。 ~驱动端信号的改变会立刻 a 传递到输出的连线上。 sela 例:右图上,slb的改 nsl out 变,会自动地立刻影响或 门的输出。 ·如果没有驱动元件连接到线 sl 网,线网的缺省值为z net

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 线网(Net)类型 ❖ 由模块或门驱动的连线。 ❖ 驱动端信号的改变会立刻 传递到输出的连线上。 ❖ 例:右图上,selb的改 变,会自动地立刻影响或 门的输出。 ❖ 如果没有驱动元件连接到线 网,线网的缺省值为z a b sl selb sela nsl out net

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 线网类型信号的主要种类 。在为不同工艺的基本元件建立库模型的时候,常常需要用不同的连接类 型来与之对应,使其行为与实际器件一致。常见的有以下几种。 类型 功能 wire,tri 对应于标准的互连线(缺省) supply1,supply2 对应于电源线或接地线 wor, trior 对应于有多个驱动源的线或逻辑连接 wand, triand 对应于有多个驱动源的线与逻辑连接 trireg 对应于有电容存在能暂时存储电平的连接 tril,triO 对应于需要上拉或下拉的连接 冬线网类型说明语法为: net kind [msb:1sb] net1,net2,.·. netN; 例:wire start,do;/2个1位的连线信号 wand[2:0]addr;//一个3位的线与信号

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 线网类型信号的主要种类 ❖ 在为不同工艺的基本元件建立库模型的时候,常常需要用不同的连接类 型来与之对应,使其行为与实际器件一致。常见的有以下几种。 类型 功能 wire, tri 对应于标准的互连线(缺省) supply1, supply2 对应于电源线或接地线 wor, trior 对应于有多个驱动源的线或逻辑连接 wand, triand 对应于有多个驱动源的线与逻辑连接 trireg 对应于有电容存在能暂时存储电平的连接 tri1, tri0 对应于需要上拉或下拉的连接 ❖ 线网类型说明语法为: net_kind [msb:lsb] net1, net2, . . . , netN; 例:wire start,do; // 2个1位的连线信号 wand [2:0] addr; // 一个3位的线与信号

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 标量和向量线网 冬1位线网称标量线网,多位线网称向量线网。缺省说明为标量线网。 如果多个驱动源驱动一个wir(或三态线网),线网的有效值由下表 决定。 Wire (tri) 0 X 2 0 0 X 0 1 X X 0 1 x 在定义向量线网时可选用关键词scalared或vectored。.例: wire vectored[3:1]Grb;/不允许位选择Grb[2]和部分选择Grb[3:2] wor scalared[4:0]Best;/与wor[4:0]Best相同,允许位选择 /Best[2]和部分选择Best[3:1]

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 标量和向量线网 ❖ 1位线网称标量线网,多位线网称向量线网。缺省说明为标量线网。 ❖ 如果多个驱动源驱动一个wire(或三态线网),线网的有效值由下表 决定。 ❖ 在定义向量线网时可选用关键词scalared 或vectored。例: wire vectored[3:1] Grb;//不允许位选择Grb[2]和部分选择Grb [3:2] wor scalared [4:0] Best;//与wor[4:0] Best相同,允许位选择 //Best[2]和部分选择Best[3:1]。 Wire(tri) 0 1 x z 0 0 x x 0 1 x 1 x 1 x x x x x z 0 1 x z

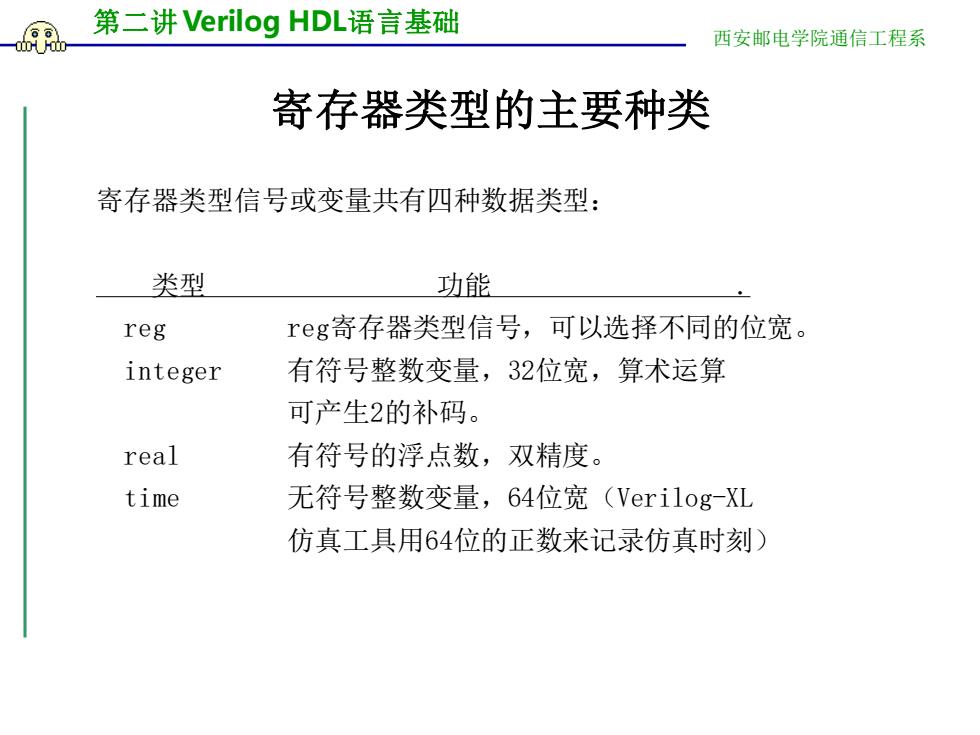

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 寄存器类型的主要种类 寄存器类型信号或变量共有四种数据类型: 类型 功能 reg reg寄存器类型信号,可以选择不同的位宽。 integer 有符号整数变量,32位宽,算术运算 可产生2的补码。 real 有符号的浮点数,双精度。 time 无符号整数变量,64位宽(Verilog-XL 仿真工具用64位的正数来记录仿真时刻)

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 寄存器类型的主要种类 寄存器类型信号或变量共有四种数据类型: 类型 功能 . reg reg寄存器类型信号,可以选择不同的位宽。 integer 有符号整数变量,32位宽,算术运算 可产生2的补码。 real 有符号的浮点数,双精度。 time 无符号整数变量,64位宽(Verilog-XL 仿真工具用64位的正数来记录仿真时刻)

第二讲Verilog HDL语言基础 西安邮电学院通信工程系 reg寄存器类型 ?reg类型使用保留字reg加以说明,主要用于描述信号,形式如下: reg [msb:Isb]regl,reg2,.reg N; 例:reg[3:0]Sat;/Sat为4位寄存器类型信号。 reg Cnt;//1位寄存器类型信号。 reg[1:32]Kisp,Pisp,Lisp;/3个32位寄存器类型信号 冬寄存器类型信号可以取任意长度,其值通常被解释为无符号数。 存储器是一个寄存器数组。存储器使用如下方式说明: reg[msb:Isb]meml[upper:lower],mem2[uppera2:lower习,.; 例:reg[3:0]MyMem[63:0];/MyMem为64个4位寄存器的数组。 reg Bog[5:1];//Bog为5个1位寄存器的数组。 存储器只能逐个赋值。如Bog[1]=1b1;Bog[2]=1b0:

第二讲 Verilog HDL语言基础 西安邮电学院通信工程系 reg寄存器类型 ❖ reg类型使用保留字reg加以说明,主要用于描述信号,形式如下: reg [msb:lsb] reg1, reg2, . . . reg N; 例:reg[3:0] Sat; //Sat为4位寄存器类型信号。 reg Cnt; //1位寄存器类型信号。 reg [1:32] Kisp, Pisp, Lisp;// 3个32位寄存器类型信号 ❖ 寄存器类型信号可以取任意长度,其值通常被解释为无符号数。 ❖ 存储器是一个寄存器数组。存储器使用如下方式说明: reg[msb:1sb] mem1 [upper1:lower1] ,mem2[upper2:lower2] ,. ; 例:reg [3:0] MyMem[63:0];// MyMem为64个4位寄存器的数组。 reg Bog[5:1]; // Bog为5个1位寄存器的数组。 ❖ 存储器只能逐个赋值。如 Bog[1]=1’b1; Bog[2]=1’b0;