电子科枚大学 软件技术基础 1.2计算机系统的构成及工作原理 主讲教师:刘民岷 航空航天学院 软件技术基础课程组 2019年5月

软件技术基础 1.2 计算机系统的构成及工作原理 主讲教师:刘民岷 航空航天学院 软件技术基础课程组 2019年5月

硬件系统+软件系统 应用软件 用户接口 编译器 汇编器数据库管理系统 系统软件 操作系统 设备驱动程序W®b浏览器中断服务程序 系统调用接口 软件 硬件 异常事件处理机构 硬件向上提供的接口 硬件系统 ·指令系统 控制器CPU高速缓存RAM ·异常事件 I/O子系统 通信子系统 ·端口定义 I/O和通信接口 硬件设备 I/O设备通信设备 电子科技大学刘民岷 计算机系统的构成 2

电子科技大学 刘民岷 2 硬件系统+软件系统 计算机系统的构成 硬件向上提供的接口 • 指令系统 • 异常事件 • 端口定义

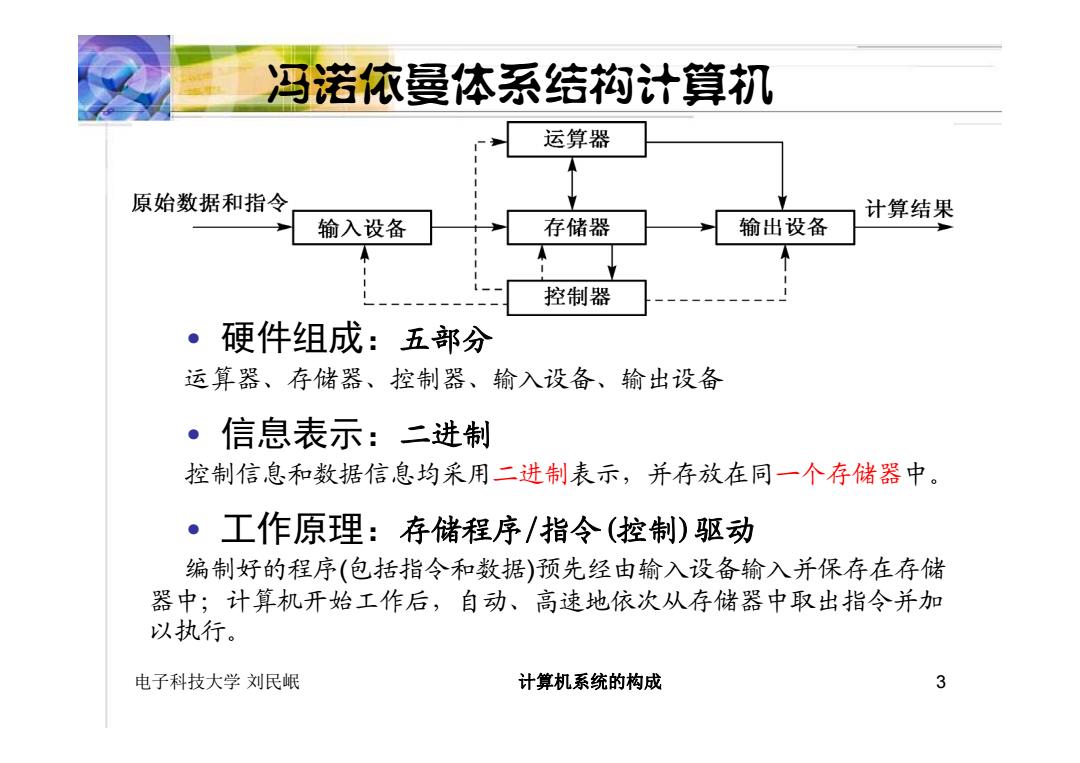

冯诺依曼体系结构计算机 运算器 原始数据和指令 计算结果 输入设备 存储器 输出设备 控制器 ·硬件组成:五部分 运算器、存储器、控制器、输入设备、输出设备 。信息表示:二进制 控制信息和数据信息均采用二进制表示,并存放在同一个存储器中。 。工作原理:存储程序/指令(控制)驱动 编制好的程序(包括指令和数据)预先经由输入设备输入并保存在存储 器中;计算机开始工作后,自动、高速地依次从存储器中取出指令并加 以执行。 电子科技大学刘民岷 计算机系统的构成 3

电子科技大学 刘民岷 3 冯诺依曼体系结构计算机 计算机系统的构成 • 硬件组成:五部分 运算器、存储器、控制器、输入设备、输出设备 • 信息表示:二进制 控制信息和数据信息均采用二进制表示,并存放在同一个存储器中。 • 工作原理:存储程序/指令(控制)驱动 编制好的程序(包括指令和数据)预先经由输入设备输入并保存在存储 器中;计算机开始工作后,自动、高速地依次从存储器中取出指令并加 以执行

内存结构 地址 内容 位7 位0 00 存储单元 01 02 来自CPU的 地址信号 地址寄存器 地址译码器 数据缓冲器 送至CPU 的数据总线 2-2 2P_ 来自CPU的 控制 控制信号 电路 》主存储器由许多字节单元组成,每个单元都有一个唯一的编号(存储单 元地址),称为该单元的地址 >访问(读或写)存储单元:CPU发送的地址信号经地址译码后产生相应的 选通信号选中目标单元,在控制信号的作用下对目标单元进行读写 电子科技大学刘民岷 计算机系统的构成 4

电子科技大学 刘民岷 4 内存结构 计算机系统的构成 主存储器由许多字节单元组成,每个单元都有一个唯一的编号(存储单 元地址),称为该单元的地址 访问(读或写)存储单元 :CPU发送的地址信号经地址译码后产生相应的 选通信号选中目标单元,在控制信号的作用下对目标单元进行读写

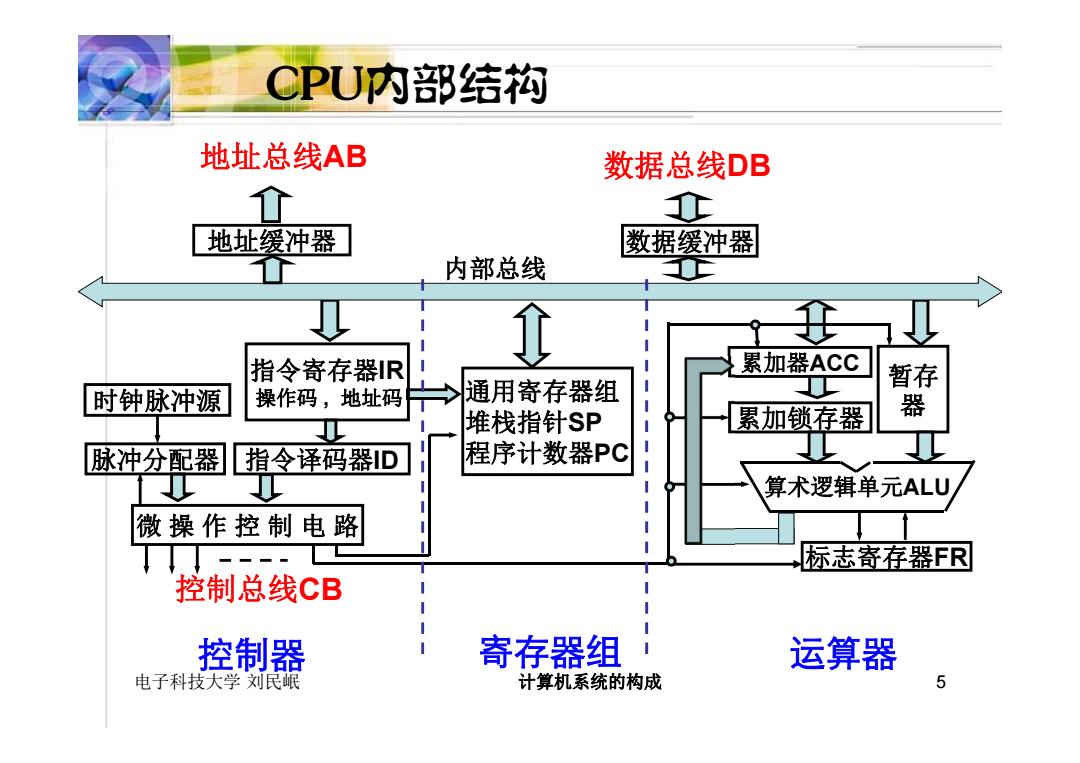

CPU内部结构 地址总线AB 数据总线DB 个 0 地址缓冲器 数据缓冲器 内部总线 指令寄存器IR 累加器ACC 暂存 时钟脉冲源 操作码,地址码 → 通用寄存器组 工 堆栈指针SP 累加锁存器 器 脉冲分配器 指令译码器D 程序计数器PC 算术逻辑单元ALU 微操作控制电路 标志寄存器FR 控制总线CB 控制器 寄存器组 1 运算器 电子科技大学刘民岷 计算机系统的构成 5

电子科技大学 刘民岷 5 CPU内部结构 计算机系统的构成 算术逻辑单元ALU 累加器ACC 累加锁存器 暂存 器 标志寄存器FR 通用寄存器组 堆栈指针SP 程序计数器PC 微操作控制电路 指令译码器ID 指令寄存器IR 操作码 , 地址码 脉冲分配器 时钟脉冲源 控制总线CB 地址总线AB 数据总线DB 内部总线 地址缓冲器 数据缓冲器 控制器 寄存器组 运算器