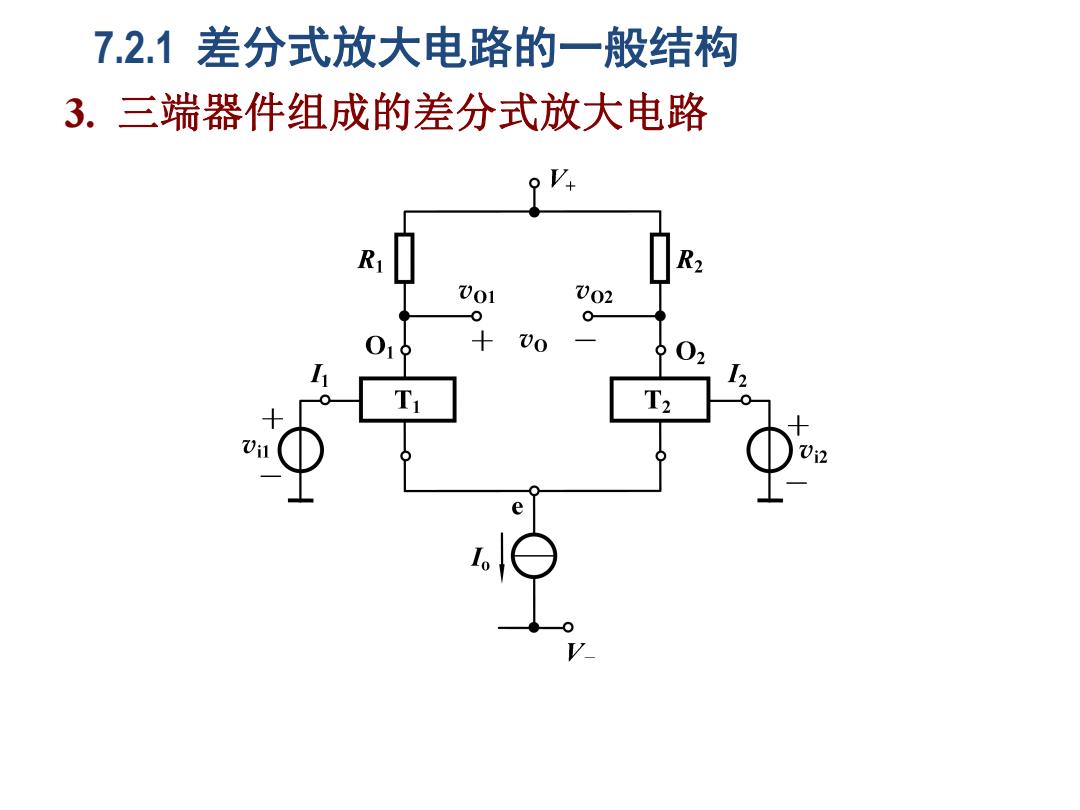

7.2.1差分式放大电路的一般结构 3.三端器件组成的差分式放大电路 V+ R2 001 002 0 019 00 T T2 02 e

7.2.1 差分式放大电路的一般结构 3. 三端器件组成的差分式放大电路

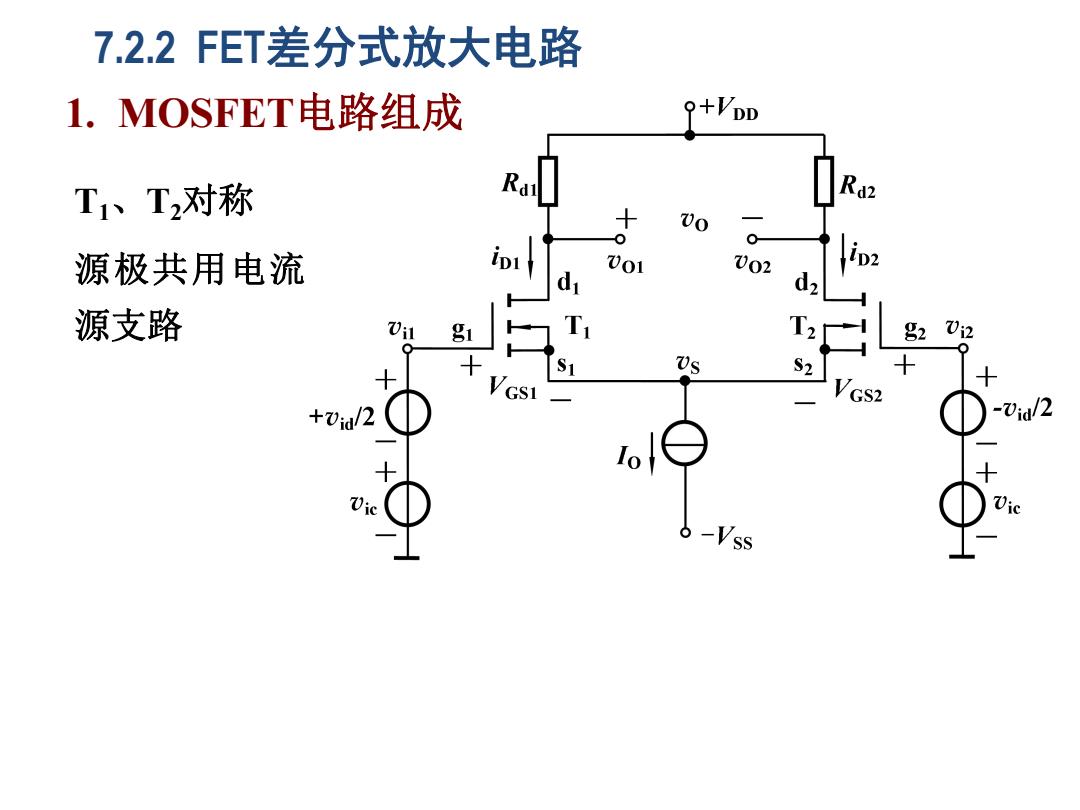

7.2.2FET差分式放大电路 1.MOSFET电路组成 +VDD T1、T2对称 00 源极共用电流 001 002 ip2 d d2 源支路 01 gi T T2 012 S1 s S2 VGSI +Via/2 -id/2 0 -Vss

7.2.2 FET差分式放大电路 1. MOSFET电路组成 T1、T2对称 源极共用电流 源支路

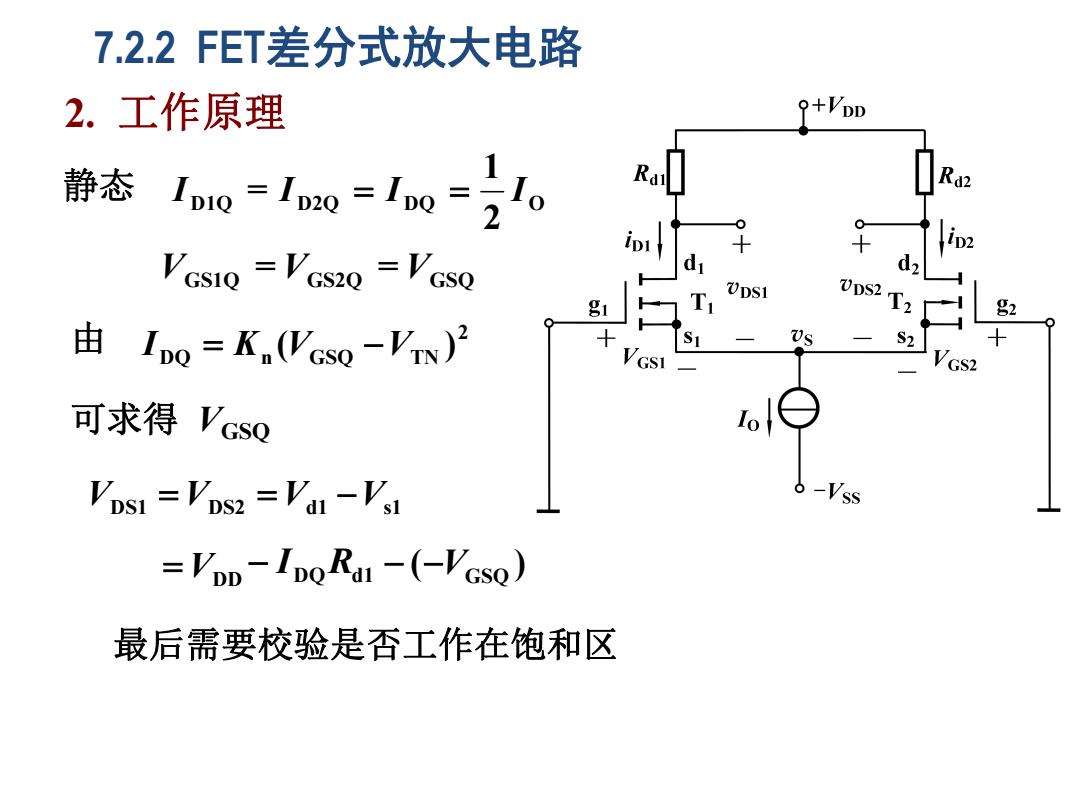

7.2.2FET差分式放大电路 2.工作原理 +VDD 静态 Iong-1oo=100 Rd2 ip2 VGSIQ VGS2O =VGSQ d2 T T2 由Ipo=Kn(Wcso-VN)2 S1 S2 VGS2 可求得 VGSQ VDSI VDS2 =Vat -Vs -Vss =Von-IDo Rai-(-Vcso)) 最后需要校验是否工作在饱和区

7.2.2 FET差分式放大电路 静态 D1Q D2Q DQ O 2 1 I = I I I VGS1Q = VGS2Q = VGSQ VDD DQ Rd1 I ( ) VGSQ 2 DQ n GSQ TN I K (V V ) 2. 工作原理 VDS1 VDS2 Vd1 Vs1 由 可求得 VGSQ 最后需要校验是否工作在饱和区

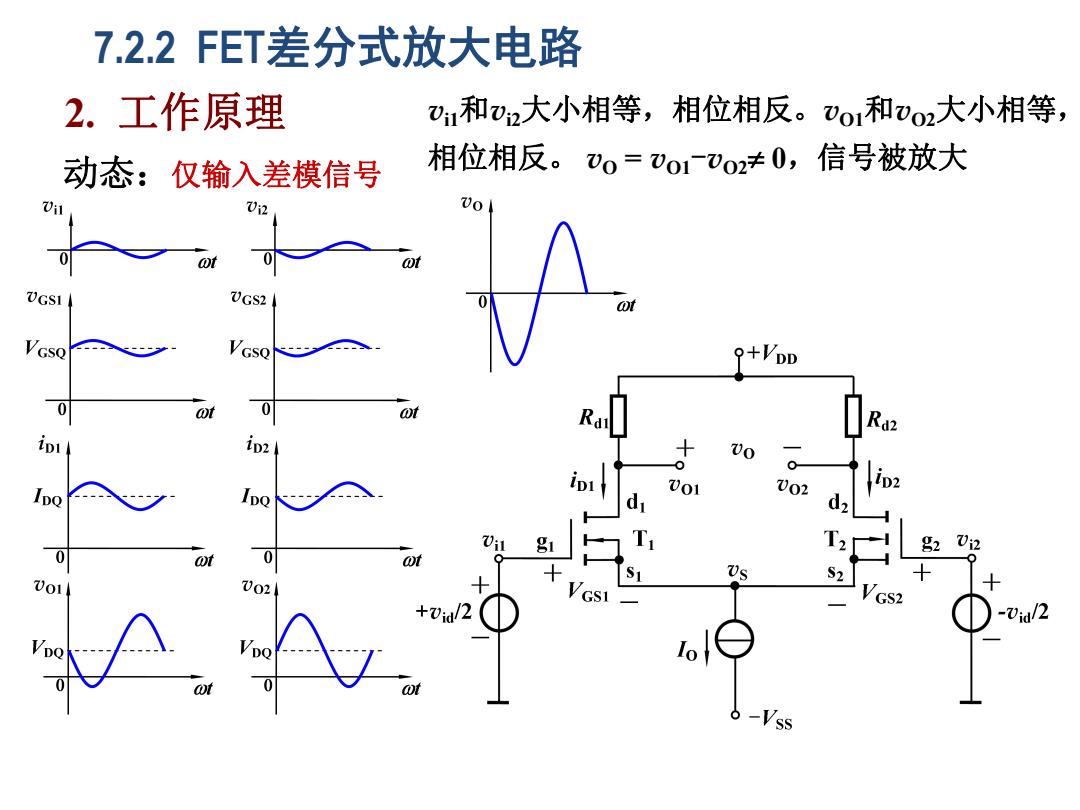

7.2.2FET差分式放大电路 2.工作原理 v1和v2大小相等,相位相反。vo1和vo2大小相等, 动态:仅输入差模信号 相位相反。v0=℃o1v02≠0,信号被放大 0i1 02 00 @i OGSI GSO +VDD 00 D2 Ipo 001 d 002 d2 g2V2 0 S2 002 GS2 +Via/2 Via/2 wt -Vss

7.2.2 FET差分式放大电路 vi1和vi2大小相等,相位相反。vO1和vO2大小相等, 相位相反。 vO = vO1-vO2 0,信号被放大 2. 工作原理 动态:仅输入差模信号

7.2.2FET差分式放大电路 2.工作原理 1和x2大小相等,相位相同。vo1和vo2大小相等, 动态:仅输入共模信号 相位相同。vo=vo1vo20,双端无信号输出 0i1 012 00 实际上单端输出时也有很 强的共模信号抑制能力 OGSI UGS2 0 at GSO VGSQ +VDD at ip2 00 001 002 D2 d T 02 at Us S2 002 GS2 o 71 wt o-Vss

7.2.2 FET差分式放大电路 vi1和vi2大小相等,相位相同。vO1和vO2大小相等, 相位相同。 vO = vO1-vO2= 0,双端无信号输出 2. 工作原理 动态:仅输入共模信号 实际上单端输出时也有很 强的共模信号抑制能力