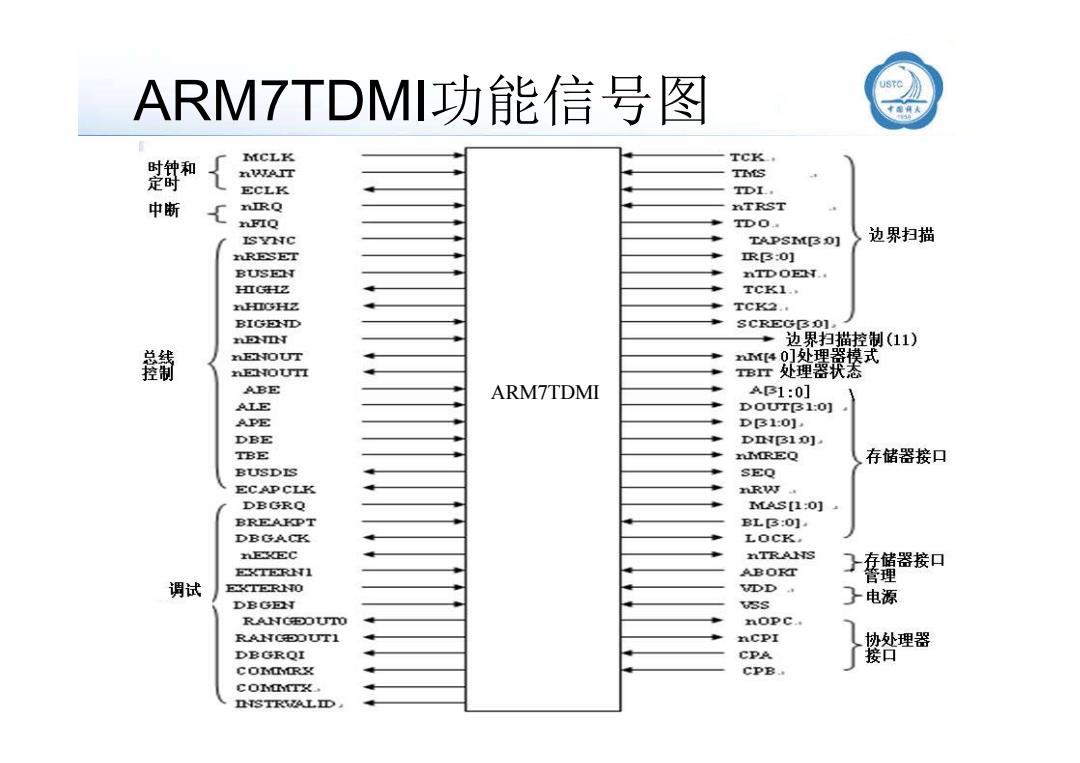

ARM7TDMI功能信号图 USTC MCLK 截和 TCK. nWAIT TIS ECLK TDI. 中断 nIRQ nTRST nFIQ T①DO. ISVNC TAPSMBO] 边界扫描 nRESET RE:0] BUSEN nTDOEN.. HⅡC狂HZ TCKI.. n正HZ TCK2.. BIGEND SCREGBo1. nEIDT 边界扫描控制(11) nENOUT 40]处理器模式 nDm0UIΠ 江处理溶状卷 ABE ARM7TDMI AB1:0] ALE DOUTB1:0] APE DB1:0]. DBE DIB10]. TBE nnREQ 存储器接口 BUSDIS SEO ECAPCLK nRW DBGRO DAS[1:0] BREAKPT BLB:0]. DBGACK LOC华 nEKEC nTRANS EKTER上T1 ABORT 奢敏器按口 调试 EXTERNO VDD DBGENT VSS 了电源 RANGEOUTO nOPC.. RANGEOUTI nCPI 协处理器 DBGRQI CPA 接行 CONMRX CPB.. CONr. DISTRVALID

ARM7TDMI功能信号图 ARM7TDMI llxx@ustc.edu.cn 21/111

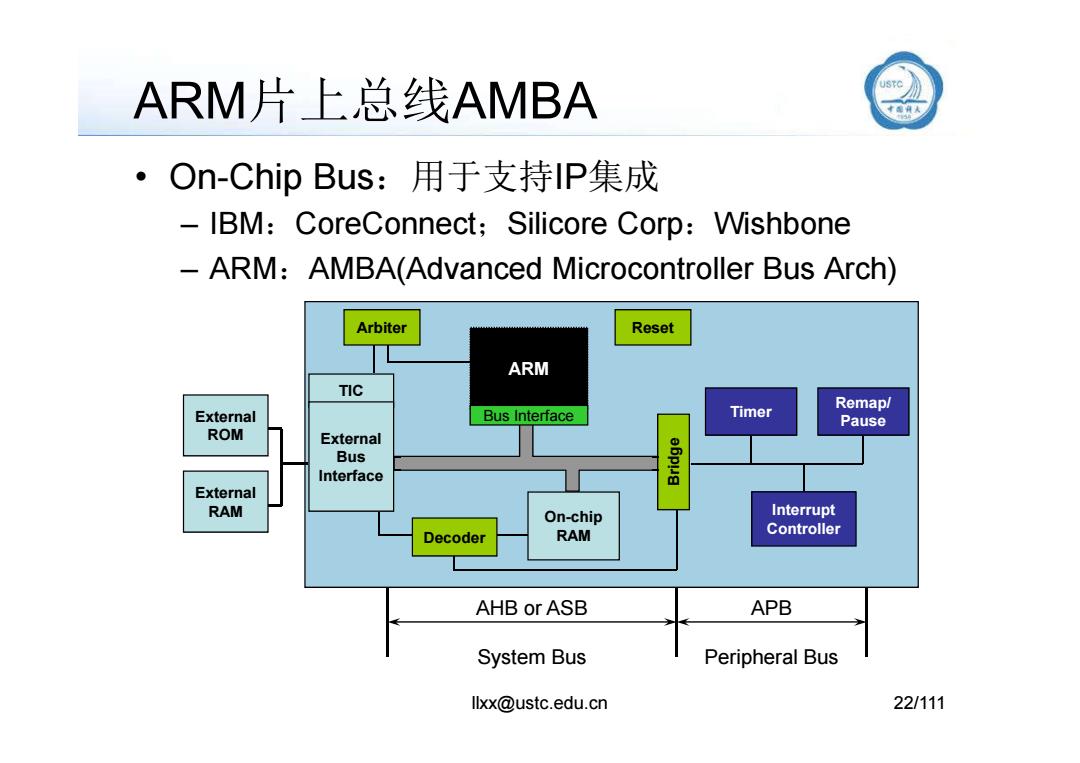

ARM片上总线AMBA On-Chip Bus:用于支持P集成 -IBM:CoreConnect;Silicore Corp:Wishbone -ARM:AMBA(Advanced Microcontroller Bus Arch) Arbiter Reset ARM TIC Remap/ External Bus Interface Timer Pause ROM External Bus Interface External RAM On-chip Interrupt Decoder RAM Controller AHB or ASB APB System Bus Peripheral Bus llxx@ustc.edu.cn 22/111

ARM片上总线AMBA • On-Chip Bus:用于支持IP集成 – IBM:CoreConnect;Silicore Corp:Wishbone – ARM:AMBA(Advanced Microcontroller Bus Arch) ARM Arbiter Reset llxx@ustc.edu.cn 22/111 Bridge Timer On-chip RAM Interrupt Controller Remap/ Pause TIC External Bus Interface ROM External RAM System Bus Peripheral Bus AHB or ASB APB External Bus Interface Decoder

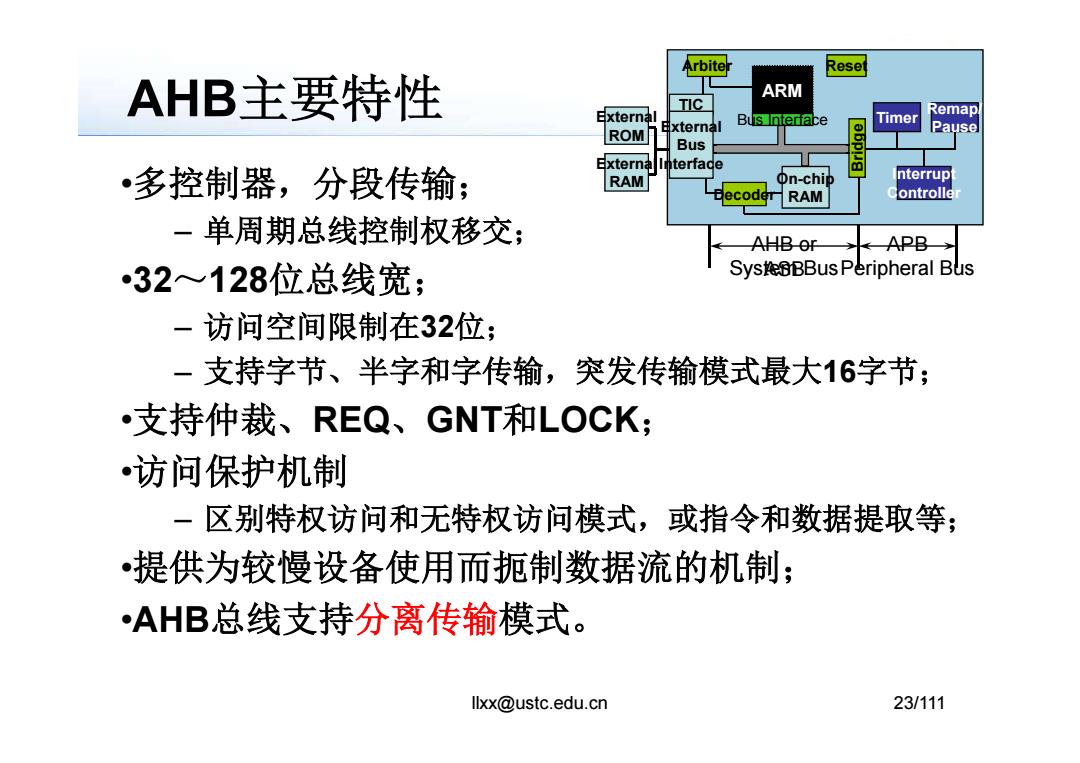

Arbiter Reset AHB主要特性 ARM TIC External Remap 田xterna Bus Interface Timer ROM Pause Bus 日xterna 多控制器,分段传输; RAM Φn-chip nterrup RAM Controlle 一单周期总线控制权移交; AHB or APB 32128位总线宽; SysteBBus Peripheral Bus -访问空间限制在32位; -支持字节、半字和字传输,突发传输模式最大16字节: 支持仲裁、REQ、GNT和LOCK; 访问保护机制 一区别特权访问和无特权访问模式,或指令和数据提取等; •提供为较慢设备使用而扼制数据流的机制; AHB总线支持分离传输模式。 llxx@ustc.edu.cn 23/111

AHB主要特性 •多控制器,分段传输; – 单周期总线控制权移交; •32~128位总线宽; – 访问空间限制在32位; – 支持字节、半字和字传输,突发传输模式最大16字节; Bridge Timer On-chip RAM ARM Interrupt Controller Remap/ Pause TIC Arbiter External Bus Interface ROM External RAM Reset System BusPeripheral Bus AHB or ASB APB External Bus Interface Decoder llxx@ustc.edu.cn 23/111 – 支持字节、半字和字传输,突发传输模式最大16字节; •支持仲裁、REQ、GNT和LOCK; •访问保护机制 – 区别特权访问和无特权访问模式,或指令和数据提取等; •提供为较慢设备使用而扼制数据流的机制; •AHB总线支持分离传输模式

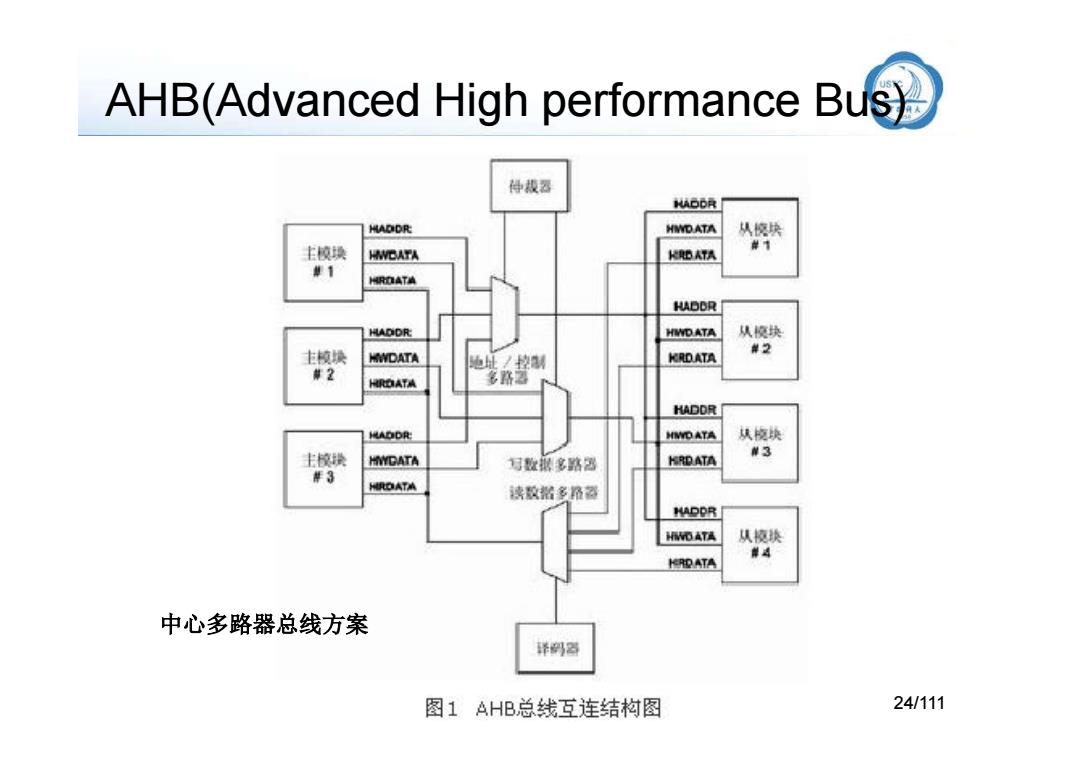

AHB(Advanced High performance e Bus) 仲裁器 HADDR HADIDR HIWDATA 从使块 #1 主校换 HCATA 长BATA "1 HROATA HADDR HADDR: HWD ATA 从模块 主核焕 HWDATA KRDATA #2 地址/控制 前2 HRDATA 多路器 HADDR 线AODR HMD ATA 从棱块 主核块 N3 HWDATA 写数据多路昌 HRDATA 禁3 HRDATA 读胶鲨多路酒 HADDR HWOATA 从棱块 #4 长OATA 中心多路器总线方案 译鸟图 图1AHB总线互连结构图 24/111

AHB(Advanced High performance Bus) llxx@ustc.edu.cn 24/111 中心多路器总线方案

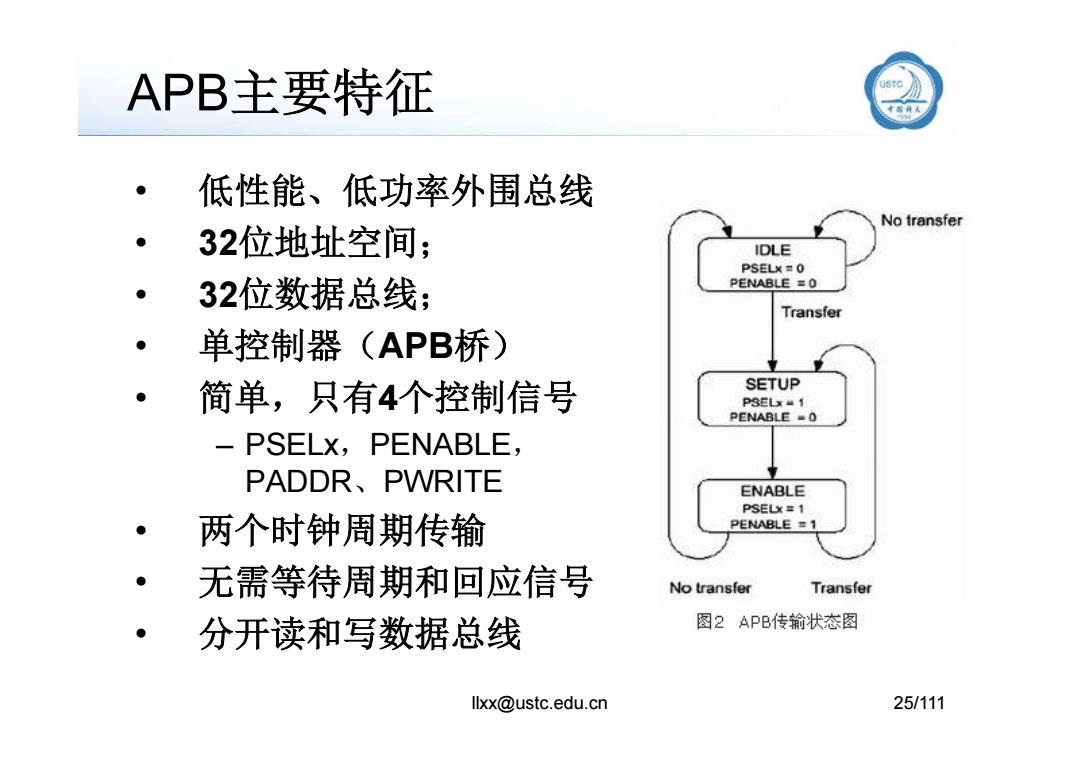

APB主要特征 低性能、低功率外围总线 No transfer ● 32位地址空间; IDLE PSELx=0 PENABLE =0 ● 32位数据总线; Transfer 单控制器(APB桥) 简单,只有4个控制信号 SETUP PSELx1 PENABLE 0 PSELX,PENABLE, PADDR、PWRITE ENABLE PSELx=1 ● 两个时钟周期传输 PENABLE =1 ● 无需等待周期和回应信号 No transfer Transfer 分开读和写数据总线 图2APB传输状态图 llxx@ustc.edu.cn 25/111

APB主要特征 • 低性能、低功率外围总线 • 32位地址空间; • 32位数据总线; • 单控制器(APB桥) • 简单,只有4个控制信号 llxx@ustc.edu.cn 25/111 • 简单,只有4个控制信号 – PSELx,PENABLE, PADDR、PWRITE • 两个时钟周期传输 • 无需等待周期和回应信号 • 分开读和写数据总线