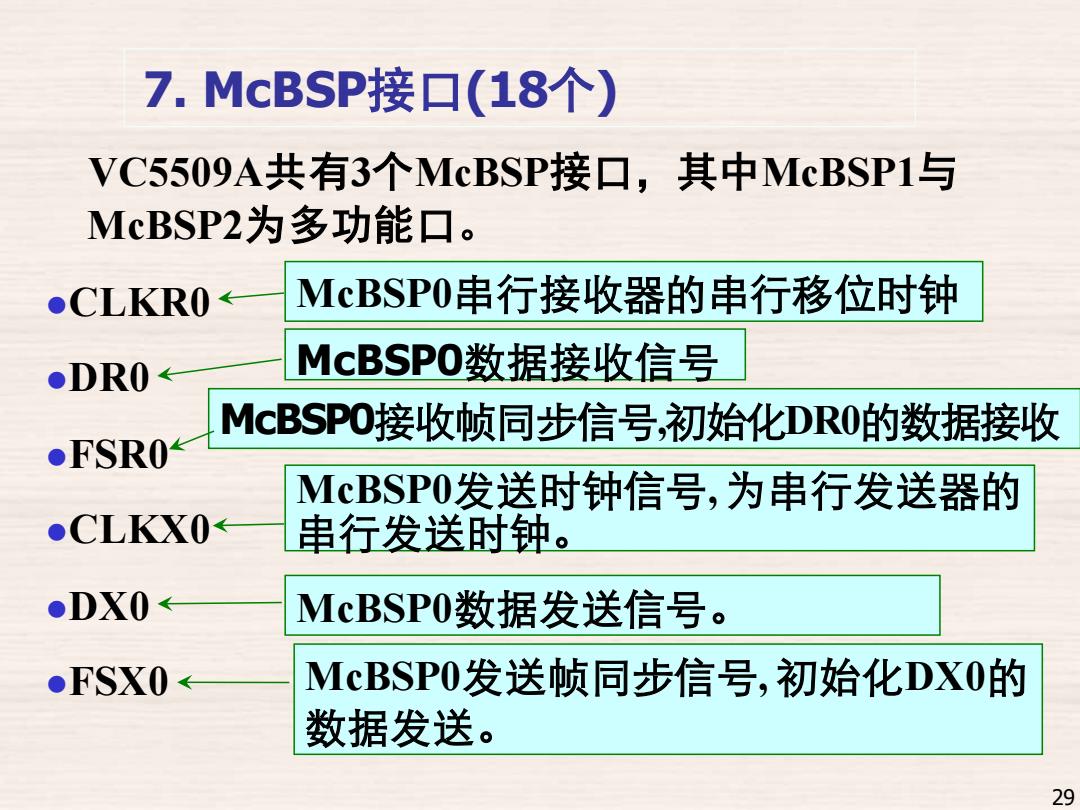

7.McBSP接▣(18个) VC5509A共有3个McBSP接口,其中McBSP1与 McBSP2为多功能口。 CLKRO McBSPO串行接收器的串行移位时钟 DRO McBSPO数据接收信号 McBSPO:接收帧同步信号,初始化DR0的数据接收 McBSP0发送时钟信号,为串行发送器的 CLKX0- 串行发送时钟。 DXO McBSP0数据发送信号。 ●FSX0 McBSPO发送帧同步信号,初始化DX0的 数据发送 。 29

VC5509A共有3个McBSP接口,其中McBSP1与 McBSP2为多功能口。 ⚫CLKR0 ⚫DR0 ⚫FSR0 ⚫CLKX0 ⚫DX0 ⚫FSX0 7. McBSP接口(18个) McBSP0串行接收器的串行移位时钟 McBSP0数据接收信号 McBSP0接收帧同步信号,初始化DR0的数据接收 McBSP0发送时钟信号, 为串行发送器的 串行发送时钟。 McBSP0数据发送信号。 McBSP0发送帧同步信号, 初始化DX0的 数据发送。 29

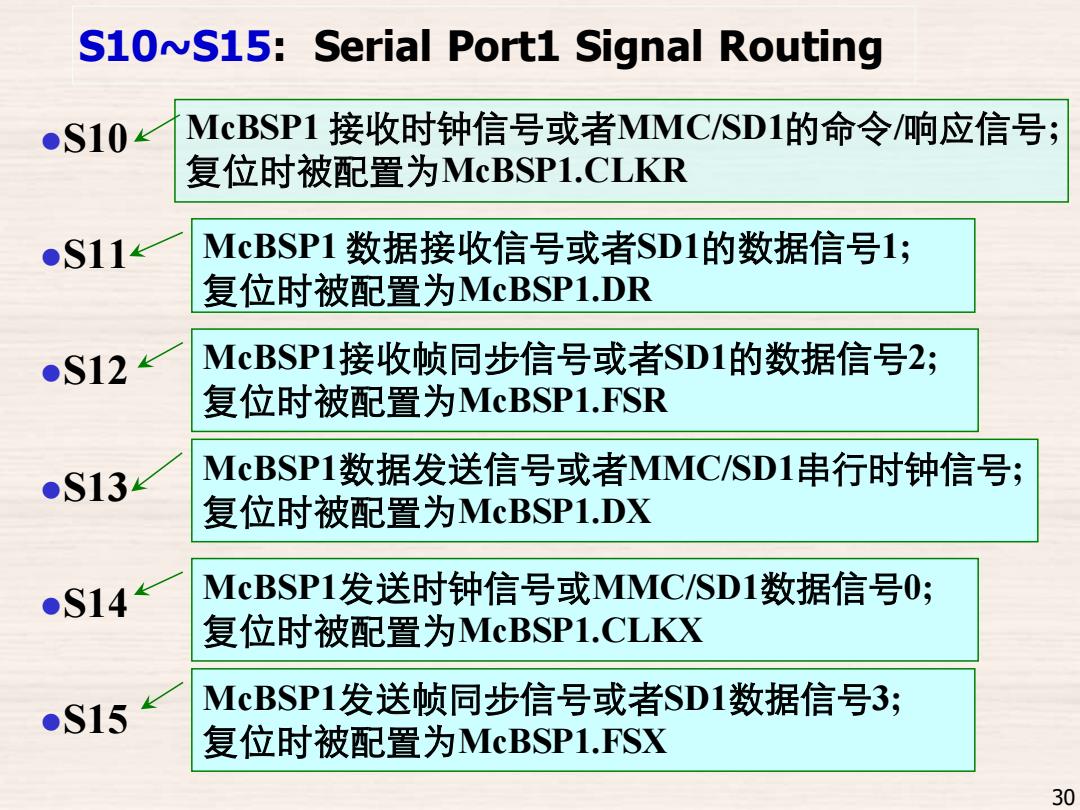

S10~S15:Serial Port1 Signal Routing ●S10k McBSP1接收时钟信号或者MMC/SD1的命令响应信号; 复位时被配置为McBSP1.CLKR ●S11k McBSP1数据接收信号或者SD1的数据信号1; 复位时被配置为McBSP1.DR ●S12 McBSP1接收帧同步信号或者SD1的数据信号2; 复位时被配置为McBSP1.FSR ●S134 McBSP1数据发送信号或者MMC/SD1串行时钟信号; 复位时被配置为MeBSP1.DX ●S14 McBSP1发送时钟信号或MMC/SD1数据信号O; 复位时被配置为McBSP1.CLKX ●S15 McBSP1发送帧同步信号或者SD1数据信号3; 复位时被配置为McBSP1.FSX 30

⚫S10 ⚫S11 ⚫S12 ⚫S13 ⚫S14 ⚫S15 McBSP1 接收时钟信号或者MMC/SD1的命令/响应信号; 复位时被配置为McBSP1.CLKR McBSP1 数据接收信号或者SD1的数据信号1; 复位时被配置为McBSP1.DR McBSP1接收帧同步信号或者SD1的数据信号2; 复位时被配置为McBSP1.FSR McBSP1数据发送信号或者MMC/SD1串行时钟信号; 复位时被配置为McBSP1.DX McBSP1发送时钟信号或MMC/SD1数据信号0; 复位时被配置为McBSP1.CLKX McBSP1发送帧同步信号或者SD1数据信号3; 复位时被配置为McBSP1.FSX 30 S10~S15: Serial Port1 Signal Routing

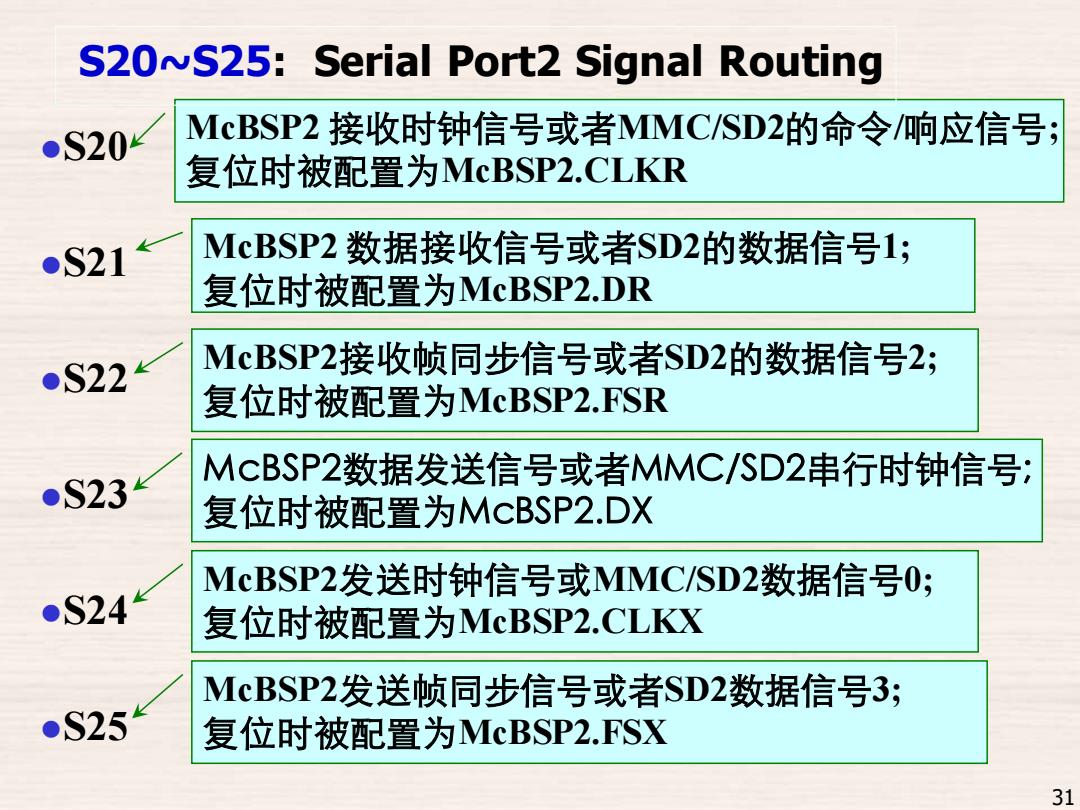

S20~S25:Serial Port2 Signal Routing ●S204 McBSP:2接收时钟信号或者MMC/SD2的命令/响应信号 复位时被配置为McBSP2.CLKR ●S21 McBSP2数据接收信号或者SD2的数据信号1; 复位时被配置为McBSP2.DR ●S22 McBSP2接收帧同步信号或者SD2的数据信号2; 复位时被配置为McBSP2.FSR McBSP2数据发送信号或者MMC/SD2串行时钟信号; ●S23 复位时被配置为McBSP2.DX McBSP2发送时钟信号或MMC/SD2数据信号0; ●S24 复位时被配置为McBSP2.CLKX McBSP2发送帧同步信号或者SD2数据信号3; 0S25 复位时被配置为McBSP2.FSX 31

⚫S20 ⚫S21 ⚫S22 ⚫S23 ⚫S24 ⚫S25 McBSP2 接收时钟信号或者MMC/SD2的命令/响应信号; 复位时被配置为McBSP2.CLKR McBSP2 数据接收信号或者SD2的数据信号1; 复位时被配置为McBSP2.DR McBSP2接收帧同步信号或者SD2的数据信号2; 复位时被配置为McBSP2.FSR McBSP2数据发送信号或者MMC/SD2串行时钟信号; 复位时被配置为McBSP2.DX McBSP2发送时钟信号或MMC/SD2数据信号0; 复位时被配置为McBSP2.CLKX McBSP2发送帧同步信号或者SD2数据信号3; 复位时被配置为McBSP2.FSX 31 S20~S25: Serial Port2 Signal Routing

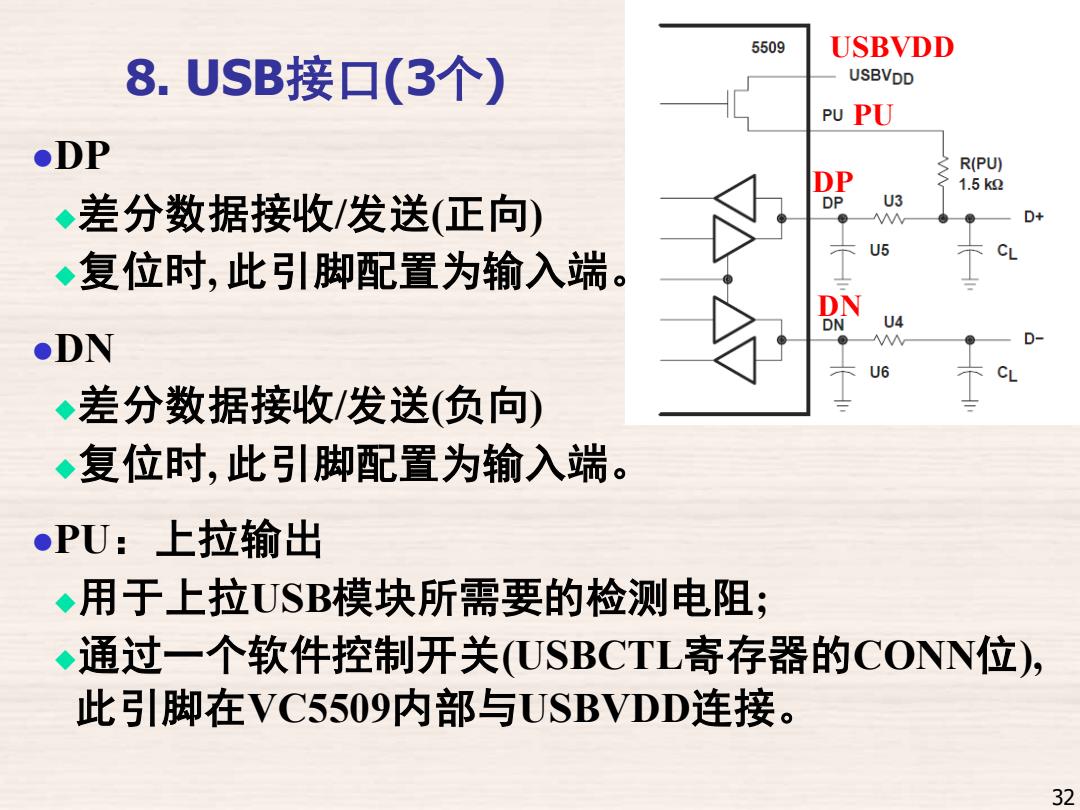

5509 USBVDD 8.USB接▣(3个) UsBVDD PU PU DP R(PU) 1.5kQ ◆差分数据接收/发送(正向) U3 N D+ 05 ◆复位时,此引脚配置为输入端。 CL DN U4 .DN U6 CL ◆差分数据接收/发送(负向) ◆复位时,此引脚配置为输入端。 PU:上拉输出 ◆用于上拉USB模块所需要的检测电阻; ◆通过一个软件控制开关(USBCTL寄存器的CONN位), 此引脚在VC5509内部与USBVDD连接。 32

8. USB接口(3个) ⚫DP ◆差分数据接收/发送(正向) ◆复位时, 此引脚配置为输入端。 ⚫DN ◆差分数据接收/发送(负向) ◆复位时, 此引脚配置为输入端。 ⚫PU:上拉输出 ◆用于上拉USB模块所需要的检测电阻; ◆通过一个软件控制开关(USBCTL寄存器的CONN位), 此引脚在VC5509内部与USBVDD连接。 DP DN PU USBVDD 32

9.A/D接口(2个) 。AIN0:模拟输入通道0 。AN1:模拟输入通道1 女注意: VC5509APGE有2个10位A/D接口; VC5509ABGA有4个10位A/D接口. 33

9. A/D接口(2个) ⚫ AIN0:模拟输入通道0 ⚫ AIN1:模拟输入通道1 ☼ 注意: VC5509A PGE有2个 10位 A/D 接口; VC5509A BGA有4个 10位 A/D 接口. 33