Polling(轮询方式) o Basic handshaking notion for writing output Host repeatedly reads the busy bit until it is 0 Host sets write bit in command register and writes a byte into data-out register Host sets command-ready bit When controller notices command-ready bit,it sets busy bit Controller gets write command and data,and works Controller clears command-ready bit,error bit and busy bit o Step1:Busy-wait cycle to wait for 1/O from device =busy-waiting=polling ”口”10:注1色,2Q0 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,20199/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Polling (轮询方式) Basic handshaking notion for writing output 1 Host repeatedly reads the busy bit until it is 0 2 Host sets write bit in command register and writes a byte into data-out register 3 Host sets command-ready bit 4 When controller notices command-ready bit, it sets busy bit 5 Controller gets write command and data, and works 6 Controller clears command-ready bit, error bit and busy bit Step1: Busy-wait cycle to wait for I/O from device ≡busy-waiting≡polling 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 9 / 54

Outline I/O Hardware and I/O control methods Polling(轮询方式 o Interrupts(中断方式) Direct Memory Access(DMA方式) o 1/O hardware summary 口18走卡11月00 陈香兰xlanchen@ustc.edu:cn http:/staf.u01174oi:Operating System操作系统原理斐 May22,201910/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Outline 1 I/O Hardware and I/O control methods Polling (轮询方式) Interrupts (中断方式) Direct Memory Access (DMA方式) I/O hardware summary 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 10 / 54

Interrupts(中断方式) o CPU Interrupt-request line triggered by I/O device o Interrupt handler receives interrupts o Basic interrupt scheme ~Raise→Catch→Dispatch→Clear 8259 CPU oS master Devices 8259 slave 口1回年走1,2月Q0 东香兰xlanchen@ustc,edu.cn http:/staff..u011740i:Operating System操作系统原理 May22,201911/54

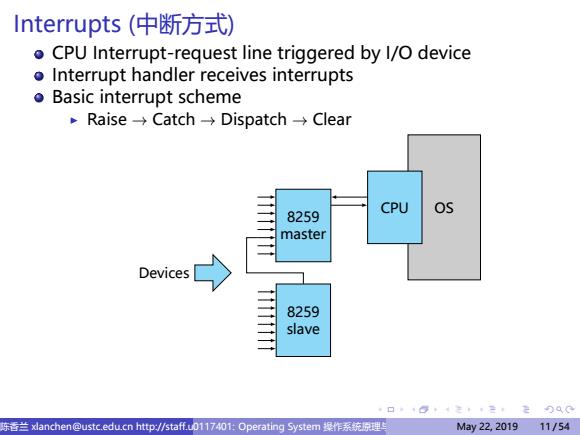

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Interrupts (中断方式) CPU Interrupt-request line triggered by I/O device Interrupt handler receives interrupts Basic interrupt scheme ▶ Raise → Catch → Dispatch → Clear CPU OS 8259 master 8259 slave Devices 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 11 / 54

Interrupts(中断方式) CPU 1/O controller 1 device driver initiates 1/O initiates l/O CPU executing checks for interrupts between instructions 3 CPU receiving interrupt, input ready,output transfers control to complete,or error interrupt handler generates interrupt signal interrupt handler processes data, returns from interrupt CPU resumes processing of interrupted task Figure:Interrupt-Driven I/O Cycle 陈香兰xlanchen@ustc.edu.cn http:/taf.u0117401:Operating System操作系统原理 May22,201911/54

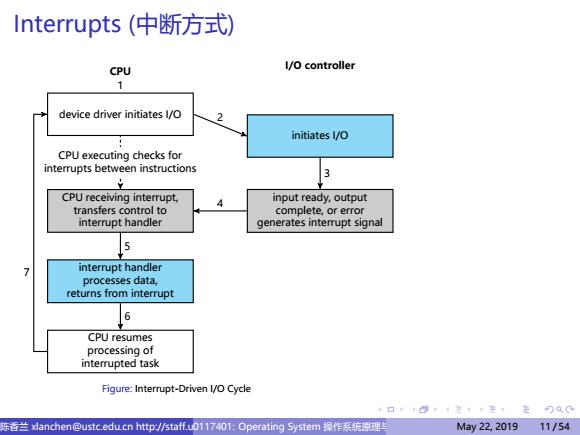

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Interrupts (中断方式) device driver initiates I/O CPU 1 CPU receiving interrupt, transfers control to interrupt handler CPU executing checks for interrupts between instructions interrupt handler processes data, returns from interrupt 5 CPU resumes processing of interrupted task 6 7 initiates I/O I/O controller 2 input ready, output complete, or error generates interrupt signal 3 4 Figure: Interrupt-Driven I/O Cycle 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 11 / 54

Interrupts(中断方式) o More sophisticated interrupt-handling features: Most CPU have two interrupt request lines Nonmaskable Maskable to ignore or delay some interrupts o Efficient dispatching without polling the devices Interrupt vector:to dispatch interrupt to correct handler Interrupt chaining:to allow more device more interrupt handlers oDistinguish between high-and low-priority interrupts: Interrupt priority:the handling of low-priority interrupts is deferred without masking,even preempted. o Interrupt mechanism also used for exceptions 口⊙生年12月00 陈话兰xlanchen@ustc.edu.cn http/staff.u0117401 Operating System操作系统原理斐 May22,201911/54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Interrupts (中断方式) More sophisticated interrupt-handling features: Most CPU have two interrupt request lines. 1 Nonmaskable 2 Maskable to ignore or delay some interrupts Efficient dispatching without polling the devices ▶ Interrupt vector: to dispatch interrupt to correct handler ▶ Interrupt chaining: to allow more device & more interrupt handlers Distinguish between high- and low-priority interrupts: ▶ Interrupt priority: the handling of low-priority interrupts is deferred without masking, even preempted. Interrupt mechanism also used for exceptions 陈香兰 xlanchen@ustc.edu.cn http://staff.ustc.edu.cn/~xlanchen (Computer Application Laboratory, CS, USTC @ Hefei Embedded System Laboratory, CS, USTC @ Suzhou) 0117401: Operating System 操作系统原理与设计 May 22, 2019 11 / 54